Building time-surfaces by exploiting the complex volatility of an ECRAM memristor

2201.12673

0

0

🔍

Abstract

Memristors have emerged as a promising technology for efficient neuromorphic architectures owing to their ability to act as programmable synapses, combining processing and memory into a single device. Although they are most commonly used for static encoding of synaptic weights, recent work has begun to investigate the use of their dynamical properties, such as Short Term Plasticity (STP), to integrate events over time in event-based architectures. However, we are still far from completely understanding the range of possible behaviors and how they might be exploited in neuromorphic computation. This work focuses on a newly developed Li$_textbf{x}$WO$_textbf{3}$-based three-terminal memristor that exhibits tunable STP and a conductance response modeled by a double exponential decay. We derive a stochastic model of the device from experimental data and investigate how device stochasticity, STP, and the double exponential decay affect accuracy in a hierarchy of time-surfaces (HOTS) architecture. We found that the device's stochasticity does not affect accuracy, that STP can reduce the effect of salt and pepper noise in signals from event-based sensors, and that the double exponential decay improves accuracy by integrating temporal information over multiple time scales. Our approach can be generalized to study other memristive devices to build a better understanding of how control over temporal dynamics can enable neuromorphic engineers to fine-tune devices and architectures to fit their problems at hand.

Get summaries of the top AI research delivered straight to your inbox:

Overview

- Memristors are a promising technology for efficient neuromorphic architectures

- They can act as programmable synapses, combining processing and memory

- Recent work has explored using their dynamic properties, like Short Term Plasticity (STP), in event-based architectures

- However, the full range of possible behaviors and how to exploit them in neuromorphic computation is still not well understood

Plain English Explanation

Memristors are a type of electronic component that can act like the connections (synapses) between neurons in the brain. This allows them to be used to build efficient neuromorphic (brain-inspired) computer architectures. While memristors are commonly used to statically encode synaptic weights, recent research has begun to investigate how their dynamic properties, such as Short Term Plasticity (STP), can be used in event-based neuromorphic systems.

This work focuses on a new type of three-terminal memristor made with lithium tungstate (Li<sub>x</sub>WO<sub>3</sub>) that exhibits tunable STP and a unique conductance response modeled by a "double exponential decay." The researchers developed a stochastic (probabilistic) model of this device based on experimental data, and investigated how the device's stochasticity, STP, and double exponential decay affect the performance of a "Hierarchy of Time Surfaces" (HOTS) neuromorphic architecture.

Technical Explanation

The researchers derived a stochastic model of the Li<sub>x</sub>WO<sub>3</sub>-based three-terminal memristor device from experimental data. They then investigated how the device's stochasticity, Short Term Plasticity (STP), and double exponential conductance decay affect the performance of a Hierarchy of Time Surfaces (HOTS) neuromorphic architecture.

They found that the device's stochasticity does not negatively impact accuracy, that STP can reduce the effect of noise in signals from event-based sensors, and that the double exponential decay improves accuracy by integrating temporal information over multiple time scales.

This approach can be generalized to study other memristive devices in order to better understand how control over temporal dynamics can enable neuromorphic engineers to fine-tune devices and architectures to fit their specific application needs.

Critical Analysis

The researchers acknowledge that they have only scratched the surface in terms of understanding the full range of behaviors that can be exhibited by this new Li<sub>x</sub>WO<sub>3</sub>-based memristor device and how to best leverage those properties for neuromorphic computing. Further research is needed to fully characterize the device and explore its potential applications.

Additionally, the experiments were conducted in simulation rather than with a physical implementation of the HOTS architecture. While the simulation results are promising, it will be important to validate the findings through real-world testing to ensure the device behaves as expected when integrated into a complete neuromorphic system.

Conclusion

This work demonstrates the potential of a new Li<sub>x</sub>WO<sub>3</sub>-based three-terminal memristor device to enable more efficient and capable neuromorphic computing systems. By harnessing the device's dynamic properties, such as Short Term Plasticity and temporal integration, neuromorphic engineers may be able to develop brain-inspired architectures that are better suited for processing real-world, event-based sensory data. Further research in this area could lead to significant advancements in neuromorphic computing and its applications.

This summary was produced with help from an AI and may contain inaccuracies - check out the links to read the original source documents!

Related Papers

💬

Spintronic memristors for computing

Qiming Shao, Zhongrui Wang, Yan Zhou, Shunsuke Fukami, Damien Querlioz, Yiran Chen, Leon O. Chua

0

0

The ever-increasing amount of data from ubiquitous smart devices fosters data-centric and cognitive algorithms. Traditional digital computer systems have separate logic and memory units, resulting in a huge delay and energy cost for implementing these algorithms. Memristors are programmable resistors with a memory, providing a paradigm-shifting approach towards creating intelligent hardware systems to handle data-centric tasks. Spintronic nanodevices are promising choices as they are high-speed, low-power, highly scalable, robust, and capable of constructing dynamic complex systems. In this Review, we survey spintronic devices from a memristor point of view. We introduce spintronic memristors based on magnetic tunnel junctions, nanomagnet ensemble, domain walls, topological spin textures, and spin waves, which represent dramatically different state spaces. They can exhibit steady, oscillatory, stochastic, and chaotic trajectories in their state spaces, which have been exploited for in-memory logic, neuromorphic computing, stochastic and chaos computing. Finally, we discuss challenges and trends in realizing large-scale spintronic memristive systems for practical applications.

4/23/2024

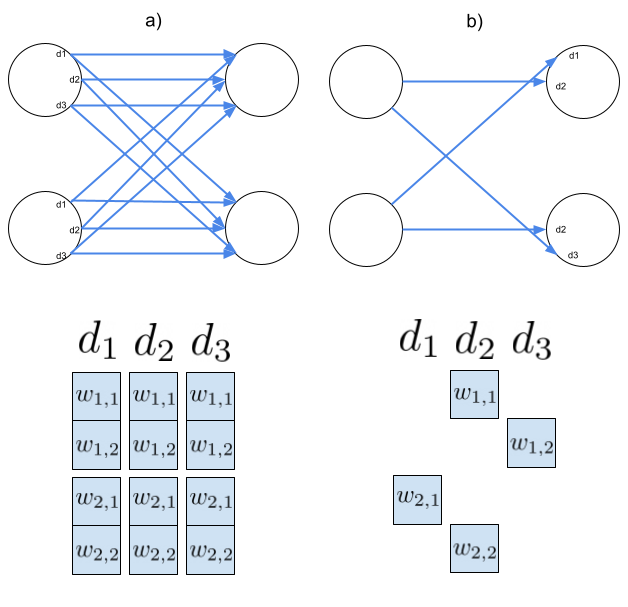

Hardware-aware training of models with synaptic delays for digital event-driven neuromorphic processors

Alberto Patino-Saucedo, Roy Meijer, Amirreza Yousefzadeh, Manil-Dev Gomony, Federico Corradi, Paul Detteter, Laura Garrido-Regife, Bernabe Linares-Barranco, Manolis Sifalakis

0

0

Configurable synaptic delays are a basic feature in many neuromorphic neural network hardware accelerators. However, they have been rarely used in model implementations, despite their promising impact on performance and efficiency in tasks that exhibit complex (temporal) dynamics, as it has been unclear how to optimize them. In this work, we propose a framework to train and deploy, in digital neuromorphic hardware, highly performing spiking neural network models (SNNs) where apart from the synaptic weights, the per-synapse delays are also co-optimized. Leveraging spike-based back-propagation-through-time, the training accounts for both platform constraints, such as synaptic weight precision and the total number of parameters per core, as a function of the network size. In addition, a delay pruning technique is used to reduce memory footprint with a low cost in performance. We evaluate trained models in two neuromorphic digital hardware platforms: Intel Loihi and Imec Seneca. Loihi offers synaptic delay support using the so-called Ring-Buffer hardware structure. Seneca does not provide native hardware support for synaptic delays. A second contribution of this paper is therefore a novel area- and memory-efficient hardware structure for acceleration of synaptic delays, which we have integrated in Seneca. The evaluated benchmark involves several models for solving the SHD (Spiking Heidelberg Digits) classification task, where minimal accuracy degradation during the transition from software to hardware is demonstrated. To our knowledge, this is the first work showcasing how to train and deploy hardware-aware models parameterized with synaptic delays, on multicore neuromorphic hardware accelerators.

4/17/2024

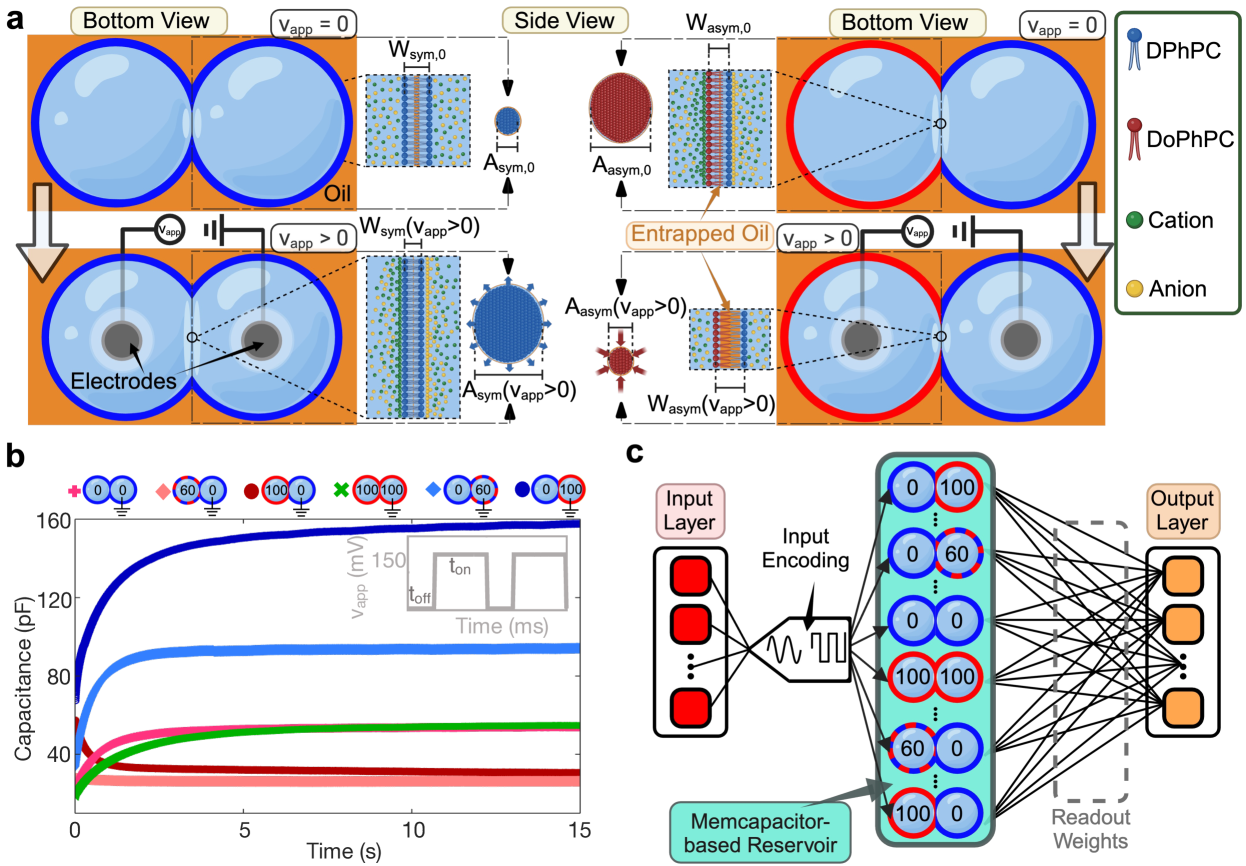

Intrinsic Voltage Offsets in Memcapacitive Bio-Membranes Enable High-Performance Physical Reservoir Computing

Ahmed S. Mohamed, Anurag Dhungel, Md Sakib Hasan, Joseph S. Najem

0

0

Reservoir computing is a brain-inspired machine learning framework for processing temporal data by mapping inputs into high-dimensional spaces. Physical reservoir computers (PRCs) leverage native fading memory and nonlinearity in physical substrates, including atomic switches, photonics, volatile memristors, and, recently, memcapacitors, to achieve efficient high-dimensional mapping. Traditional PRCs often consist of homogeneous device arrays, which rely on input encoding methods and large stochastic device-to-device variations for increased nonlinearity and high-dimensional mapping. These approaches incur high pre-processing costs and restrict real-time deployment. Here, we introduce a novel heterogeneous memcapacitor-based PRC that exploits internal voltage offsets to enable both monotonic and non-monotonic input-state correlations crucial for efficient high-dimensional transformations. We demonstrate our approach's efficacy by predicting a second-order nonlinear dynamical system with an extremely low prediction error (0.00018). Additionally, we predict a chaotic H'enon map, achieving a low normalized root mean square error (0.080). Unlike previous PRCs, such errors are achieved without input encoding methods, underscoring the power of distinct input-state correlations. Most importantly, we generalize our approach to other neuromorphic devices that lack inherent voltage offsets using externally applied offsets to realize various input-state correlations. Our approach and unprecedented performance are a major milestone towards high-performance full in-materia PRCs.

5/16/2024

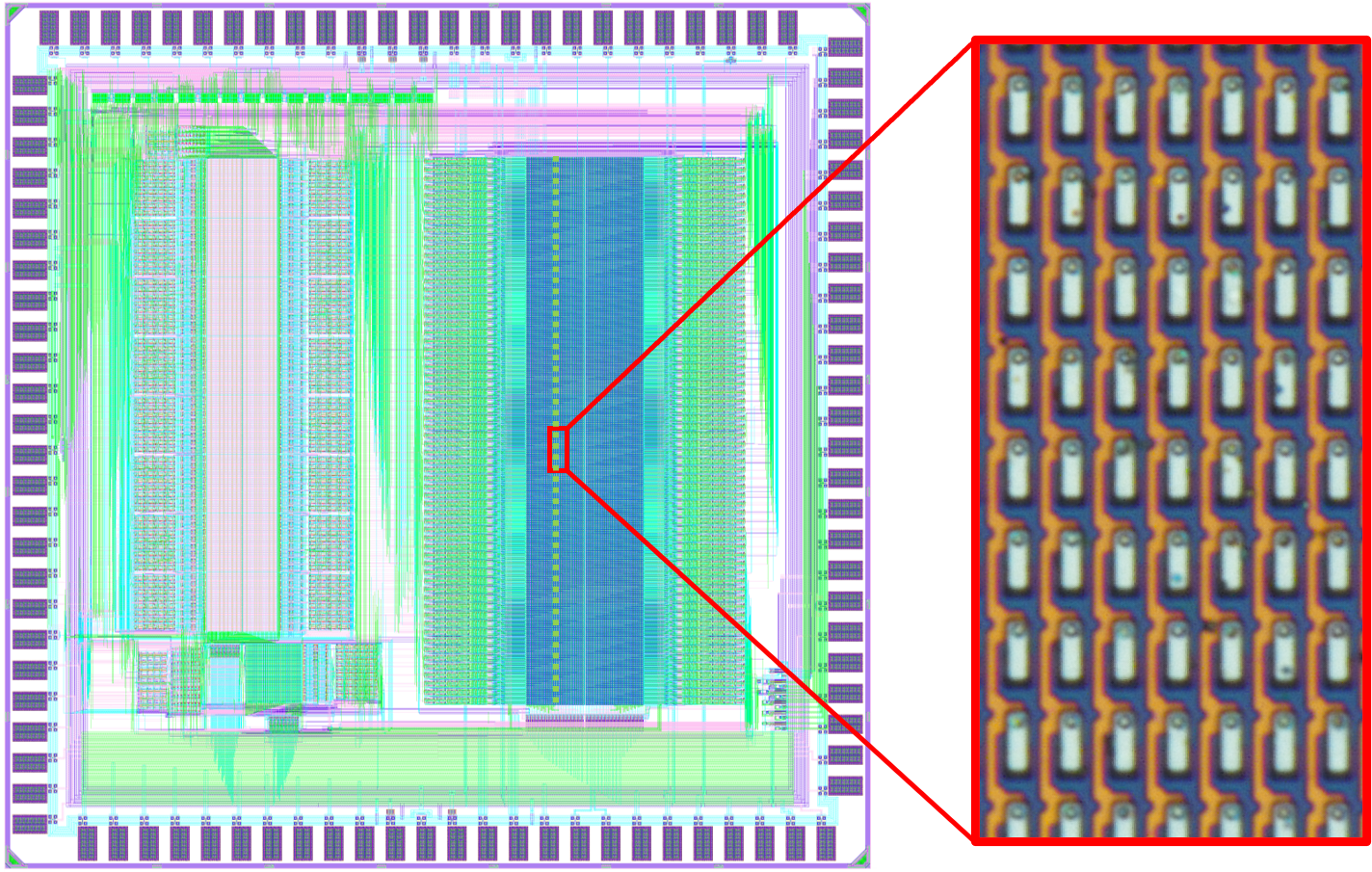

Synaptogen: A cross-domain generative device model for large-scale neuromorphic circuit design

Tyler Hennen, Leon Brackmann, Tobias Ziegler, Sebastian Siegel, Stephan Menzel, Rainer Waser, Dirk J. Wouters, Daniel Bedau

0

0

We present a fast generative modeling approach for resistive memories that reproduces the complex statistical properties of real-world devices. To enable efficient modeling of analog circuits, the model is implemented in Verilog-A. By training on extensive measurement data of integrated 1T1R arrays (6,000 cycles of 512 devices), an autoregressive stochastic process accurately accounts for the cross-correlations between the switching parameters, while non-linear transformations ensure agreement with both cycle-to-cycle (C2C) and device-to-device (D2D) variability. Benchmarks show that this statistically comprehensive model achieves read/write throughputs exceeding those of even highly simplified and deterministic compact models.

4/10/2024