CNN-Based Equalization for Communications: Achieving Gigabit Throughput with a Flexible FPGA Hardware Architecture

2405.02323

2

0

🛸

Abstract

To satisfy the growing throughput demand of data-intensive applications, the performance of optical communication systems increased dramatically in recent years. With higher throughput, more advanced equalizers are crucial, to compensate for impairments caused by inter-symbol interference (ISI). The latest research shows that artificial neural network (ANN)-based equalizers are promising candidates to replace traditional algorithms for high-throughput communications. On the other hand, not only throughput but also flexibility is a main objective of beyond-5G and 6G communication systems. A platform that is able to satisfy the strict throughput and flexibility requirements of modern communication systems are field programmable gate arrays (FPGAs). Thus, in this work, we present a high-performance FPGA implementation of an ANN-based equalizer, which meets the throughput requirements of modern optical communication systems. Further, our architecture is highly flexible since it includes a variable degree of parallelism (DOP) and therefore can also be applied to low-cost or low-power applications which is demonstrated for a magnetic recording channel. The implementation is based on a cross-layer design approach featuring optimizations from the algorithm down to the hardware architecture, including a detailed quantization analysis. Moreover, we present a framework to reduce the latency of the ANN-based equalizer under given throughput constraints. As a result, the bit error ratio (BER) of our equalizer for the optical fiber channel is around four times lower than that of a conventional one, while the corresponding FPGA implementation achieves a throughput of more than 40 GBd, outperforming a high-performance graphics processing unit (GPU) by three orders of magnitude for a similar batch size.

Create account to get full access

Overview

- Increasing throughput demand in data-intensive applications has driven significant performance improvements in optical communication systems

- Advanced equalizers are crucial to compensate for impairments caused by inter-symbol interference (ISI) in high-throughput communications

- Artificial neural network (ANN)-based equalizers are promising replacements for traditional algorithms

- Field programmable gate arrays (FPGAs) can provide the high throughput and flexibility required for beyond-5G and 6G communication systems

Plain English Explanation

As the need for faster data transfer has grown, optical communication systems have made major advancements in their performance. With these higher data rates, more sophisticated equalizers are necessary to counteract the distortions caused by interference between adjacent data signals. The latest research shows that ANN-based equalizers have the potential to outperform traditional equalizer algorithms in high-throughput applications.

At the same time, future communication networks not only require high throughput, but also increased flexibility. FPGAs are a platform that can meet both of these demands. This work presents a high-performance FPGA implementation of an ANN-based equalizer designed for modern optical communication systems. The architecture is highly flexible, as it can adjust the degree of parallelism to suit different throughput and power requirements, even for applications like magnetic recording.

The researchers used a comprehensive, cross-layer design approach, optimizing the algorithm, quantization, and hardware implementation. They also developed a framework to minimize the latency of the ANN equalizer while meeting throughput targets. As a result, the bit error rate of their equalizer for optical fiber is about four times lower than a conventional equalizer, while achieving over 40 gigabits per second of throughput - significantly faster than a high-performance GPU.

Technical Explanation

This work presents a high-performance FPGA implementation of an ANN-based equalizer designed to meet the throughput requirements of modern optical communication systems. The researchers used a cross-layer design approach, optimizing the algorithm, quantization, and hardware architecture.

The key aspects of the technical implementation include:

- A variable degree of parallelism (DOP) in the architecture, allowing flexibility for different throughput and power requirements

- A detailed quantization analysis to determine the optimal fixed-point representation

- A framework to minimize the latency of the ANN equalizer under given throughput constraints

The researchers evaluated the ANN-based equalizer on an optical fiber channel and a magnetic recording channel. For the optical fiber channel, the bit error ratio (BER) of their equalizer is around four times lower than a conventional equalizer, while achieving a throughput of over 40 gigabits per second. This throughput outperforms a high-performance GPU by three orders of magnitude for a similar batch size.

Critical Analysis

The paper provides a comprehensive and well-designed implementation of an ANN-based equalizer on FPGA hardware. The researchers addressed several key challenges, including achieving high throughput, flexibility, and low latency.

One potential limitation is the evaluation was primarily focused on optical fiber and magnetic recording channels. While the architecture is designed to be flexible, it would be valuable to see the performance on a broader range of communication channels to fully assess its generalizability.

Additionally, the paper does not provide much insight into the training process or hyperparameter tuning of the ANN model. Further details on these aspects could help other researchers build upon this work more effectively.

Overall, this is a strong technical contribution that demonstrates the potential of ANN-based equalizers and FPGA implementations to address the demands of future high-throughput, flexible communication systems. The insights and design principles presented here could be applicable to a wide range of signal processing and communications applications.

Conclusion

This work presents a high-performance FPGA implementation of an ANN-based equalizer that can meet the throughput requirements of modern optical communication systems. The key innovations include a flexible architecture with variable parallelism, a quantization analysis, and a framework to optimize latency under throughput constraints.

The researchers were able to achieve a bit error ratio around four times lower than a conventional equalizer, while delivering over 40 gigabits per second of throughput - significantly outperforming a high-performance GPU. This demonstrates the potential of ANN-based equalizers and FPGA platforms to address the evolving needs of beyond-5G and 6G communication networks, which require both high throughput and flexibility.

This summary was produced with help from an AI and may contain inaccuracies - check out the links to read the original source documents!

Related Papers

🌐

Advanced Equalization in 112 Gb/s Upstream PON Using a Novel Fourier Convolution-based Network

Chen Shao, Elias Giacoumidis, Patrick Matalla, Jialei Li, Shi Li, Sebastian Randel, Andre Richter, Michael Faerber, Tobias Kaefer

0

0

We experimentally demonstrate a novel, low-complexity Fourier Convolution-based Network (FConvNet) based equalizer for 112 Gb/s upstream PAM4-PON. At a BER of 0.005, FConvNet enhances the receiver sensitivity by 2 and 1 dB compared to a 51-tap Sato equalizer and benchmark machine learning algorithms respectively.

5/7/2024

A Novel Machine Learning-based Equalizer for a Downstream 100G PAM-4 PON

Chen Shao, Elias Giacoumidis, Shi Li, Jialei Li, Michael Faerber, Tobias Kaefer, Andre Richter

0

0

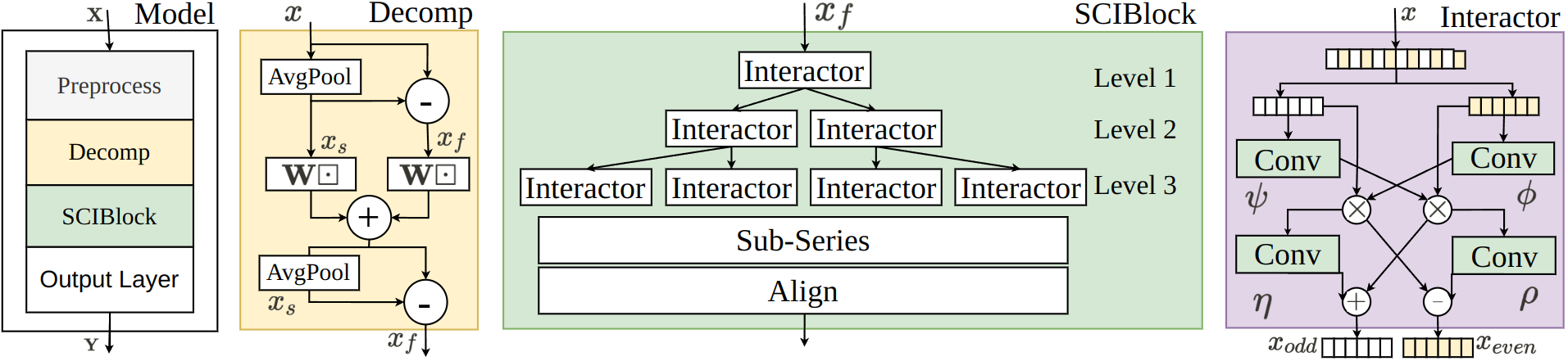

A frequency-calibrated SCINet (FC-SCINet) equalizer is proposed for down-stream 100G PON with 28.7 dB path loss. At 5 km, FC-SCINet improves the BER by 88.87% compared to FFE and a 3-layer DNN with 10.57% lower complexity.

5/3/2024

Embedded FPGA Developments in 130nm and 28nm CMOS for Machine Learning in Particle Detector Readout

Julia Gonski, Aseem Gupta, Haoyi Jia, Hyunjoon Kim, Lorenzo Rota, Larry Ruckman, Angelo Dragone, Ryan Herbst

0

0

Embedded field programmable gate array (eFPGA) technology allows the implementation of reconfigurable logic within the design of an application-specific integrated circuit (ASIC). This approach offers the low power and efficiency of an ASIC along with the ease of FPGA configuration, particularly beneficial for the use case of machine learning in the data pipeline of next-generation collider experiments. An open-source framework called FABulous was used to design eFPGAs using 130 nm and 28 nm CMOS technology nodes, which were subsequently fabricated and verified through testing. The capability of an eFPGA to act as a front-end readout chip was tested using simulation of high energy particles passing through a silicon pixel sensor. A machine learning-based classifier, designed for reduction of sensor data at the source, was synthesized and configured onto the eFPGA. A successful proof-of-concept was demonstrated through reproduction of the expected algorithm result on the eFPGA with perfect accuracy. Further development of the eFPGA technology and its application to collider detector readout is discussed.

4/30/2024

Deep-Learning-Based Channel Estimation for Distributed MIMO with 1-bit Radio-Over-Fiber Fronthaul

Alireza Bordbar, Lise Aabel, Christian Hager, Christian Fager, Giuseppe Durisi

0

0

We consider the problem of pilot-aided, uplink channel estimation in a distributed massive multiple-input multiple-output (MIMO) architecture, in which the access points are connected to a central processing unit via fiber-optical fronthaul links, carrying a two-level-quantized version of the received analog radio-frequency signal. We adapt to this architecture the deep-learning-based channel-estimation algorithm recently proposed by Nguyen et al. (2023), and explore its robustness to the additional signal distortions (beyond 1-bit quantization) introduced in the considered architecture by the automatic gain controllers (AGCs) and by the comparators. These components are used at the access points to generate the two-level analog waveform from the received signal. Via simulation results, we illustrate that the proposed channel-estimation method outperforms significantly the Bussgang linear minimum mean-square error channel estimator, and it is robust against the additional impairments introduced by the AGCs and the comparators.

6/18/2024