Domain wall and Magnetic Tunnel Junction Hybrid for on-chip Learning in UNet architecture

0

Sign in to get full access

Overview

- This paper presents a spintronic implementation of the U-Net architecture for image segmentation tasks.

- It explores the use of magnetic tunnel junctions (MTJs) and domain wall dynamics to perform the convolution and pooling operations in a U-Net network.

- The proposed approach aims to take advantage of the non-volatile and energy-efficient properties of spintronics to create a more efficient and compact image segmentation system.

Plain English Explanation

The researchers in this study wanted to find a new way to do image segmentation, which is the process of dividing an image into different parts or "segments." Image segmentation is an important task in many applications like self-driving cars, medical imaging, and object detection.

Traditionally, image segmentation is done using deep learning models like the U-Net architecture. These models are typically implemented using standard electronics, which can be power-hungry and take up a lot of space.

The researchers in this paper explored using a technology called spintronics to implement the U-Net architecture instead. Spintronics uses the magnetic properties of materials to store and process information, which can be more energy-efficient and compact than traditional electronics.

Specifically, the researchers proposed using magnetic tunnel junctions (MTJs) and domain wall dynamics to perform the key operations in the U-Net model, like convolution and pooling. By leveraging the unique properties of spintronics, they aimed to create a more efficient and compact image segmentation system.

Technical Explanation

The key components of the proposed spintronic U-Net architecture are:

-

Convolution: The researchers used magnetic tunnel junctions (MTJs) to perform the convolution operation. MTJs can be used to implement weighted sums efficiently by taking advantage of their resistance-based readout.

-

Pooling: For the pooling operation, the researchers relied on domain wall dynamics. By controlling the movement of magnetic domain walls, they were able to perform max pooling in a compact and energy-efficient manner.

-

Training: To train the spintronic U-Net, the researchers used a measurement-driven approach that leverages the unique properties of MTJs and domain walls to enable efficient training.

The researchers demonstrated the feasibility of their approach through experimental validation using a deep multi-threshold spiking U-Net for image segmentation tasks.

Critical Analysis

The proposed spintronic implementation of U-Net offers several potential benefits, such as improved energy efficiency and reduced footprint compared to traditional electronics-based approaches. However, the paper does not address several important practical considerations:

-

Scalability: The researchers only demonstrated their approach on relatively small-scale image segmentation tasks. It's unclear how well the spintronic U-Net would scale to more complex, high-resolution images and larger models.

-

Training Complexity: While the measurement-driven training approach is interesting, it may introduce additional complexity and challenges compared to standard deep learning training methods.

-

Hardware Integration: The integration of spintronic components like MTJs and domain walls into a complete, high-performing image segmentation system is likely to involve significant engineering challenges.

-

Performance Benchmarking: The paper lacks a detailed comparison of the spintronic U-Net's performance (in terms of accuracy, speed, power consumption, etc.) against state-of-the-art electronics-based U-Net implementations.

Conclusion

This paper presents a novel approach to implementing the U-Net architecture for image segmentation using spintronic components like magnetic tunnel junctions and domain wall dynamics. The proposed design aims to leverage the energy-efficient and compact properties of spintronics to create a more efficient and compact image segmentation system.

While the theoretical foundation and experimental validation are promising, the paper does not fully address the practical challenges and limitations of the spintronic U-Net approach. Further research and development will be necessary to assess the real-world viability and performance of this technology for large-scale image segmentation tasks.

This summary was produced with help from an AI and may contain inaccuracies - check out the links to read the original source documents!

Related Papers

0

Domain wall and Magnetic Tunnel Junction Hybrid for on-chip Learning in UNet architecture

Venkatesh Vadde, Bhaskaran Muralidharan, Abhishek Sharma

We present spintronic devices based hardware implementation of UNet for segmentation tasks. Our approach involves designing hardware for convolution, deconvolution, rectified activation function (ReLU), and max pooling layers of the UNet architecture. We designed the convolution and deconvolution layers of the network using the synaptic behavior of the domain wall MTJ. We also construct the ReLU and max pooling functions of the network utilizing the spin hall driven orthogonal current injected MTJ. To incorporate the diverse physics of spin-transport, magnetization dynamics, and CMOS elements in our UNet design, we employ a hybrid simulation setup that couples micromagnetic simulation, non-equilibrium Green's function, SPICE simulation along with network implementation. We evaluate our UNet design on the CamVid dataset and achieve segmentation accuracies of 83.71$%$ on test data, on par with the software implementation with 821mJ of energy consumption for on-chip training over 150 epochs. We further demonstrate nearly one order $(10times)$ improvement in the energy requirement of the network using unstable ferromagnet ($Delta$=4.58) over the stable ferromagnet ($Delta$=45) based ReLU and max pooling functions while maintaining the similar accuracy. The hybrid architecture comprising domain wall MTJ and unstable FM-based MTJ leads to an on-chip energy consumption of 85.79mJ during training, with a testing energy cost of 1.55 $mu J$.

Read more7/12/2024

👀

0

A design of magnetic tunnel junctions for the deployment of neuromorphic hardware for edge computing

Davi Rodrigues, Eleonora Raimondo, Riccardo Tomasello, Mario Carpentieri, Giovanni Finocchio

The electrically readable complex dynamics of robust and scalable magnetic tunnel junctions (MTJs) offer promising opportunities for advancing neuromorphic computing. In this work, we present an MTJ design with a free layer and two polarizers capable of computing the sigmoidal activation function and its gradient at the device level. This design enables both feedforward and backpropagation computations within a single device, extending neuromorphic computing frameworks previously explored in the literature by introducing the ability to perform backpropagation directly in hardware. Our algorithm implementation reveals two key findings: (i) the small discrepancies between the MTJ-generated curves and the exact software-generated curves have a negligible impact on the performance of the backpropagation algorithm, (ii) the device implementation is highly robust to inter-device variation and noise, and (iii) the proposed method effectively supports transfer learning and knowledge distillation. To demonstrate this, we evaluated the performance of an edge computing network using weights from a software-trained model implemented with our MTJ design. The results show a minimal loss of accuracy of only 0.1% for the Fashion MNIST dataset and 2% for the CIFAR-100 dataset compared to the original software implementation. These results highlight the potential of our MTJ design for compact, hardware-based neural networks in edge computing applications, particularly for transfer learning.

Read more9/5/2024

🤔

0

Domain Wall Magnetic Tunnel Junction Reliable Integrate and Fire Neuron

Can Cui1, Sam Liu, Jaesuk Kwon, Jean Anne C. Incorvia

In spiking neural networks, neuron dynamics are described by the biologically realistic integrate-and-fire model that captures membrane potential accumulation and above-threshold firing behaviors. Among the hardware implementations of integrate-and-fire neuron devices, one important feature, reset, has been largely ignored. Here, we present the design and fabrication of a magnetic domain wall and magnetic tunnel junction based artificial integrate-and-fire neuron device that achieves reliable reset at the end of the integrate-fire cycle. We demonstrate the domain propagation in the domain wall racetrack (integration), reading using a magnetic tunnel junction (fire), and reset as the domain is ejected from the racetrack, showing the artificial neuron can be operated continuously over 100 integrate-fire-reset cycles. Both pulse amplitude and pulse number encoding is demonstrated. The device data is applied on an image classification task using a spiking neural network and shown to have comparable performance to an ideal leaky, integrate-and-fire neural network. These results achieve the first demonstration of reliable integrate-fire-reset in domain wall-magnetic tunnel junction-based neuron devices and shows the promise of spintronics for neuromorphic computing.

Read more5/24/2024

0

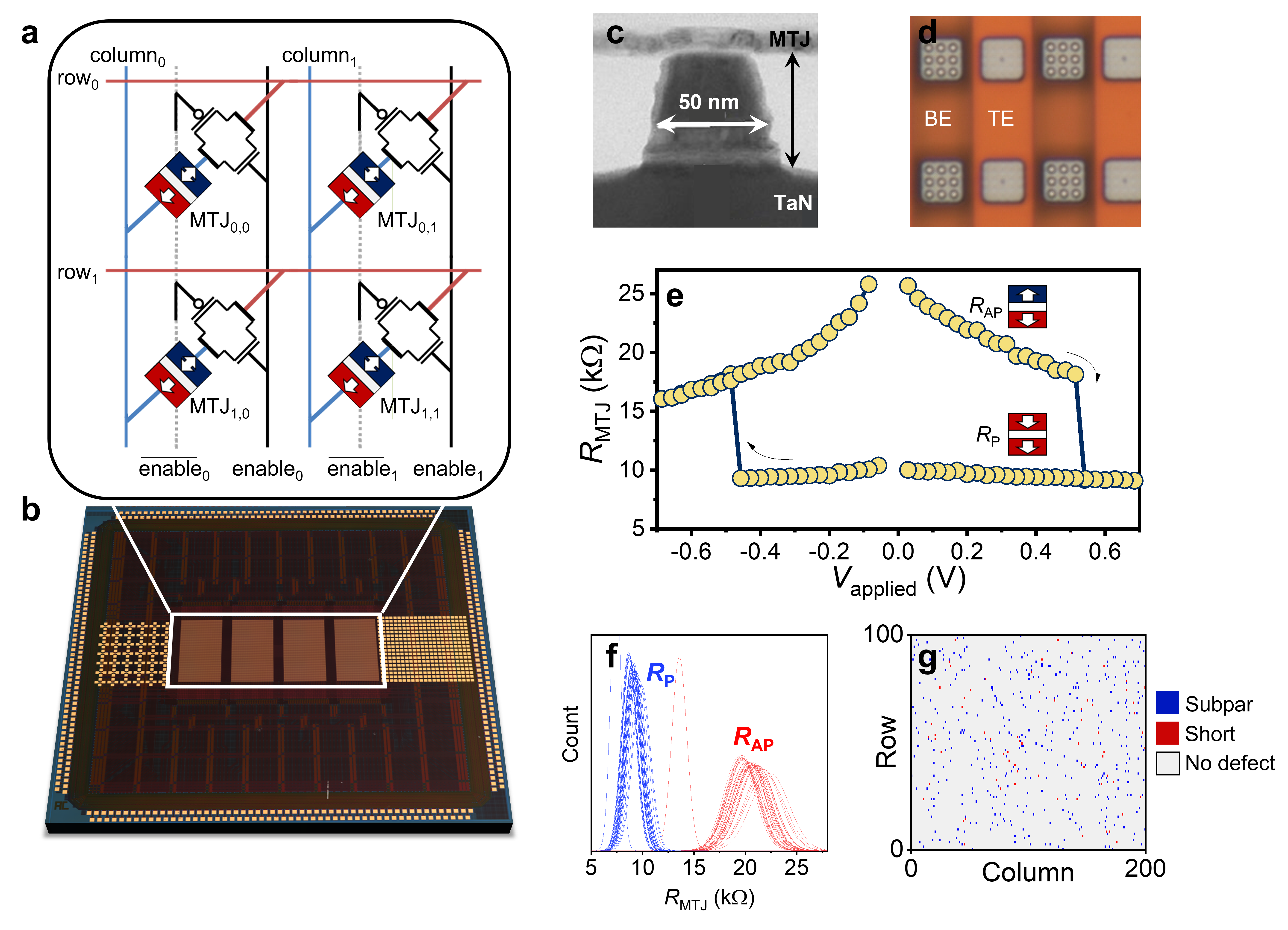

Measurement-driven neural-network training for integrated magnetic tunnel junction arrays

William A. Borders, Advait Madhavan, Matthew W. Daniels, Vasileia Georgiou, Martin Lueker-Boden, Tiffany S. Santos, Patrick M. Braganca, Mark D. Stiles, Jabez J. McClelland, Brian D. Hoskins

The increasing scale of neural networks needed to support more complex applications has led to an increasing requirement for area- and energy-efficient hardware. One route to meeting the budget for these applications is to circumvent the von Neumann bottleneck by performing computation in or near memory. An inevitability of transferring neural networks onto hardware is that non-idealities such as device-to-device variations or poor device yield impact performance. Methods such as hardware-aware training, where substrate non-idealities are incorporated during network training, are one way to recover performance at the cost of solution generality. In this work, we demonstrate inference on hardware neural networks consisting of 20,000 magnetic tunnel junction arrays integrated on a complementary metal-oxide-semiconductor chips that closely resembles market-ready spin transfer-torque magnetoresistive random access memory technology. Using 36 dies, each containing a crossbar array with its own non-idealities, we show that even a small number of defects in physically mapped networks significantly degrades the performance of networks trained without defects and show that, at the cost of generality, hardware-aware training accounting for specific defects on each die can recover to comparable performance with ideal networks. We then demonstrate a robust training method that extends hardware-aware training to statistics-aware training, producing network weights that perform well on most defective dies regardless of their specific defect locations. When evaluated on the 36 physical dies, statistics-aware trained solutions can achieve a mean misclassification error on the MNIST dataset that differs from the software-baseline by only 2 %. This statistics-aware training method could be generalized to networks with many layers that are mapped to hardware suited for industry-ready applications.

Read more5/15/2024