Highly Versatile FPGA-Implemented Cyber Coherent Ising Machine

0

Sign in to get full access

Overview

- FPGA-implemented cyber coherent Ising machine with high versatility

- Capable of implementing a variety of algorithms for solving optimization problems

- Leverages FPGA hardware to achieve high performance and energy efficiency

Plain English Explanation

This research paper describes an FPGA-based system that can be used to solve a wide range of optimization problems. Optimization problems are mathematical challenges where the goal is to find the best solution from a set of possible solutions. These problems arise in many real-world applications, such as scheduling, resource allocation, and decision-making.

The key innovation in this work is the use of an FPGA (Field-Programmable Gate Array) to implement a "cyber coherent Ising machine." An Ising machine is a type of analog computing device that can be used to solve optimization problems by mapping them to the energy minimization of a physical system. By implementing this Ising machine on an FPGA, the researchers were able to create a highly versatile and efficient system for solving these optimization problems.

The FPGA-based Ising machine described in this paper can be reconfigured to implement a variety of different algorithms, allowing it to tackle a wide range of optimization problems. This flexibility is important because optimization problems can take many different forms, and a one-size-fits-all approach is often not sufficient.

Technical Explanation

The researchers developed an FPGA-based system that can be used to implement a variety of algorithms for solving optimization problems. The core of the system is a "cyber coherent Ising machine," which is a type of analog computing device that can be used to solve optimization problems by mapping them to the energy minimization of a physical system.

The researchers implemented this Ising machine on an FPGA, which allowed them to create a highly versatile and efficient system. FPGAs are reconfigurable hardware devices that can be programmed to perform a wide range of different functions. By implementing the Ising machine on an FPGA, the researchers were able to create a system that can be reconfigured to implement a variety of different algorithms for solving optimization problems.

The researchers demonstrated the versatility of their system by using it to implement several different algorithms, including those described in the following related papers:

- L0-Regularized Compressed Sensing Mean-Field Coherent Ising Machine

- All-to-All Reconfigurability of Sparse Higher-Order Ising Machines

- Efficient Computation Using Spatial Photonic Ising Machines

- Multi-Digit Ising Mapping for Low-Precision Ising Machines

- Design and Execution of Quantum Circuits Using Tens of Superconducting Qubits

By implementing these algorithms on their FPGA-based Ising machine, the researchers were able to demonstrate the versatility and high performance of their system.

Critical Analysis

The researchers have developed a highly versatile FPGA-based system for solving optimization problems, and they have demonstrated its capabilities by implementing a variety of different algorithms. However, the paper does not provide much detail on the limitations or potential issues with their approach.

One potential concern is the scalability of the FPGA-based Ising machine. As the size and complexity of the optimization problems increase, the resource requirements of the FPGA-based system may also grow, potentially limiting its applicability to larger-scale problems.

Additionally, the paper does not discuss the energy efficiency of the FPGA-based system compared to other approaches, such as classical digital computing or quantum computing. While the researchers claim that their system is energy-efficient, more detailed analysis and comparisons would be helpful to fully assess its advantages and drawbacks.

Overall, the research described in this paper represents an interesting and potentially valuable contribution to the field of optimization algorithms and hardware acceleration. However, further research and analysis would be useful to better understand the limitations and trade-offs of the FPGA-based Ising machine approach.

Conclusion

The FPGA-implemented cyber coherent Ising machine described in this paper represents a highly versatile system for solving a wide range of optimization problems. By leveraging the reconfigurability of FPGA hardware, the researchers have created a system that can be adapted to implement a variety of different algorithms, allowing it to tackle a diverse set of optimization challenges.

While the paper demonstrates the capabilities of this FPGA-based system, further research is needed to fully understand its limitations and trade-offs, particularly in terms of scalability and energy efficiency. Nevertheless, this work represents an important advancement in the field of analog computing and hardware acceleration for optimization problems, with potentially significant implications for real-world applications.

This summary was produced with help from an AI and may contain inaccuracies - check out the links to read the original source documents!

Related Papers

0

Highly Versatile FPGA-Implemented Cyber Coherent Ising Machine

Toru Aonishi, Tatsuya Nagasawa, Toshiyuki Koizumi, Mastiyage Don Sudeera Hasaranga Gunathilaka, Kazushi Mimura, Masato Okada, Satoshi Kako, Yoshihisa Yamamoto

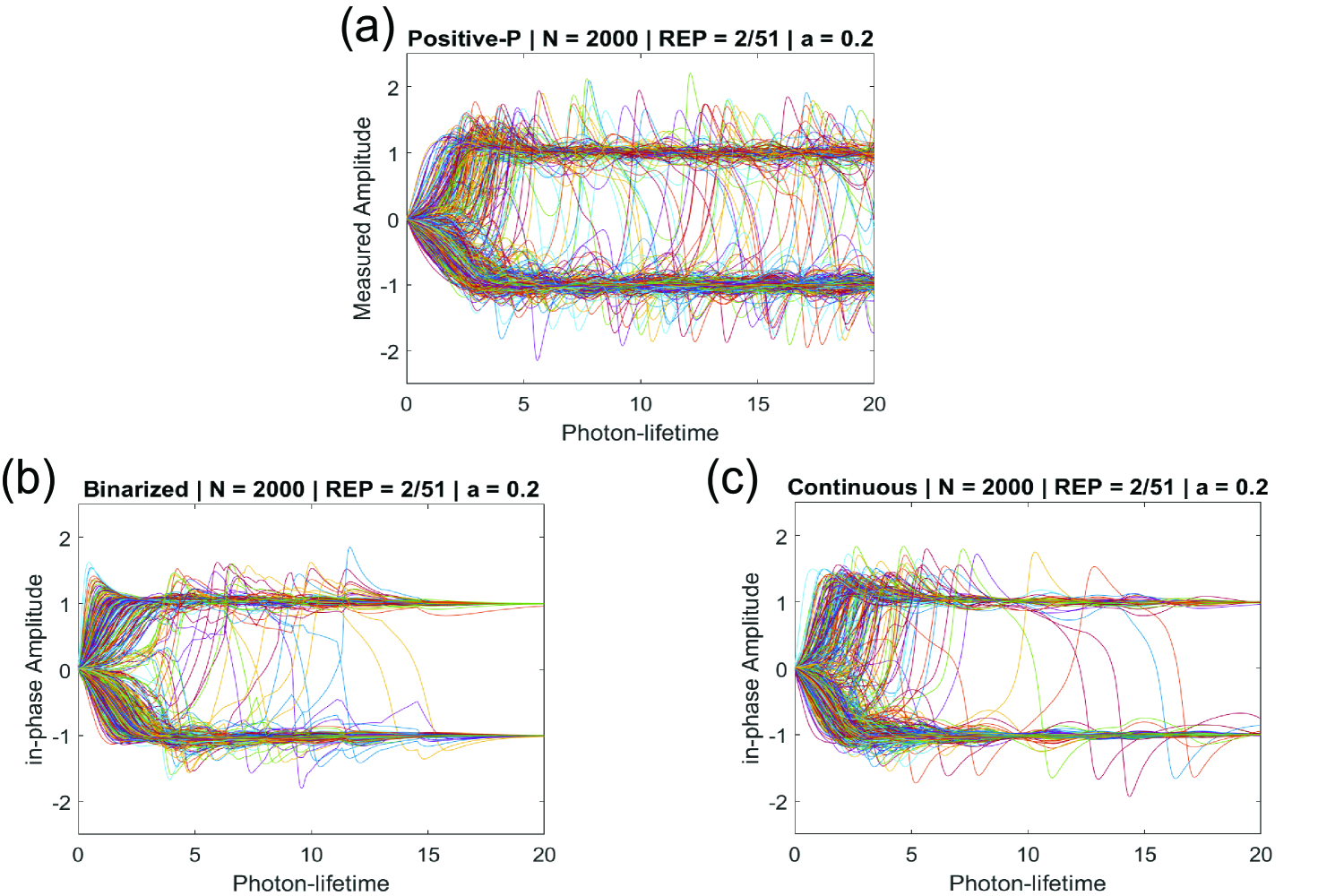

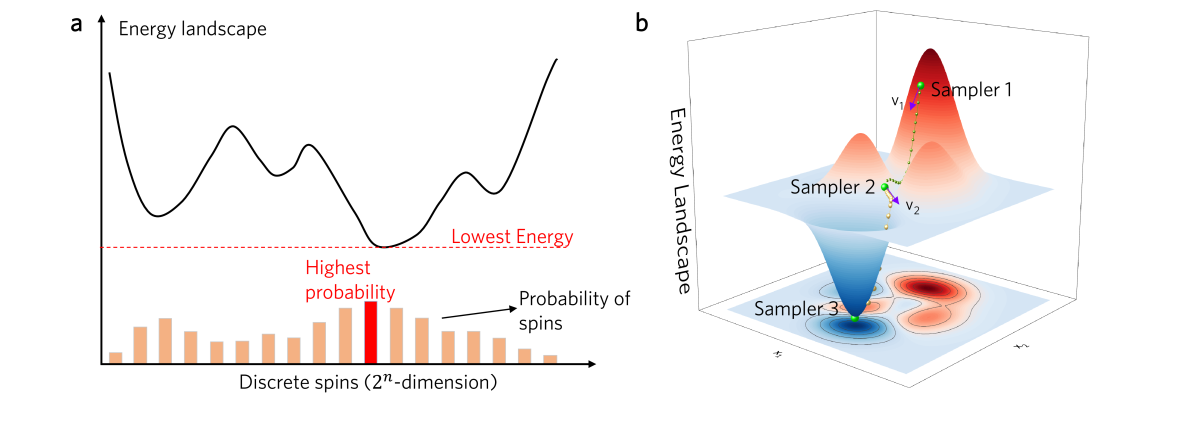

In recent years, quantum Ising machines have drawn a lot of attention, but due to physical implementation constraints, it has been difficult to achieve dense coupling, such as full coupling with sufficient spins to handle practical large-scale applications. Consequently, classically computable equations have been derived from quantum master equations for these quantum Ising machines. Parallel implementations of these algorithms using FPGAs have been used to rapidly find solutions to these problems on a scale that is difficult to achieve in physical systems. We have developed an FPGA implemented cyber coherent Ising machine (cyber CIM) that is much more versatile than previous implementations using FPGAs. Our architecture is versatile since it can be applied to the open-loop CIM, which was proposed when CIM research began, to the closed-loop CIM, which has been used recently, as well as to Jacobi successive over-relaxation method. By modifying the sequence control code for the calculation control module, other algorithms such as Simulated Bifurcation (SB) can also be implemented. Earlier research on large-scale FPGA implementations of SB and CIM used binary or ternary discrete values for connections, whereas the cyber CIM used FP32 values. Also, the cyber CIM utilized Zeeman terms that were represented as FP32, which were not present in other large-scale FPGA systems. Our implementation with continuous interaction realizes N=4096 on a single FPGA, comparable to the single-FPGA implementation of SB with binary interactions, with N=4096. The cyber CIM enables applications such as CDMA multi-user detector and L0 compressed sensing which were not possible with earlier FPGA systems, while enabling superior calculation speeds, more than ten times faster than a GPU implementation. The calculation speed can be further improved by increasing parallelism, such as through clustering.

Read more6/11/2024

0

L0-regularized compressed sensing with Mean-field Coherent Ising Machines

Mastiyage Don Sudeera Hasaranga Gunathilaka, Yoshitaka Inui, Satoshi Kako, Kazushi Mimura, Masato Okada, Yoshihisa Yamamoto, Toru Aonishi

Coherent Ising Machine (CIM) is a network of optical parametric oscillators that solves combinatorial optimization problems by finding the ground state of an Ising Hamiltonian. As a practical application of CIM, Aonishi et al. proposed a quantum-classical hybrid system to solve optimization problems of L0-regularization-based compressed sensing (L0RBCS). Gunathilaka et al. has further enhanced the accuracy of the system. However, the computationally expensive CIM's stochastic differential equations (SDEs) limit the use of digital hardware implementations. As an alternative to Gunathilaka et al.'s CIM SDEs used previously, we propose using the mean-field CIM (MF-CIM) model, which is a physics-inspired heuristic solver without quantum noise. MF-CIM surmounts the high computational cost due to the simple nature of the differential equations (DEs). Furthermore, our results indicate that the proposed model has similar performance to physically accurate SDEs in both artificial and magnetic resonance imaging data, paving the way for implementing CIM-based L0RBCS on digital hardware such as Field Programmable Gate Arrays (FPGAs).

Read more6/18/2024

0

All-to-all reconfigurability with sparse and higher-order Ising machines

Srijan Nikhar, Sidharth Kannan, Navid Anjum Aadit, Shuvro Chowdhury, Kerem Y. Camsari

Domain-specific hardware to solve computationally hard optimization problems has generated tremendous excitement recently. Here, we evaluate probabilistic bit (p-bit) based on Ising Machines (IM) or p-computers with a benchmark combinatorial optimization problem, namely the 3-regular 3-XOR Satisfiability (3R3X). The 3R3X problem has a glassy energy landscape, and it has recently been used to benchmark various IMs and other solvers. We introduce a multiplexed architecture where p-computers emulate all-to-all (complete) graph functionality despite being interconnected in sparse networks, enabling a highly parallelized chromatic Gibbs sampling. We implement this architecture in FPGAs and show that p-bit networks running an adaptive version of the powerful parallel tempering algorithm demonstrate competitive algorithmic and prefactor advantages over alternative IMs by D-Wave, Toshiba, and Fujitsu, except a greedy algorithm accelerated on a GPU. We further extend our APT results using higher-order interactions in FPGAs and show that while higher-order interactions lead to prefactor advantages, they do not show any algorithmic scaling advantages for the XORSAT problem, settling an open conjecture. Even though FPGA implementations of p-bits are still not quite as fast as the best possible greedy algorithms implemented in GPUs, scaled magnetic versions of p-computers could lead to orders of magnitude over such algorithms according to experimentally established projections.

Read more5/24/2024

0

Parallel Ising Annealer via Gradient-based Hamiltonian Monte Carlo

Hao Wang, Zixuan Liu, Zhixin Xie, Langyu Li, Zibo Miao, Wei Cui, Yu Pan

Ising annealer is a promising quantum-inspired computing architecture for combinatorial optimization problems. In this paper, we introduce an Ising annealer based on the Hamiltonian Monte Carlo, which updates the variables of all dimensions in parallel. The main innovation is the fusion of an approximate gradient-based approach into the Ising annealer which introduces significant acceleration and allows a portable and scalable implementation on the commercial FPGA. Comprehensive simulation and hardware experiments show that the proposed Ising annealer has promising performance and scalability on all types of benchmark problems when compared to other Ising annealers including the state-of-the-art hardware. In particular, we have built a prototype annealer which solves Ising problems of both integer and fraction coefficients with up to 200 spins on a single low-cost FPGA board, whose performance is demonstrated to be better than the state-of-the-art quantum hardware D-Wave 2000Q and similar to the expensive coherent Ising machine. The sub-linear scalability of the annealer signifies its potential in solving challenging combinatorial optimization problems and evaluating the advantage of quantum hardware.

Read more7/16/2024