Investigating Resource-efficient Neutron/Gamma Classification ML Models Targeting eFPGAs

2404.14436

0

0

🏷️

Abstract

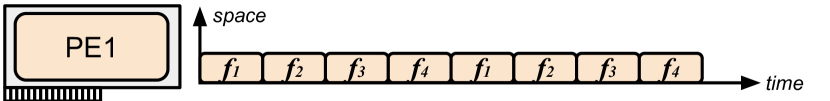

There has been considerable interest and resulting progress in implementing machine learning (ML) models in hardware over the last several years from the particle and nuclear physics communities. A big driver has been the release of the Python package, hls4ml, which has enabled porting models specified and trained using Python ML libraries to register transfer level (RTL) code. So far, the primary end targets have been commercial FPGAs or synthesized custom blocks on ASICs. However, recent developments in open-source embedded FPGA (eFPGA) frameworks now provide an alternate, more flexible pathway for implementing ML models in hardware. These customized eFPGA fabrics can be integrated as part of an overall chip design. In general, the decision between a fully custom, eFPGA, or commercial FPGA ML implementation will depend on the details of the end-use application. In this work, we explored the parameter space for eFPGA implementations of fully-connected neural network (fcNN) and boosted decision tree (BDT) models using the task of neutron/gamma classification with a specific focus on resource efficiency. We used data collected using an AmBe sealed source incident on Stilbene, which was optically coupled to an OnSemi J-series SiPM to generate training and test data for this study. We investigated relevant input features and the effects of bit-resolution and sampling rate as well as trade-offs in hyperparameters for both ML architectures while tracking total resource usage. The performance metric used to track model performance was the calculated neutron efficiency at a gamma leakage of 10$^{-3}$. The results of the study will be used to aid the specification of an eFPGA fabric, which will be integrated as part of a test chip.

Create account to get full access

Overview

- The paper explores the implementation of machine learning (ML) models in hardware, specifically using embedded FPGA (eFPGA) frameworks.

- The focus is on the resource efficiency of fully-connected neural networks (fcNN) and boosted decision tree (BDT) models for the task of neutron/gamma classification.

- The authors used data collected from an AmBe sealed source incident on Stilbene, coupled with an OnSemi J-series SiPM, to generate training and test data for their study.

- The performance metric tracked was the calculated neutron efficiency at a gamma leakage of 10^-3.

- The results will be used to aid the specification of an eFPGA fabric, which will be integrated into a test chip.

Plain English Explanation

In recent years, there has been growing interest in using machine learning (ML) models in hardware, particularly in the fields of particle and nuclear physics. One key driver has been the development of the hls4ml Python package, which has made it easier to implement ML models in hardware using register transfer level (RTL) code.

The researchers in this study explored an alternative approach, using open-source embedded FPGA (eFPGA) frameworks. These customizable eFPGA fabrics can be integrated directly into a chip design, providing a more flexible pathway for implementing ML models in hardware compared to commercial FPGAs or custom ASIC blocks.

The team focused on the task of neutron/gamma classification, using data collected from an experiment with an AmBe sealed source and a Stilbene-based sensor. They investigated the performance and resource efficiency of two common ML architectures: fully-connected neural networks (fcNN) and boosted decision trees (BDT). The goal was to identify the optimal trade-offs in terms of input features, bit-resolution, sampling rate, and other hyperparameters for each model.

The key metric used to evaluate the models was the neutron efficiency, which measures how well the model can identify neutrons while keeping the number of misclassified gamma rays (a type of high-energy photon) low. The researchers aimed to achieve a gamma leakage rate of no more than 0.1%, a challenging target for this application.

The insights gained from this study will inform the design of an eFPGA fabric that can be integrated into a test chip, demonstrating the potential of this approach for implementing efficient ML models in specialized hardware.

Technical Explanation

The paper explores the growing interest and progress in implementing machine learning (ML) models in hardware, particularly within the particle and nuclear physics communities. A key driver has been the development of the hls4ml Python package, which has enabled the porting of ML models specified and trained using Python libraries to register transfer level (RTL) code. This has allowed for the deployment of these models on commercial FPGAs or custom ASIC blocks.

However, the researchers in this study have explored an alternative approach using open-source embedded FPGA (eFPGA) frameworks. These customizable eFPGA fabrics can be integrated directly into a chip design, providing a more flexible pathway for implementing ML models in hardware compared to commercial FPGAs or custom ASIC blocks.

The team focused their investigation on the task of neutron/gamma classification, using data collected from an experiment with an AmBe sealed source incident on Stilbene, which was optically coupled to an OnSemi J-series SiPM. This data was used to generate training and test sets for two common ML architectures: fully-connected neural networks (fcNN) and boosted decision trees (BDT).

The researchers explored the parameter space for eFPGA implementations of these models, investigating relevant input features, bit-resolution, sampling rate, and trade-offs in hyperparameters. The primary performance metric used was the calculated neutron efficiency at a gamma leakage of 10^-3, a challenging target for this application.

The insights gained from this study will be used to aid the specification of an eFPGA fabric, which will be integrated as part of a test chip. This demonstrates the potential of this approach for implementing efficient ML models in specialized hardware, with potential applications in financial risk management, energy optimization, and other domains requiring resource-efficient neural networks.

Critical Analysis

The paper presents a thorough exploration of the parameter space for eFPGA implementations of fcNN and BDT models for the task of neutron/gamma classification. The use of real-world data collected from an experimental setup is a strength, as it provides a realistic evaluation of the models' performance.

However, the paper does not delve into the specific details of the eFPGA fabric design or the process of integrating the ML models into the hardware. Additional information on the trade-offs and challenges involved in this integration process would have been valuable for readers interested in implementing similar solutions.

Furthermore, the paper does not provide much context on the broader applications and implications of this research beyond the specific use case of neutron/gamma classification. It would be helpful to see a discussion of how these findings could be applied to other domains or how the eFPGA approach compares to other hardware acceleration strategies, such as ASIC-based solutions or spatial acceleration on FPGAs.

Overall, the paper provides a solid technical foundation for the implementation of resource-efficient ML models in eFPGA hardware, but could benefit from additional context and discussion of the broader implications and potential applications of this research.

Conclusion

This study explored the implementation of machine learning models, specifically fully-connected neural networks and boosted decision trees, on embedded FPGA (eFPGA) hardware for the task of neutron/gamma classification. The researchers investigated the parameter space, including input features, bit-resolution, and sampling rate, to optimize the resource efficiency of these models.

The key findings and insights from this work will be used to inform the design of an eFPGA fabric that can be integrated into a test chip, demonstrating the potential of this approach for implementing efficient ML models in specialized hardware. The eFPGA framework provides a more flexible and customizable pathway for deploying ML models in hardware compared to commercial FPGAs or custom ASIC blocks.

The results of this study have implications for a range of applications, from financial risk management to energy optimization, where resource-efficient neural networks are crucial. The researchers have demonstrated the potential of eFPGA-based hardware acceleration to enable the deployment of advanced ML models in embedded and specialized systems.

This summary was produced with help from an AI and may contain inaccuracies - check out the links to read the original source documents!

Related Papers

Embedded FPGA Developments in 130nm and 28nm CMOS for Machine Learning in Particle Detector Readout

Julia Gonski, Aseem Gupta, Haoyi Jia, Hyunjoon Kim, Lorenzo Rota, Larry Ruckman, Angelo Dragone, Ryan Herbst

0

0

Embedded field programmable gate array (eFPGA) technology allows the implementation of reconfigurable logic within the design of an application-specific integrated circuit (ASIC). This approach offers the low power and efficiency of an ASIC along with the ease of FPGA configuration, particularly beneficial for the use case of machine learning in the data pipeline of next-generation collider experiments. An open-source framework called FABulous was used to design eFPGAs using 130 nm and 28 nm CMOS technology nodes, which were subsequently fabricated and verified through testing. The capability of an eFPGA to act as a front-end readout chip was assessed using simulation of high energy particles passing through a silicon pixel sensor. A machine learning-based classifier, designed for reduction of sensor data at the source, was synthesized and configured onto the eFPGA. A successful proof-of-concept was demonstrated through reproduction of the expected algorithm result on the eFPGA with perfect accuracy. Further development of the eFPGA technology and its application to collider detector readout is discussed.

7/2/2024

🧠

Resource-Efficient Neural Networks for Embedded Systems

Wolfgang Roth, Gunther Schindler, Bernhard Klein, Robert Peharz, Sebastian Tschiatschek, Holger Froning, Franz Pernkopf, Zoubin Ghahramani

0

0

While machine learning is traditionally a resource intensive task, embedded systems, autonomous navigation, and the vision of the Internet of Things fuel the interest in resource-efficient approaches. These approaches aim for a carefully chosen trade-off between performance and resource consumption in terms of computation and energy. The development of such approaches is among the major challenges in current machine learning research and key to ensure a smooth transition of machine learning technology from a scientific environment with virtually unlimited computing resources into everyday's applications. In this article, we provide an overview of the current state of the art of machine learning techniques facilitating these real-world requirements. In particular, we focus on resource-efficient inference based on deep neural networks (DNNs), the predominant machine learning models of the past decade. We give a comprehensive overview of the vast literature that can be mainly split into three non-mutually exclusive categories: (i) quantized neural networks, (ii) network pruning, and (iii) structural efficiency. These techniques can be applied during training or as post-processing, and they are widely used to reduce the computational demands in terms of memory footprint, inference speed, and energy efficiency. We also briefly discuss different concepts of embedded hardware for DNNs and their compatibility with machine learning techniques as well as potential for energy and latency reduction. We substantiate our discussion with experiments on well-known benchmark data sets using compression techniques (quantization, pruning) for a set of resource-constrained embedded systems, such as CPUs, GPUs and FPGAs. The obtained results highlight the difficulty of finding good trade-offs between resource efficiency and prediction quality.

4/9/2024

🤯

HLSTransform: Energy-Efficient Llama 2 Inference on FPGAs Via High Level Synthesis

Andy He, Darren Key, Mason Bulling, Andrew Chang, Skyler Shapiro, Everett Lee

0

0

Graphics Processing Units (GPUs) have become the leading hardware accelerator for deep learning applications and are used widely in training and inference of transformers; transformers have achieved state-of-the-art performance in many areas of machine learning and are especially used in most modern Large Language Models (LLMs). However, GPUs require large amounts of energy, which poses environmental concerns, demands high operational costs, and causes GPUs to be unsuitable for edge computing. We develop an accelerator for transformers, namely, Llama 2, an open-source state-of-the-art LLM, using high level synthesis (HLS) on Field Programmable Gate Arrays (FPGAs). HLS allows us to rapidly prototype FPGA designs without writing code at the register-transfer level (RTL). We name our method HLSTransform, and the FPGA designs we synthesize with HLS achieve up to a 12.75x reduction and 8.25x reduction in energy used per token on the Xilinx Virtex UltraScale+ VU9P FPGA compared to an Intel Xeon Broadwell E5-2686 v4 CPU and NVIDIA RTX 3090 GPU respectively, while increasing inference speeds by up to 2.46x compared to CPU and maintaining 0.53x the speed of an RTX 3090 GPU despite the GPU's 4 times higher base clock rate. With the lack of existing open-source FPGA accelerators for transformers, we open-source our code and document our steps for synthesis. We hope this work will serve as a step in democratizing the use of FPGAs in transformer inference and inspire research into energy-efficient inference methods as a whole. The code can be found on https://github.com/HLSTransform/submission.

5/3/2024

Understanding the Potential of FPGA-Based Spatial Acceleration for Large Language Model Inference

Hongzheng Chen, Jiahao Zhang, Yixiao Du, Shaojie Xiang, Zichao Yue, Niansong Zhang, Yaohui Cai, Zhiru Zhang

0

0

Recent advancements in large language models (LLMs) boasting billions of parameters have generated a significant demand for efficient deployment in inference workloads. The majority of existing approaches rely on temporal architectures that reuse hardware units for different network layers and operators. However, these methods often encounter challenges in achieving low latency due to considerable memory access overhead. This paper investigates the feasibility and potential of model-specific spatial acceleration for LLM inference on FPGAs. Our approach involves the specialization of distinct hardware units for specific operators or layers, facilitating direct communication between them through a dataflow architecture while minimizing off-chip memory accesses. We introduce a comprehensive analytical model for estimating the performance of a spatial LLM accelerator, taking into account the on-chip compute and memory resources available on an FPGA. Through our analysis, we can determine the scenarios in which FPGA-based spatial acceleration can outperform its GPU-based counterpart. To enable more productive implementations of an LLM model on FPGAs, we further provide a library of high-level synthesis (HLS) kernels that are composable and reusable. This library will be made available as open-source. To validate the effectiveness of both our analytical model and HLS library, we have implemented BERT and GPT2 on an AMD Alveo U280 FPGA device. Experimental results demonstrate our approach can achieve up to 13.4x speedup when compared to previous FPGA-based accelerators for the BERT model. For GPT generative inference, we attain a 2.2x speedup compared to DFX, an FPGA overlay, in the prefill stage, while achieving a 1.9x speedup and a 5.7x improvement in energy efficiency compared to the NVIDIA A100 GPU in the decode stage.

4/9/2024