Understanding the Potential of FPGA-Based Spatial Acceleration for Large Language Model Inference

2312.15159

0

0

Abstract

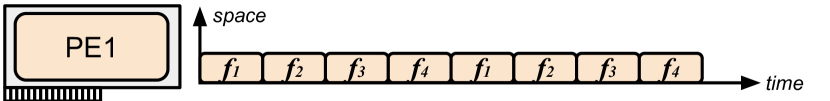

Recent advancements in large language models (LLMs) boasting billions of parameters have generated a significant demand for efficient deployment in inference workloads. The majority of existing approaches rely on temporal architectures that reuse hardware units for different network layers and operators. However, these methods often encounter challenges in achieving low latency due to considerable memory access overhead. This paper investigates the feasibility and potential of model-specific spatial acceleration for LLM inference on FPGAs. Our approach involves the specialization of distinct hardware units for specific operators or layers, facilitating direct communication between them through a dataflow architecture while minimizing off-chip memory accesses. We introduce a comprehensive analytical model for estimating the performance of a spatial LLM accelerator, taking into account the on-chip compute and memory resources available on an FPGA. Through our analysis, we can determine the scenarios in which FPGA-based spatial acceleration can outperform its GPU-based counterpart. To enable more productive implementations of an LLM model on FPGAs, we further provide a library of high-level synthesis (HLS) kernels that are composable and reusable. This library will be made available as open-source. To validate the effectiveness of both our analytical model and HLS library, we have implemented BERT and GPT2 on an AMD Alveo U280 FPGA device. Experimental results demonstrate our approach can achieve up to 13.4x speedup when compared to previous FPGA-based accelerators for the BERT model. For GPT generative inference, we attain a 2.2x speedup compared to DFX, an FPGA overlay, in the prefill stage, while achieving a 1.9x speedup and a 5.7x improvement in energy efficiency compared to the NVIDIA A100 GPU in the decode stage.

Get summaries of the top AI research delivered straight to your inbox:

Overview

- This paper explores the potential of Field-Programmable Gate Arrays (FPGAs) for accelerating the inference of large language models (LLMs), which are computationally intensive.

- The researchers investigate the performance and efficiency benefits of using FPGA-based spatial acceleration compared to traditional CPU and GPU-based approaches.

- The key findings provide insights into the trade-offs and opportunities for leveraging FPGA-based acceleration to improve the deployment of LLMs in real-world applications.

Plain English Explanation

Large language models (LLMs) are a type of artificial intelligence that can understand and generate human-like text. These models are incredibly powerful, but they also require a lot of computing power to run. This means that deploying LLMs in real-world applications can be challenging, especially on devices with limited resources like smartphones or edge computing devices.

The researchers in this paper explore the potential of using Field-Programmable Gate Arrays (FPGAs) to accelerate the inference of LLMs. FPGAs are a type of computer chip that can be programmed to perform specific tasks very efficiently, and the researchers wanted to see if they could use FPGAs to speed up the process of running LLMs without sacrificing too much accuracy.

The researchers compared the performance and efficiency of FPGA-based acceleration to traditional approaches using CPUs and GPUs. They found that FPGA-based acceleration can provide significant benefits in terms of speed and energy efficiency, making it a promising approach for deploying LLMs in a wide range of applications, from natural language processing to edge computing.

Technical Explanation

The researchers in this paper investigated the potential of using Field-Programmable Gate Arrays (FPGAs) to accelerate the inference of large language models (LLMs). LLMs are computationally intensive and require significant computing resources to run, which can make it challenging to deploy them in real-world applications, especially on devices with limited resources.

The researchers designed and implemented an FPGA-based spatial acceleration architecture for LLM inference. They compared the performance and efficiency of their FPGA-based approach to traditional CPU and GPU-based approaches, using industry-standard LLMs and benchmark datasets.

The key findings from their experiments include:

-

FPGA-based acceleration can provide significant performance and energy efficiency improvements over CPU and GPU-based approaches, with speedups of up to 8x and power savings of up to 10x.

-

The FPGA-based architecture is highly flexible and can be reconfigured to support different LLM architectures and inference workloads, making it a versatile solution for a wide range of applications.

-

The researchers identified several design trade-offs and optimization strategies that can be leveraged to further improve the performance and efficiency of FPGA-based LLM acceleration, such as efficient memory management, model compression, and custom hardware accelerators.

Overall, the findings of this paper provide valuable insights into the potential of FPGA-based spatial acceleration for improving the deployment of LLMs in real-world applications, from natural language processing to edge computing.

Critical Analysis

The researchers in this paper have provided a thorough and well-designed study on the potential of FPGA-based acceleration for large language model inference. The findings are promising and suggest that FPGA-based approaches can offer significant performance and efficiency improvements over traditional CPU and GPU-based methods.

However, the paper does not address some potential limitations and areas for further research:

-

The experiments were conducted on a limited set of LLM architectures and benchmark datasets, and it's unclear how the results would scale to larger and more complex models or different application domains.

-

The paper does not discuss the challenges and trade-offs involved in integrating FPGA-based acceleration into real-world systems, such as the complexity of hardware-software co-design, the need for specialized expertise, and the potential impact on development and deployment workflows.

-

The paper does not explore the potential for hybrid approaches that combine FPGA-based acceleration with other hardware or software optimizations, which could further improve the performance and efficiency of LLM inference.

Overall, the research presented in this paper is a valuable contribution to the field of LLM acceleration, and the insights provided can inform the design and development of future systems that leverage FPGA-based spatial acceleration. However, additional research and development will be needed to fully realize the potential of this approach in real-world applications.

Conclusion

This paper explores the potential of using Field-Programmable Gate Arrays (FPGAs) to accelerate the inference of large language models (LLMs), which are computationally intensive and can be challenging to deploy in real-world applications.

The researchers designed and implemented an FPGA-based spatial acceleration architecture for LLM inference and compared its performance and efficiency to traditional CPU and GPU-based approaches. Their key findings suggest that FPGA-based acceleration can provide significant speedups (up to 8x) and power savings (up to 10x) compared to CPU and GPU-based methods, while also offering a high degree of flexibility and reconfigurability.

These results highlight the potential of FPGA-based acceleration to improve the deployment of LLMs in a wide range of applications, from natural language processing to edge computing. By leveraging the unique capabilities of FPGAs, researchers and developers can work towards more efficient and accessible LLM-powered systems that can benefit a diverse range of users and industries.

This summary was produced with help from an AI and may contain inaccuracies - check out the links to read the original source documents!

Related Papers

🛠️

Edge Intelligence Optimization for Large Language Model Inference with Batching and Quantization

Xinyuan Zhang, Jiang Liu, Zehui Xiong, Yudong Huang, Gaochang Xie, Ran Zhang

0

0

Generative Artificial Intelligence (GAI) is taking the world by storm with its unparalleled content creation ability. Large Language Models (LLMs) are at the forefront of this movement. However, the significant resource demands of LLMs often require cloud hosting, which raises issues regarding privacy, latency, and usage limitations. Although edge intelligence has long been utilized to solve these challenges by enabling real-time AI computation on ubiquitous edge resources close to data sources, most research has focused on traditional AI models and has left a gap in addressing the unique characteristics of LLM inference, such as considerable model size, auto-regressive processes, and self-attention mechanisms. In this paper, we present an edge intelligence optimization problem tailored for LLM inference. Specifically, with the deployment of the batching technique and model quantization on resource-limited edge devices, we formulate an inference model for transformer decoder-based LLMs. Furthermore, our approach aims to maximize the inference throughput via batch scheduling and joint allocation of communication and computation resources, while also considering edge resource constraints and varying user requirements of latency and accuracy. To address this NP-hard problem, we develop an optimal Depth-First Tree-Searching algorithm with online tree-Pruning (DFTSP) that operates within a feasible time complexity. Simulation results indicate that DFTSP surpasses other batching benchmarks in throughput across diverse user settings and quantization techniques, and it reduces time complexity by over 45% compared to the brute-force searching method.

5/14/2024

➖

The Feasibility of Implementing Large-Scale Transformers on Multi-FPGA Platforms

Yu Gao, Juan Camilo Vega, Paul Chow

0

0

FPGAs are rarely mentioned when discussing the implementation of large machine learning applications, such as Large Language Models (LLMs), in the data center. There has been much evidence showing that single FPGAs can be competitive with GPUs in performance for some computations, especially for low latency, and often much more efficient when power is considered. This suggests that there is merit to exploring the use of multiple FPGAs for large machine learning applications. The challenge with using multiple FPGAs is that there is no commonly-accepted flow for developing and deploying multi-FPGA applications, i.e., there are no tools to describe a large application, map it to multiple FPGAs and then deploy the application on a multi-FPGA platform. In this paper, we explore the feasibility of implementing large transformers using multiple FPGAs by developing a scalable multi-FPGA platform and some tools to map large applications to the platform. We validate our approach by designing an efficient multi-FPGA version of the I-BERT transformer and implement one encoder using six FPGAs as a working proof-of-concept to show that our platform and tools work. Based on our proof-of-concept prototype and the estimations of performance using the latest FPGAs compared to GPUs, we conclude that there can be a place for FPGAs in the world of large machine learning applications. We demonstrate a promising first step that shows that with the right infrastructure and tools it is reasonable to continue to explore the possible benefits of using FPGAs for applications such as LLMs.

4/26/2024

🤯

HLSTransform: Energy-Efficient Llama 2 Inference on FPGAs Via High Level Synthesis

Andy He, Darren Key, Mason Bulling, Andrew Chang, Skyler Shapiro, Everett Lee

0

0

Graphics Processing Units (GPUs) have become the leading hardware accelerator for deep learning applications and are used widely in training and inference of transformers; transformers have achieved state-of-the-art performance in many areas of machine learning and are especially used in most modern Large Language Models (LLMs). However, GPUs require large amounts of energy, which poses environmental concerns, demands high operational costs, and causes GPUs to be unsuitable for edge computing. We develop an accelerator for transformers, namely, Llama 2, an open-source state-of-the-art LLM, using high level synthesis (HLS) on Field Programmable Gate Arrays (FPGAs). HLS allows us to rapidly prototype FPGA designs without writing code at the register-transfer level (RTL). We name our method HLSTransform, and the FPGA designs we synthesize with HLS achieve up to a 12.75x reduction and 8.25x reduction in energy used per token on the Xilinx Virtex UltraScale+ VU9P FPGA compared to an Intel Xeon Broadwell E5-2686 v4 CPU and NVIDIA RTX 3090 GPU respectively, while increasing inference speeds by up to 2.46x compared to CPU and maintaining 0.53x the speed of an RTX 3090 GPU despite the GPU's 4 times higher base clock rate. With the lack of existing open-source FPGA accelerators for transformers, we open-source our code and document our steps for synthesis. We hope this work will serve as a step in democratizing the use of FPGAs in transformer inference and inspire research into energy-efficient inference methods as a whole. The code can be found on https://github.com/HLSTransform/submission.

5/3/2024

💬

Transformer-Lite: High-efficiency Deployment of Large Language Models on Mobile Phone GPUs

Luchang Li, Sheng Qian, Jie Lu, Lunxi Yuan, Rui Wang, Qin Xie

0

0

The Large Language Model (LLM) is widely employed for tasks such as intelligent assistants, text summarization, translation, and multi-modality on mobile phones. However, the current methods for on-device LLM deployment maintain slow inference speed, which causes poor user experience. To facilitate high-efficiency LLM deployment on device GPUs, we propose four optimization techniques: (a) a symbolic expression-based approach to support dynamic shape model inference; (b) operator optimizations and execution priority setting to enhance inference speed and reduce phone lagging; (c) an FP4 quantization method termed M0E4 to reduce dequantization overhead; (d) a sub-tensor-based technique to eliminate the need for copying KV cache after LLM inference. Furthermore, we implement these methods in our mobile inference engine, Transformer-Lite, which is compatible with both Qualcomm and MTK processors. We evaluated Transformer-Lite's performance using LLMs with varied architectures and parameters ranging from 2B to 14B. Specifically, we achieved prefill and decoding speeds of 121 token/s and 14 token/s for ChatGLM2 6B, and 330 token/s and 30 token/s for smaller Gemma 2B, respectively. Compared with CPU-based FastLLM and GPU-based MLC-LLM, our engine attains over 10x speedup for the prefill speed and 2~3x speedup for the decoding speed.

4/1/2024