An Open-Source Fast Parallel Routing Approach for Commercial FPGAs

0

Sign in to get full access

Overview

- This paper presents a new open-source, fast, and parallel routing approach for commercial field-programmable gate arrays (FPGAs).

- The proposed method aims to improve the performance and scalability of FPGA routing compared to existing solutions.

- The authors demonstrate the effectiveness of their approach through experiments on various FPGA benchmarks and showcase its advantages over alternative routing techniques.

Plain English Explanation

FPGAs are a type of computer chip that can be reconfigured to perform different functions. They are used in a wide range of applications, from video processing to cryptocurrency mining. However, the process of "routing" the connections on an FPGA can be computationally intensive and time-consuming, which can limit the performance and scalability of FPGA-based systems.

The researchers in this paper have developed a new open-source routing approach that is both faster and able to take advantage of parallel processing. This means that their method can route the connections on an FPGA much more quickly than traditional approaches, without sacrificing the quality of the routing.

The key idea behind their approach is to break down the routing problem into smaller, independent sub-problems that can be solved in parallel. This allows them to leverage the power of modern multi-core processors to speed up the routing process. Additionally, their method is designed to be more efficient and scalable than existing routing algorithms, making it well-suited for use with large and complex FPGA designs.

The researchers have evaluated their approach on a variety of FPGA benchmarks and have demonstrated that it outperforms other state-of-the-art routing techniques in terms of both runtime and the quality of the resulting routing solutions. This suggests that their method could be a valuable tool for FPGA designers and researchers who are looking to improve the performance and scalability of their FPGA-based systems.

Technical Explanation

The paper presents a new open-source, fast, and parallel routing approach for commercial FPGAs. The proposed method, called [link text]https://aimodels.fyi/papers/arxiv/achieving-high-performance-fault-tolerant-routing-hyperx[/link], aims to improve the performance and scalability of FPGA routing compared to existing solutions.

The key contributions of the paper are:

-

Parallel Routing Algorithm: The authors develop a parallel routing algorithm that decomposes the global routing problem into smaller, independent sub-problems that can be solved concurrently. This allows them to leverage the power of modern multi-core processors to speed up the routing process.

-

Efficient Routing Heuristics: The paper introduces several novel routing heuristics that are designed to be more efficient and scalable than existing algorithms. These heuristics are used to guide the parallel routing process and ensure the quality of the resulting routing solutions.

-

Comprehensive Evaluation: The researchers evaluate their approach on a wide range of FPGA benchmarks and compare its performance to state-of-the-art routing techniques. They demonstrate that their method outperforms alternative approaches in terms of runtime and the quality of the routing solutions.

The parallel routing algorithm works by partitioning the FPGA's routing resources into multiple, independent regions that can be routed concurrently. The algorithm uses efficient heuristics to guide the routing process within each region, and it employs a novel technique for handling the dependencies between regions to ensure the overall quality of the routing solution.

The experimental results show that the proposed approach can achieve significant speedups over existing routing algorithms, with improvements of up to 3x in runtime while maintaining comparable or better quality of the routing solutions. This suggests that the researchers' method could be a valuable tool for FPGA designers and researchers who are looking to improve the performance and scalability of their FPGA-based systems.

Critical Analysis

The paper presents a thorough and well-designed study of the researchers' parallel routing approach for commercial FPGAs. The authors have clearly put a lot of thought and effort into developing their algorithm and evaluating its performance on a wide range of benchmarks.

One potential limitation of the study is that it focuses primarily on the runtime and quality of the routing solutions, without delving deeply into the energy efficiency or other practical considerations of their approach. Additionally, while the researchers have demonstrated the effectiveness of their method on a variety of FPGA benchmarks, it would be interesting to see how it performs on real-world FPGA designs and applications.

Furthermore, the paper does not provide much insight into the specific tradeoffs or design decisions made during the development of the parallel routing algorithm. It would be helpful to have a more detailed discussion of the algorithm's strengths, weaknesses, and the factors that influenced the researchers' choices.

Despite these minor caveats, the paper presents a compelling and well-executed study that makes a significant contribution to the field of FPGA routing. The researchers' open-source implementation of their approach [link text]https://aimodels.fyi/papers/arxiv/study-workload-interference-intelligent-routing-dragonfly[/link] is a valuable resource for the FPGA research community, and their findings could have important implications for the design and optimization of FPGA-based systems.

Conclusion

This paper introduces a novel open-source, fast, and parallel routing approach for commercial FPGAs. The researchers have developed a parallel routing algorithm that decomposes the global routing problem into smaller, independent sub-problems that can be solved concurrently, leveraging the power of modern multi-core processors to improve runtime.

The proposed method also incorporates efficient routing heuristics that enhance the quality of the resulting routing solutions. Through comprehensive experiments on a variety of FPGA benchmarks, the authors have demonstrated that their approach can achieve significant speedups over existing routing algorithms while maintaining comparable or better routing quality.

The researchers' work has the potential to make a significant impact on the field of FPGA design and optimization, as their open-source implementation [link text]https://aimodels.fyi/papers/arxiv/low-latency-video-conferencing-via-optimized-packet[/link] could become a valuable tool for FPGA designers and researchers. The insights and techniques presented in this paper may also inspire further advancements in the area of parallel and scalable FPGA routing, ultimately leading to more efficient and performant FPGA-based systems.

This summary was produced with help from an AI and may contain inaccuracies - check out the links to read the original source documents!

Related Papers

0

An Open-Source Fast Parallel Routing Approach for Commercial FPGAs

Xinshi Zang, Wenhao Lin, Shiju Lin, Jinwei Liu, Evangeline F. Y. Young

In the face of escalating complexity and size of contemporary FPGAs and circuits, routing emerges as a pivotal and time-intensive phase in FPGA compilation flows. In response to this challenge, we present an open-source parallel routing methodology designed to expedite routing procedures for commercial FPGAs. Our approach introduces a novel recursive partitioning ternary tree to augment the parallelism of multi-net routing. Additionally, we propose a hybrid updating strategy for congestion coefficients within the routing cost function to accelerate congestion resolution in negotiation-based routing algorithms. Evaluation on public benchmarks from the FPGA24 routing contest demonstrates the efficacy of our parallel router. It achieves a 2x speedup compared to the academic serial router RWRoute. Furthermore, when compared to the industry-standard tool Vivado, our approach not only delivers a 2x acceleration but also yields a notable 31% enhancement in critical-path wirelength.

Read more7/2/2024

🧠

0

Achieving High-Performance Fault-Tolerant Routing in HyperX Interconnection Networks

Crist'obal Camarero, Alejandro Cano, Carmen Mart'inez, Ram'on Beivide

Interconnection networks are key actors that condition the performance of current large datacenter and supercomputer systems. Both topology and routing are critical aspects that must be carefully considered for a competitive system network design. Moreover, when daily failures are expected, this tandem should exhibit resilience and robustness. Low-diameter networks, including HyperX, are cheaper than typical Fat Trees. But, to be really competitive, they have to employ evolved routing algorithms to both balance traffic and tolerate failures. In this paper, SurePath, an efficient fault-tolerant routing mechanism for HyperX topology is introduced and evaluated. SurePath leverages routes provided by standard routing algorithms and a deadlock avoidance mechanism based on an Up/Down escape subnetwork. This mechanism not only prevents deadlock but also allows for a fault-tolerant solution for these networks. SurePath is thoroughly evaluated in the paper under different traffic patterns, showing no performance degradation under extremely faulty scenarios.

Read more4/9/2024

⚙️

0

FlexCross: High-Speed and Flexible Packet Processing via a Crosspoint-Queued Crossbar

Klajd Zyla, Marco Liess, Thomas Wild, Andreas Herkersdorf

The fast pace at which new online services emerge leads to a rapid surge in the volume of network traffic. A recent approach that the research community has proposed to tackle this issue is in-network computing, which means that network devices perform more computations than before. As a result, processing demands become more varied, creating the need for flexible packet-processing architectures. State-of-the-art approaches provide a high degree of flexibility at the expense of performance for complex applications, or they ensure high performance but only for specific use cases. In order to address these limitations, we propose FlexCross. This flexible packet-processing design can process network traffic with diverse processing requirements at over 100 Gbit/s on FPGAs. Our design contains a crosspoint-queued crossbar that enables the execution of complex applications by forwarding incoming packets to the required processing engines in the specified sequence. The crossbar consists of distributed logic blocks that route incoming packets to the specified targets and resolve contentions for shared resources, as well as memory blocks for packet buffering. We implemented a prototype of FlexCross in Verilog and evaluated it via cycle-accurate register-transfer level simulations. We also conducted test runs with real-world network traffic on an FPGA. The evaluation results demonstrate that FlexCross outperforms state-of-the-art flexible packet-processing designs for different traffic loads and scenarios. The synthesis results show that our prototype consumes roughly 21% of the resources on a Virtex XCU55 UltraScale+ FPGA.

Read more7/12/2024

0

Online Convex Optimization for On-Board Routing in High-Throughput Satellites

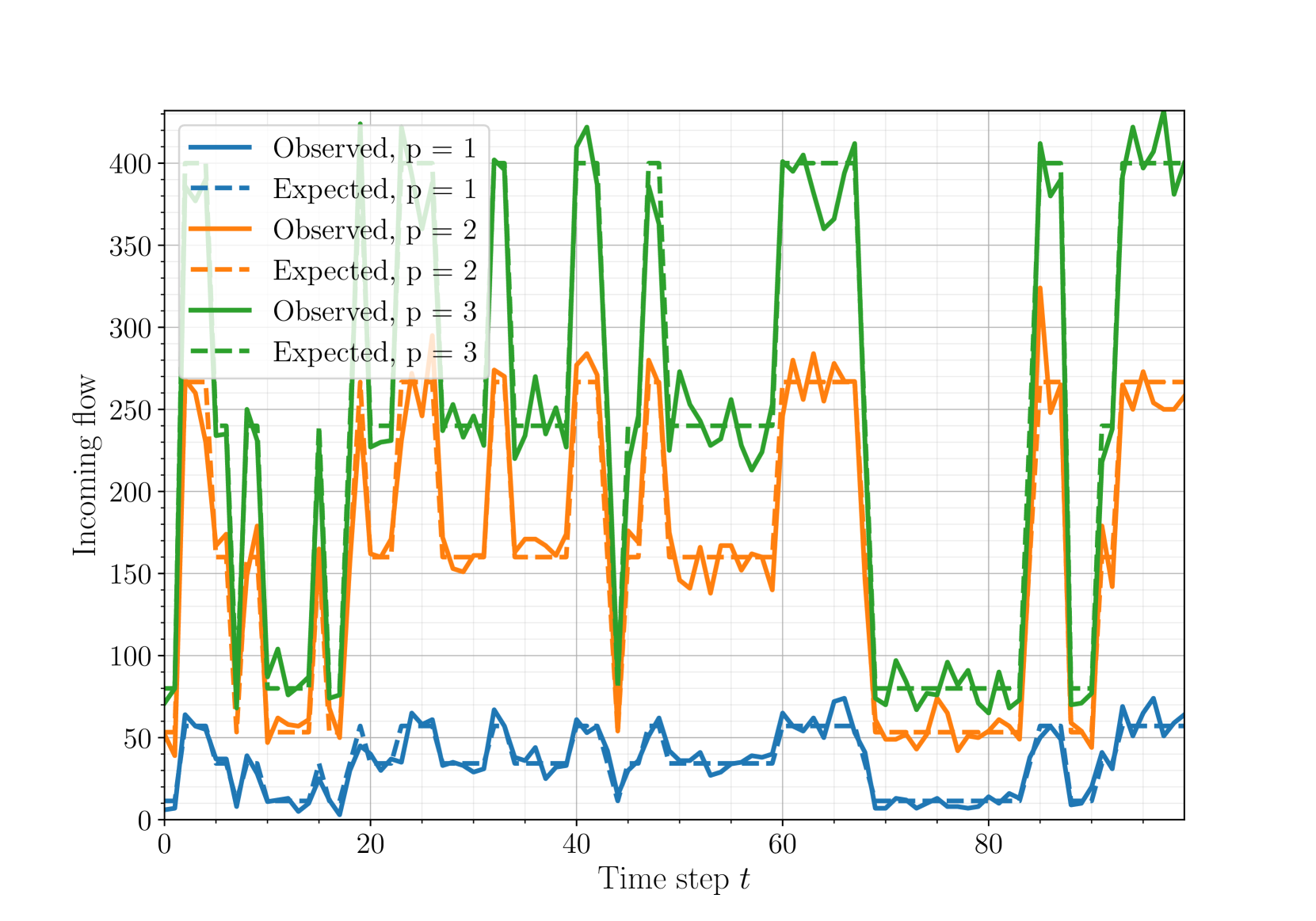

Olivier B'elanger, Jean-Luc Lupien, Olfa Ben Yahia, St'ephane Martel, Antoine Lesage-Landry, Gunes Karabulut Kurt

The rise in low Earth orbit (LEO) satellite Internet services has led to increasing demand, often exceeding available data rates and compromising the quality of service. While deploying more satellites offers a short-term fix, designing higher-performance satellites with enhanced transmission capabilities provides a more sustainable solution. Achieving the necessary high capacity requires interconnecting multiple modem banks within a satellite payload. However, there is a notable gap in research on internal packet routing within extremely high-throughput satellites. To address this, we propose a real-time optimal flow allocation and priority queue scheduling method using online convex optimization-based model predictive control. We model the problem as a multi-commodity flow instance and employ an online interior-point method to solve the routing and scheduling optimization iteratively. This approach minimizes packet loss and supports real-time rerouting with low computational overhead. Our method is tested in simulation on a next-generation extremely high-throughput satellite model, demonstrating its effectiveness compared to a reference batch optimization and to traditional methods.

Read more9/4/2024