Overcoming the Limitations of Layer Synchronization in Spiking Neural Networks

0

Sign in to get full access

Overview

- Spiking neural networks (SNNs) are a type of artificial neural network that aim to mimic the behavior of biological neurons.

- One key challenge with SNNs is the issue of layer synchronization, where neurons in different layers fire at different times, leading to inefficient computation.

- This paper proposes a novel approach called "Overcoming the Limitations of Layer Synchronization in Spiking Neural Networks" to address this problem.

Plain English Explanation

The paper explores a solution to a problem that arises in a particular type of artificial intelligence called spiking neural networks (SNNs). SNNs are designed to work more like the human brain, where information is transmitted through electrical "spikes" between neurons.

One issue with SNNs is that the neurons in different layers of the network can fire (or "spike") at different times. This lack of synchronization can make the computation less efficient. The researchers in this paper have developed a new approach to help overcome this challenge of layer synchronization in SNNs.

By addressing this technical limitation, the researchers aim to improve the performance and efficiency of spiking neural networks, which could lead to advancements in areas like neuromorphic computing and energy-efficient AI systems.

Technical Explanation

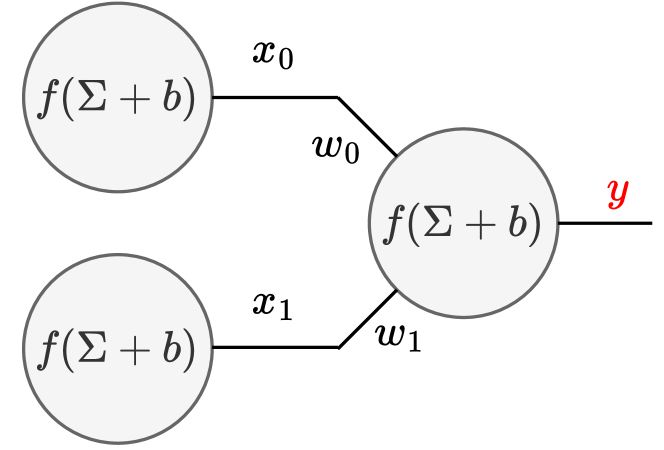

The paper presents a novel technique to overcome the limitations of layer synchronization in spiking neural networks. Spiking neural networks are designed to mimic the behavior of biological neurons, where information is transmitted through discrete electrical impulses or "spikes" rather than continuous activations.

One key challenge with SNNs is the issue of layer synchronization. Due to the asynchronous nature of spiking, neurons in different layers of the network can fire at different times, leading to inefficient computation and information processing.

The proposed approach aims to address this problem by introducing a hardware-aware training method that accounts for the temporal dynamics of spiking neurons. The technique involves encoding information in the timing of spikes and leveraging the inherent temporal characteristics of SNNs to enable more efficient event-based computation.

Critical Analysis

The paper acknowledges that while the proposed approach helps overcome the limitations of layer synchronization, there are still some caveats and areas for further research. For example, the technique may be sensitive to variations in neuronal and synaptic parameters, and the impact on overall network performance and energy efficiency requires more extensive evaluation.

Additionally, the paper does not address the potential trade-offs between the increased complexity of the training process and the benefits of improved layer synchronization. Further research is needed to fully understand the implications and practical applications of this approach.

Conclusion

This paper presents a novel technique to address the challenge of layer synchronization in spiking neural networks. By encoding information in the timing of spikes and leveraging the temporal dynamics of SNNs, the researchers have developed a hardware-aware training method that can improve the efficiency of event-based computation in these types of neuromorphic systems.

The proposed solution has the potential to advance the field of spiking neural networks and contribute to the development of more energy-efficient and biologically-inspired AI systems. However, further research is needed to fully understand the implications and practical applicability of this approach.

This summary was produced with help from an AI and may contain inaccuracies - check out the links to read the original source documents!

Related Papers

0

Overcoming the Limitations of Layer Synchronization in Spiking Neural Networks

Roel Koopman, Amirreza Yousefzadeh, Mahyar Shahsavari, Guangzhi Tang, Manolis Sifalakis

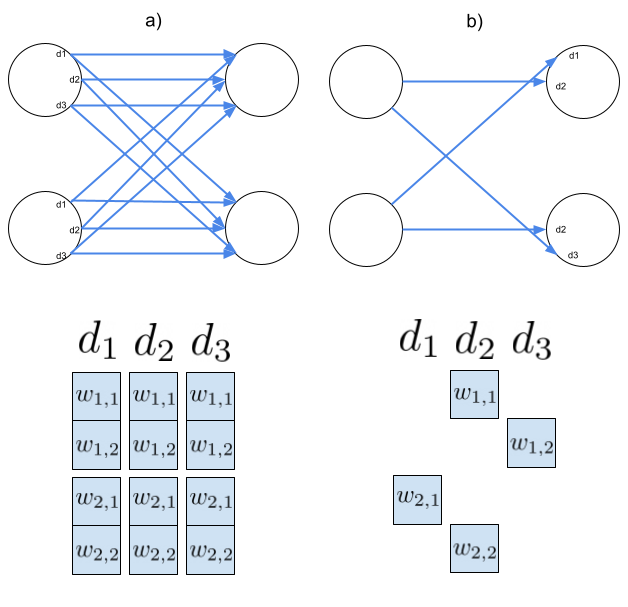

Currently, neural-network processing in machine learning applications relies on layer synchronization, whereby neurons in a layer aggregate incoming currents from all neurons in the preceding layer, before evaluating their activation function. This is practiced even in artificial Spiking Neural Networks (SNNs), which are touted as consistent with neurobiology, in spite of processing in the brain being, in fact asynchronous. A truly asynchronous system however would allow all neurons to evaluate concurrently their threshold and emit spikes upon receiving any presynaptic current. Omitting layer synchronization is potentially beneficial, for latency and energy efficiency, but asynchronous execution of models previously trained with layer synchronization may entail a mismatch in network dynamics and performance. We present a study that documents and quantifies this problem in three datasets on our simulation environment that implements network asynchrony, and we show that models trained with layer synchronization either perform sub-optimally in absence of the synchronization, or they will fail to benefit from any energy and latency reduction, when such a mechanism is in place. We then make ends meet and address the problem with unlayered backprop, a novel backpropagation-based training method, for learning models suitable for asynchronous processing. We train with it models that use different neuron execution scheduling strategies, and we show that although their neurons are more reactive, these models consistently exhibit lower overall spike density (up to 50%), reach a correct decision faster (up to 2x) without integrating all spikes, and achieve superior accuracy (up to 10% higher). Our findings suggest that asynchronous event-based (neuromorphic) AI computing is indeed more efficient, but we need to seriously rethink how we train our SNN models, to benefit from it.

Read more8/12/2024

0

An Asynchronous Multi-core Accelerator for SNN inference

Zhuo Chen, De Ma, Xiaofei Jin, Qinghui Xing, Ouwen Jin, Xin Du, Shuibing He, Gang Pan

Spiking Neural Networks (SNNs) are extensively utilized in brain-inspired computing and neuroscience research. To enhance the speed and energy efficiency of SNNs, several many-core accelerators have been developed. However, maintaining the accuracy of SNNs often necessitates frequent explicit synchronization among all cores, which presents a challenge to overall efficiency. In this paper, we propose an asynchronous architecture for Spiking Neural Networks (SNNs) that eliminates the need for inter-core synchronization, thus enhancing speed and energy efficiency. This approach leverages the pre-determined dependencies of neuromorphic cores established during compilation. Each core is equipped with a scheduler that monitors the status of its dependencies, allowing it to safely advance to the next timestep without waiting for other cores. This eliminates the necessity for global synchronization and minimizes core waiting time despite inherent workload imbalances. Comprehensive evaluations using five different SNN workloads show that our architecture achieves a 1.86x speedup and a 1.55x increase in energy efficiency compared to state-of-the-art synchronization architectures.

Read more7/31/2024

🧠

0

Spike-based computation using classical recurrent neural networks

Florent De Geeter (Montefiore Institute, University of Li`ege, Li`ege, Belgium), Damien Ernst (Montefiore Institute, University of Li`ege, Li`ege, Belgium, LTCI, T'el'ecom Paris, Institut Polytechnique de Paris, France), Guillaume Drion (Montefiore Institute, University of Li`ege, Li`ege, Belgium)

Spiking neural networks are a type of artificial neural networks in which communication between neurons is only made of events, also called spikes. This property allows neural networks to make asynchronous and sparse computations and therefore drastically decrease energy consumption when run on specialised hardware. However, training such networks is known to be difficult, mainly due to the non-differentiability of the spike activation, which prevents the use of classical backpropagation. This is because state-of-the-art spiking neural networks are usually derived from biologically-inspired neuron models, to which are applied machine learning methods for training. Nowadays, research about spiking neural networks focuses on the design of training algorithms whose goal is to obtain networks that compete with their non-spiking version on specific tasks. In this paper, we attempt the symmetrical approach: we modify the dynamics of a well-known, easily trainable type of recurrent neural network to make it event-based. This new RNN cell, called the Spiking Recurrent Cell, therefore communicates using events, i.e. spikes, while being completely differentiable. Vanilla backpropagation can thus be used to train any network made of such RNN cell. We show that this new network can achieve performance comparable to other types of spiking networks in the MNIST benchmark and its variants, the Fashion-MNIST and the Neuromorphic-MNIST. Moreover, we show that this new cell makes the training of deep spiking networks achievable.

Read more5/7/2024

0

Hardware-aware training of models with synaptic delays for digital event-driven neuromorphic processors

Alberto Patino-Saucedo, Roy Meijer, Amirreza Yousefzadeh, Manil-Dev Gomony, Federico Corradi, Paul Detteter, Laura Garrido-Regife, Bernabe Linares-Barranco, Manolis Sifalakis

Configurable synaptic delays are a basic feature in many neuromorphic neural network hardware accelerators. However, they have been rarely used in model implementations, despite their promising impact on performance and efficiency in tasks that exhibit complex (temporal) dynamics, as it has been unclear how to optimize them. In this work, we propose a framework to train and deploy, in digital neuromorphic hardware, highly performing spiking neural network models (SNNs) where apart from the synaptic weights, the per-synapse delays are also co-optimized. Leveraging spike-based back-propagation-through-time, the training accounts for both platform constraints, such as synaptic weight precision and the total number of parameters per core, as a function of the network size. In addition, a delay pruning technique is used to reduce memory footprint with a low cost in performance. We evaluate trained models in two neuromorphic digital hardware platforms: Intel Loihi and Imec Seneca. Loihi offers synaptic delay support using the so-called Ring-Buffer hardware structure. Seneca does not provide native hardware support for synaptic delays. A second contribution of this paper is therefore a novel area- and memory-efficient hardware structure for acceleration of synaptic delays, which we have integrated in Seneca. The evaluated benchmark involves several models for solving the SHD (Spiking Heidelberg Digits) classification task, where minimal accuracy degradation during the transition from software to hardware is demonstrated. To our knowledge, this is the first work showcasing how to train and deploy hardware-aware models parameterized with synaptic delays, on multicore neuromorphic hardware accelerators.

Read more4/17/2024