Profiling quantum circuits for their efficient execution on single- and multi-core architectures

0

Sign in to get full access

Overview

- This paper explores techniques for profiling and optimizing quantum circuit execution on both single-core and multi-core architectures.

- The researchers investigate methods to analyze the performance characteristics of quantum circuits and identify opportunities for parallelization and hardware-specific optimizations.

- The goal is to enable more efficient execution of quantum algorithms on classical computing hardware, which is an important step towards practical quantum computing.

Plain English Explanation

Quantum computers have the potential to solve certain problems much faster than classical computers. However, building large-scale quantum computers is extremely challenging. In the meantime, researchers are exploring ways to run quantum algorithms on classical computers, which are more widely available.

This paper focuses on profiling quantum circuits - breaking them down and analyzing their performance characteristics. The researchers want to understand how quantum circuits can be executed most efficiently on classical hardware, both on single-core and multi-core systems.

By studying the properties of quantum circuits, the researchers aim to identify opportunities to parallelize their execution and optimize them for specific hardware architectures. This could lead to faster and more efficient quantum algorithm implementations on classical computers, bringing us closer to practical quantum computing applications.

The paper presents techniques for analyzing the structure and behavior of quantum circuits in order to run them as efficiently as possible on today's computing hardware. This is an important step towards bridging the gap between theoretical quantum algorithms and real-world implementations.

Technical Explanation

The paper begins by providing background on quantum computing and the challenges of executing quantum circuits on classical hardware. The researchers note that while quantum algorithms have the potential for exponential speedups, realizing these benefits requires carefully orchestrating the execution of quantum circuits.

The key contributions of the paper are:

-

Developing techniques to profile the performance characteristics of quantum circuits, including their parallelization potential and hardware-specific optimization opportunities.

-

Demonstrating the application of these profiling methods on several benchmark quantum circuits, both on single-core and multi-core systems.

-

Analyzing the profiling results to identify opportunities for parallelization and hardware-specific optimizations that can improve the efficiency of quantum circuit execution on classical computers.

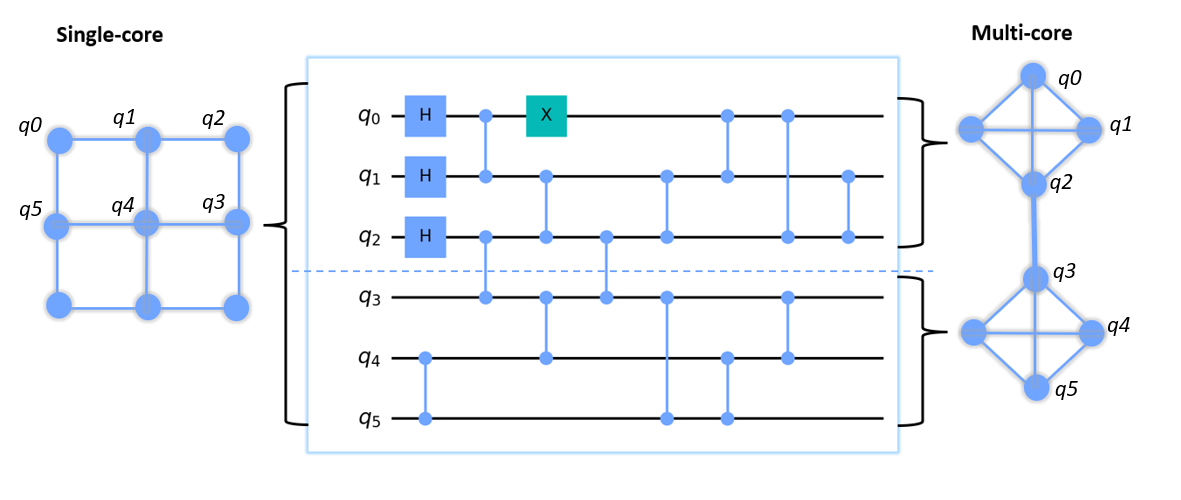

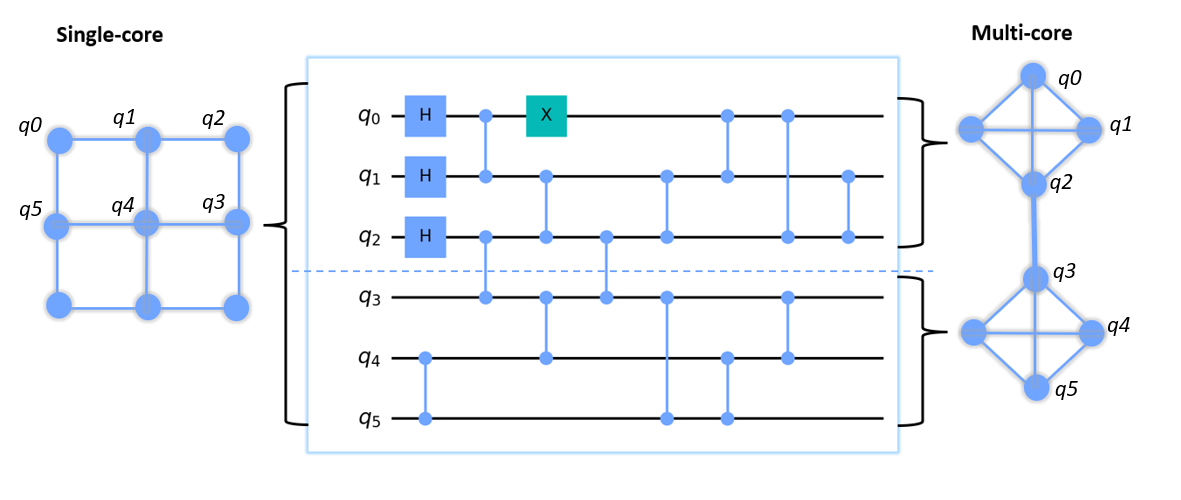

The profiling process involves analyzing the dependencies and resource requirements of each quantum gate within a circuit. By understanding the circuit structure, the researchers can determine which gates can be executed in parallel and how to best map the circuit to the target hardware architecture.

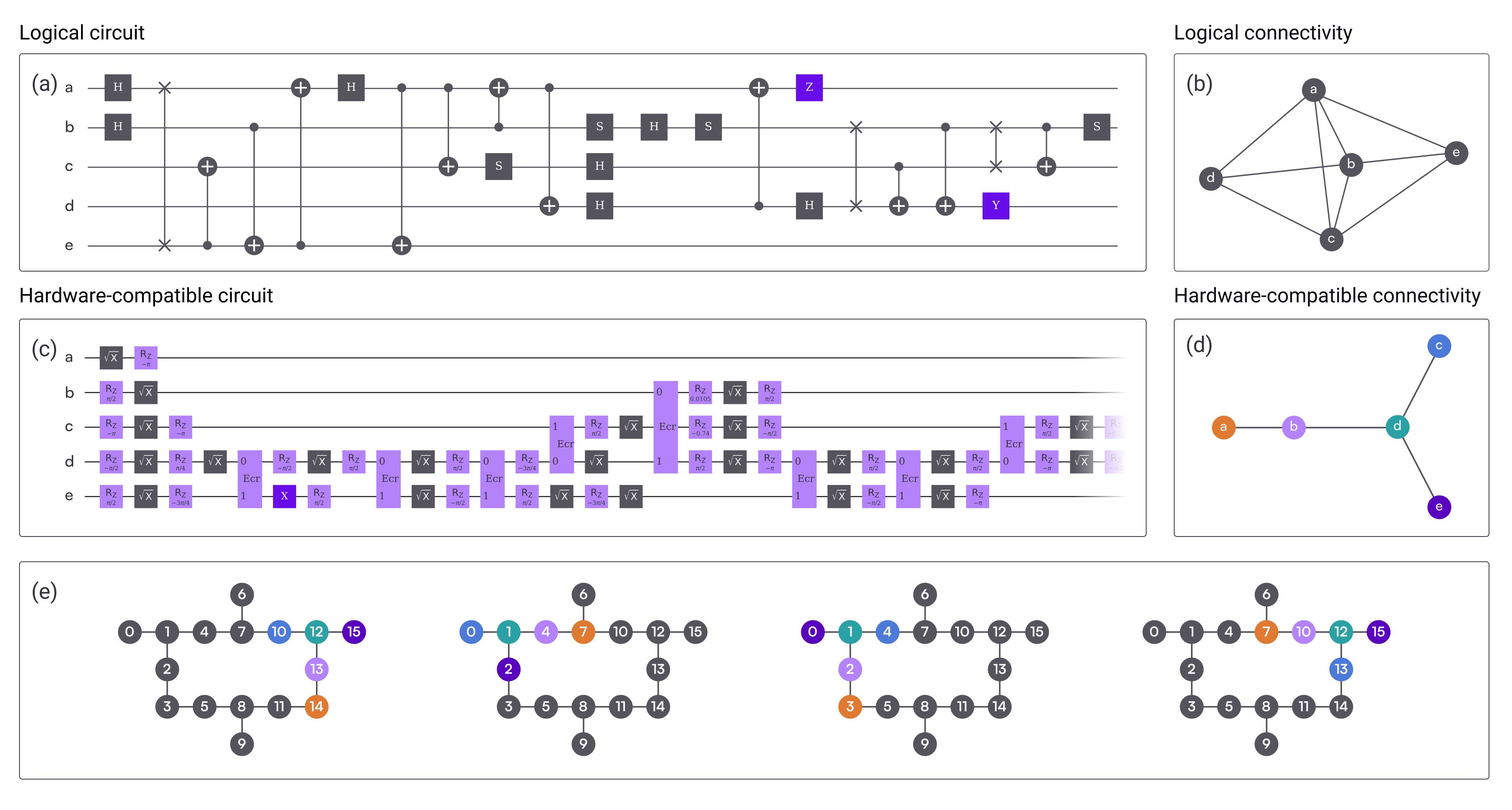

The paper presents case studies that apply the profiling techniques to various quantum circuits, including those from the Learning to Rank Quantum Circuits for Hardware Optimization and Design and Execution of Quantum Circuits Using Tens of Superconducting Qubits papers. The results demonstrate the potential for significant performance improvements through parallelization and hardware-specific optimizations.

Critical Analysis

The paper presents a promising approach for profiling and optimizing quantum circuits on classical hardware, but it also acknowledges several limitations and areas for further research:

- The profiling techniques rely on accurate models of the target hardware, which may not always be available or easy to obtain.

- The paper focuses on single-qubit and two-qubit gates, but more complex multi-qubit gates may require additional considerations.

- The benchmarks used in the study may not be representative of the full range of quantum circuits encountered in practice, so further validation is needed.

- The paper does not address the challenges of error correction and fault tolerance, which are critical for scaling up practical quantum computing.

Additionally, while the paper demonstrates the potential for performance improvements, it does not quantify the actual speedups that can be achieved in real-world scenarios. Further research is needed to fully understand the practical implications and limitations of the proposed techniques.

Conclusion

This paper presents a systematic approach for profiling and optimizing the execution of quantum circuits on classical computing hardware. By analyzing the structure and resource requirements of quantum circuits, the researchers identify opportunities for parallelization and hardware-specific optimizations that can lead to more efficient implementation of quantum algorithms on available classical systems.

The techniques described in this paper represent an important step towards bridging the gap between theoretical quantum algorithms and practical realizations. As classical hardware continues to evolve and quantum computing technologies mature, these types of optimization strategies will play a crucial role in advancing the field of quantum computing and bringing its benefits to real-world applications.

This summary was produced with help from an AI and may contain inaccuracies - check out the links to read the original source documents!

Related Papers

0

Profiling quantum circuits for their efficient execution on single- and multi-core architectures

Medina Bandic, Pablo le Henaff, Anabel Ovide, Pau Escofet, Sahar Ben Rached, Santiago Rodrigo, Hans van Someren, Sergi Abadal, Eduard Alarcon, Carmen G. Almudever, Sebastian Feld

Application-specific quantum computers offer the most efficient means to tackle problems intractable by classical computers. Realizing these architectures necessitates a deep understanding of quantum circuit properties and their relationship to execution outcomes on quantum devices. Our study aims to perform for the first time a rigorous examination of quantum circuits by introducing graph theory-based metrics extracted from their qubit interaction graph and gate dependency graph alongside conventional parameters describing the circuit itself. This methodology facilitates a comprehensive analysis and clustering of quantum circuits. Furthermore, it uncovers a connection between parameters rooted in both qubit interaction and gate dependency graphs, and the performance metrics for quantum circuit mapping, across a range of established quantum device and mapping configurations. Among the various device configurations, we particularly emphasize modular (i.e., multi-core) quantum computing architectures due to their high potential as a viable solution for quantum device scalability. This thorough analysis will help us to: i) identify key attributes of quantum circuits that affect the quantum circuit mapping performance metrics; ii) predict the performance on a specific chip for similar circuit structures; iii) determine preferable combinations of mapping techniques and hardware setups for specific circuits; and iv) define representative benchmark sets by clustering similarly structured circuits.

Read more7/18/2024

0

Visual Analytics of Performance of Quantum Computing Systems and Circuit Optimization

Junghoon Chae, Chad A. Steed, Travis S. Humble

Driven by potential exponential speedups in business, security, and scientific scenarios, interest in quantum computing is surging. This interest feeds the development of quantum computing hardware, but several challenges arise in optimizing application performance for hardware metrics (e.g., qubit coherence and gate fidelity). In this work, we describe a visual analytics approach for analyzing the performance properties of quantum devices and quantum circuit optimization. Our approach allows users to explore spatial and temporal patterns in quantum device performance data and it computes similarities and variances in key performance metrics. Detailed analysis of the error properties characterizing individual qubits is also supported. We also describe a method for visualizing the optimization of quantum circuits. The resulting visualization tool allows researchers to design more efficient quantum algorithms and applications by increasing the interpretability of quantum computations.

Read more9/11/2024

0

Characterizing the Inter-Core Qubit Traffic in Large-Scale Quantum Modular Architectures

Sahar Ben Rached, Isaac Lopez Agudo, Santiago Rodrigo, Medina Bandic, Sebastian Feld, Hans van Someren, Eduard Alarc'on, Carmen G. Almud'ever, Sergi Abadal

Modular quantum processor architectures are envisioned as a promising solution for the scalability of quantum computing systems beyond the Noisy Intermediate Scale Quantum (NISQ) devices era. Based upon interconnecting tens to hundreds of quantum cores via a quantum intranet, this approach unravels the pressing limitations of densely qubit-packed monolithic processors, mainly by mitigating the requirements of qubit control and enhancing qubit isolation, and therefore enables executing large-scale algorithms on quantum computers. In order to optimize such architectures, it is crucial to analyze the quantum state transfers occurring via inter-core communication networks, referred to as inter-core qubit traffic. This would also provide insights to improve the software and hardware stack for multi-core quantum computers. To this aim, we present a pioneering characterization of the spatio-temporal inter-core qubit traffic in large-scale circuits. The programs are executed on an all-to-all connected multi-core architecture that supports up to around 1000 qubits. We characterize the qubit traffic based on multiple performance metrics to assess the computational process and the communication overhead. Based on the showcased results, we conclude on the scalability of the presented algorithms, provide a set of guidelines to improve mapping quantum circuits to multi-core processors, and lay the foundations of benchmarking large-scale multi-core architectures.

Read more9/5/2024

0

Learning to rank quantum circuits for hardware-optimized performance enhancement

Gavin S. Hartnett, Aaron Barbosa, Pranav S. Mundada, Michael Hush, Michael J. Biercuk, Yuval Baum

We introduce and experimentally test a machine-learning-based method for ranking logically equivalent quantum circuits based on expected performance estimates derived from a training procedure conducted on real hardware. We apply our method to the problem of layout selection, in which abstracted qubits are assigned to physical qubits on a given device. Circuit measurements performed on IBM hardware indicate that the maximum and median fidelities of logically equivalent layouts can differ by an order of magnitude. We introduce a circuit score used for ranking that is parameterized in terms of a physics-based, phenomenological error model whose parameters are fit by training a ranking-loss function over a measured dataset. The dataset consists of quantum circuits exhibiting a diversity of structures and executed on IBM hardware, allowing the model to incorporate the contextual nature of real device noise and errors without the need to perform an exponentially costly tomographic protocol. We perform model training and execution on the 16-qubit ibmq_guadalupe device and compare our method to two common approaches: random layout selection and a publicly available baseline called Mapomatic. Our model consistently outperforms both approaches, predicting layouts that exhibit lower noise and higher performance. In particular, we find that our best model leads to a $1.8times$ reduction in selection error when compared to the baseline approach and a $3.2times$ reduction when compared to random selection. Beyond delivering a new form of predictive quantum characterization, verification, and validation, our results reveal the specific way in which context-dependent and coherent gate errors appear to dominate the divergence from performance estimates extrapolated from simple proxy measures.

Read more4/11/2024