A Programming Model for Disaggregated Memory over CXL

0

Sign in to get full access

Overview

- The paper proposes a programming model for disaggregated memory systems using the Compute Express Link (CXL) interconnect.

- It aims to enable efficient and transparent access to remote memory resources without requiring significant changes to existing software stacks.

- The model introduces mechanisms for memory allocation, access, and synchronization in a disaggregated environment.

Plain English Explanation

In modern computer systems, memory is often physically separated from the processors that use it, a concept known as [object Object]. This can provide benefits like improved scalability and flexibility. However, it also introduces challenges in how software interacts with these remote memory resources.

The paper presents a new [object Object] that aims to make it easier for software to access and manage disaggregated memory over the [object Object]. The key ideas are:

- Memory Allocation: The model provides mechanisms for applications to dynamically allocate and deallocate memory from the disaggregated pool, similar to how local memory is managed.

- Memory Access: Applications can transparently access remote memory as if it were local, without needing to worry about the underlying communication protocols.

- Synchronization: The model includes primitives for coordinating access to shared memory regions between different processes or threads, ensuring data consistency.

By hiding the complexities of the disaggregated architecture, this programming model allows existing software to leverage remote memory resources with minimal changes. This can help [object Object] and enable more [object Object] to take advantage of disaggregated memory.

Technical Explanation

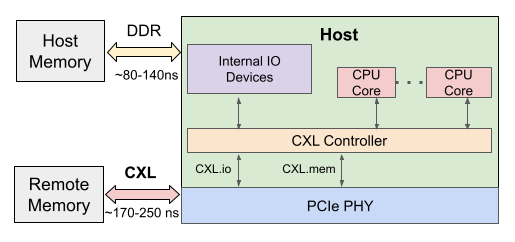

The paper first provides an overview of the CXL interconnect and how it enables the disaggregation of memory from compute resources. It then introduces the key components of the proposed programming model:

-

Memory Allocation: The model includes system calls for applications to request memory from the disaggregated pool, similar to how local memory is allocated using

malloc(). It also provides mechanisms for deallocating this remote memory when no longer needed. -

Memory Access: The programming model allows applications to transparently access remote memory through familiar load and store instructions, without needing to manage the underlying communication protocols. It leverages hardware features of CXL, like remote memory access and cache coherence, to enable this transparent access.

-

Synchronization: To coordinate access to shared memory regions between different processes or threads, the model provides synchronization primitives like mutexes and condition variables. These primitives are designed to work seamlessly across local and remote memory.

The paper also discusses the implementation of this programming model, including the kernel-level components and user-level libraries. It presents performance evaluations that demonstrate the efficiency and scalability of the proposed approach compared to alternative solutions.

Critical Analysis

The paper presents a well-designed programming model that addresses several key challenges in leveraging disaggregated memory over CXL. By providing a familiar and transparent interface, the model enables the adoption of CXL-based systems with minimal changes to existing software stacks.

However, the paper does not delve into potential limitations or edge cases that may arise in real-world deployment scenarios. For example, it does not discuss how the programming model handles failures or faults in the disaggregated memory subsystem, or how it might perform under varying workload characteristics and access patterns.

Additionally, the paper focuses primarily on the technical aspects of the programming model and does not provide a deeper analysis of the broader implications and trade-offs of disaggregated memory architectures. Further research could explore the impact of this technology on system-level performance, energy efficiency, and overall cost-effectiveness.

Conclusion

The proposed programming model for disaggregated memory over CXL presents a promising approach to enabling efficient and transparent access to remote memory resources. By hiding the complexities of the underlying architecture, the model can facilitate the adoption of CXL-based systems and enable a wider range of applications to benefit from the flexibility and scalability of disaggregated memory. As the industry continues to explore the potential of CXL and disaggregated architectures, this research contributes a valuable building block towards more [object Object].

This summary was produced with help from an AI and may contain inaccuracies - check out the links to read the original source documents!

Related Papers

0

A Programming Model for Disaggregated Memory over CXL

Gal Assa, Michal Friedman, Ori Lahav

CXL (Compute Express Link) is an emerging open industry-standard interconnect between processing and memory devices that is expected to revolutionize the way systems are designed in the near future. It enables cache-coherent shared memory pools in a disaggregated fashion at unprecedented scales, allowing algorithms to interact with a variety of storage devices using simple loads and stores in a cacheline granularity. Alongside with unleashing unique opportunities for a wide range of applications, CXL introduces new challenges of data management and crash consistency. Alas, CXL lacks an adequate programming model, which makes reasoning about the correctness and expected behaviors of algorithms and systems on top of it nearly impossible. In this work, we present CXL0, the first programming model for concurrent programs running on top of CXL. We propose a high-level abstraction for CXL memory accesses and formally define operational semantics on top of that abstraction. We provide a set of general transformations that adapt concurrent algorithms to the new disruptive technology. Using these transformations, every linearizable algorithm can be easily transformed into its provably correct version in the face of a full-system or sub-system crash. We believe that this work will serve as the stepping stone for systems design and modelling on top of CXL, and support the development of future models as software and hardware evolve.

Read more7/24/2024

0

Position: CXL Shared Memory Programming: Barely Distributed and Almost Persistent

Yi Xu, Suyash Mahar, Ziheng Liu, Mingyao Shen, Steven Swanson

While Compute Express Link (CXL) enables support for cache-coherent shared memory among multiple nodes, it also introduces new types of failures--processes can fail before data does, or data might fail before a process does. The lack of a failure model for CXL-based shared memory makes it challenging to understand and mitigate these failures. To solve these challenges, in this paper, we describe a model categorizing and handling the CXL-based shared memory's failures: data and process failures. Data failures in CXL-based shared memory render data inaccessible or inconsistent for a currently running application. We argue that such failures are unlike data failures in distributed storage systems and require CXL-specific handling. To address this, we look into traditional data failure mitigation techniques like erasure coding and replication and propose new solutions to better handle data failures in CXL-based shared memory systems. Next, we look into process failures and compare the failures and potential solutions with PMEM's failure model and programming solutions. We argue that although PMEM shares some of CXL's characteristics, it does not fully address CXL's volatile nature and low access latencies. Finally, taking inspiration from PMEM programming solutions, we propose techniques to handle these new failures. Thus, this paper is the first work to define the CXL-based shared memory failure model and propose tailored solutions that address challenges specific to CXL-based systems.

Read more7/18/2024

0

Memory Sharing with CXL: Hardware and Software Design Approaches

Sunita Jain, Nagaradhesh Yeleswarapu, Hasan Al Maruf, Rita Gupta

Compute Express Link (CXL) is a rapidly emerging coherent interconnect standard that provides opportunities for memory pooling and sharing. Memory sharing is a well-established software feature that improves memory utilization by avoiding unnecessary data movement. In this paper, we discuss multiple approaches to enable memory sharing with different generations of CXL protocol (i.e., CXL 2.0 and CXL 3.0) considering the challenges with each of the architectures from the device hardware and software viewpoint.

Read more4/5/2024

0

emucxl: an emulation framework for CXL-based disaggregated memory applications

Raja Gond, Purushottam Kulkarni

The emergence of CXL (Compute Express Link) promises to transform the status of interconnects between host and devices and in turn impact the design of all software layers. With its low overhead, low latency, and memory coherency capabilities, CXL has the potential to improve the performance of existing devices while making viable new operational use cases (e.g., disaggregated memory pools, cache coherent memory across devices etc.). The focus of this work is design of applications and middleware with use of CXL for supporting disaggregated memory. A vital building block for solutions in this space is the availability of a standard CXL hardware and software platform. Currently, CXL devices are not commercially available, and researchers often rely on custom-built hardware or emulation techniques and/or use customized software interfaces and abstractions. These techniques do not provide a standard usage model and abstraction layer for CXL usage, and developers and researchers have to reinvent the CXL setup to design and test their solutions, our work aims to provide a standardized view of the CXL emulation platform and the software interfaces and abstractions for disaggregated memory. This standardization is designed and implemented as a user space library, emucxl and is available as a virtual appliance. The library provides a user space API and is coupled with a NUMA-based CXL emulation backend. Further, we demonstrate usage of the standardized API for different use cases relying on disaggregated memory and show that generalized functionality can be built using the open source emucxl library.

Read more4/15/2024