Resource-aware scheduling of multiple quantum circuits on a hardware device

0

Sign in to get full access

Overview

- This paper introduces a novel approach for optimizing the scheduling and layout of quantum circuits on resource-constrained distributed quantum hardware.

- The authors formulate the problem of intra-device scheduling as an optimization problem and propose a scalable solution that can handle the complexity of real-world quantum systems.

- The proposed method aims to minimize the overall circuit execution time by considering factors such as qubit connectivity, resource constraints, and control dependencies.

Plain English Explanation

The paper addresses a key challenge in quantum computing: how to efficiently execute quantum circuits on physical hardware that has limited resources and connectivity. The authors recognize that as quantum systems become more complex, the task of mapping and scheduling these circuits becomes increasingly difficult.

To tackle this problem, the researchers <a href="https://aimodels.fyi/papers/arxiv/scalable-circuit-cutting-scheduling-resource-constrained-distributed">formulate the intra-device scheduling as an optimization problem</a>. This means they define a mathematical model that captures the various constraints and objectives, such as minimizing the overall circuit execution time while respecting the hardware's limitations.

The authors then propose a <a href="https://aimodels.fyi/papers/arxiv/learning-to-rank-quantum-circuits-hardware-optimized">scalable solution</a> that can handle the complexity of real-world quantum systems. This solution involves techniques like circuit cutting and scheduling, which aim to break down the quantum circuit into smaller, more manageable pieces and then arrange the execution of these pieces in an optimal way.

By considering factors like qubit connectivity, resource constraints, and control dependencies, the proposed method seeks to <a href="https://aimodels.fyi/papers/arxiv/distributed-quantum-computation-minimum-circuit-execution-time">minimize the overall circuit execution time</a>. This is crucial for improving the performance and practicality of quantum computers, as faster circuit execution can lead to more efficient computation and a better user experience.

The authors also discuss the <a href="https://aimodels.fyi/papers/arxiv/design-execution-quantum-circuits-using-tens-superconducting">design and execution of quantum circuits</a> on real-world hardware, highlighting the challenges and trade-offs involved in mapping these circuits to physical devices.

Technical Explanation

The paper presents a novel approach for optimizing the scheduling and layout of quantum circuits on resource-constrained distributed quantum hardware. The authors <a href="https://aimodels.fyi/papers/arxiv/scalable-circuit-cutting-scheduling-resource-constrained-distributed">formulate the problem of intra-device scheduling as an optimization problem</a>, where the goal is to minimize the overall circuit execution time while respecting the hardware's limitations.

To solve this problem, the researchers propose a <a href="https://aimodels.fyi/papers/arxiv/learning-to-rank-quantum-circuits-hardware-optimized">scalable solution</a> that combines circuit cutting and scheduling techniques. The circuit cutting step divides the quantum circuit into smaller, more manageable pieces, while the scheduling step arranges the execution of these pieces in an optimal way.

The proposed solution takes into account various factors, such as qubit connectivity, resource constraints, and control dependencies, to <a href="https://aimodels.fyi/papers/arxiv/distributed-quantum-computation-minimum-circuit-execution-time">minimize the overall circuit execution time</a>. The authors also discuss the <a href="https://aimodels.fyi/papers/arxiv/design-execution-quantum-circuits-using-tens-superconducting">design and execution of quantum circuits</a> on real-world hardware, highlighting the challenges and trade-offs involved in mapping these circuits to physical devices.

Critical Analysis

The paper presents a promising approach for optimizing the scheduling and layout of quantum circuits on resource-constrained distributed quantum hardware. The authors' formulation of the problem as an optimization task and their proposed scalable solution are both compelling and well-justified.

One potential limitation of the research is the reliance on simulation-based experiments, which may not fully capture the nuances and complexities of real-world quantum hardware. While the authors discuss the challenges of mapping circuits to physical devices, it would be valuable to see the proposed methods evaluated on actual quantum hardware to assess their practical performance and limitations.

Additionally, the paper could have provided more detail on the specific algorithms and techniques used in the circuit cutting and scheduling steps. A deeper technical dive into the implementation of these components would help readers better understand the core innovations and trade-offs involved.

Another area for further research could be the exploration of <a href="https://aimodels.fyi/papers/arxiv/dynamic-inhomogeneous-quantum-resource-scheduling-reinforcement-learning">dynamic and adaptive scheduling approaches</a>, which could potentially offer even greater optimization opportunities by accounting for real-time changes in the system's state and resource availability.

Overall, the paper makes a valuable contribution to the field of quantum computing by addressing a critical challenge in the efficient execution of quantum circuits. The authors' work lays the foundation for further research and development in this important area.

Conclusion

This paper presents a novel approach for optimizing the scheduling and layout of quantum circuits on resource-constrained distributed quantum hardware. By formulating the problem as an optimization task and proposing a scalable solution, the authors aim to minimize the overall circuit execution time and improve the practical viability of quantum computing.

The key innovations of this research include the formulation of intra-device scheduling as an optimization problem and the development of a scalable solution that considers factors such as qubit connectivity, resource constraints, and control dependencies. While the paper relies on simulation-based experiments, the insights and methods presented have the potential to make a significant impact on the field of quantum computing as the technology continues to evolve.

Future research directions could include the evaluation of the proposed techniques on real-world quantum hardware, the exploration of dynamic and adaptive scheduling approaches, and the further refinement of the circuit cutting and scheduling algorithms. By addressing the challenges of efficient quantum circuit execution, this work contributes to the ongoing efforts to unlock the full potential of quantum computing.

This summary was produced with help from an AI and may contain inaccuracies - check out the links to read the original source documents!

Related Papers

0

Resource-aware scheduling of multiple quantum circuits on a hardware device

Debasmita Bhoumik, Ritajit Majumdar, Susmita Sur-Kolay

Recent quantum technologies and quantum error-correcting codes emphasize the requirement for arranging interacting qubits in a nearest-neighbor (NN) configuration while mapping a quantum circuit onto a given hardware device, in order to avoid undesirable noise. It is equally important to minimize the wastage of qubits in a quantum hardware device with m qubits while running circuits of n qubits in total, with n < m. In order to prevent cross-talk between two circuits, a buffer distance between their layouts is needed. Furthermore, not all the qubits and all the two-qubit interactions are at the same noise-level. Scheduling multiple circuits on the same hardware may create a possibility that some circuits are executed on a noisier layout than the others. In this paper, we consider an optimization problem which schedules as many circuits as possible for execution in parallel on the hardware, while maintaining a pre-defined layout quality for each. An integer linear programming formulation to ensure maximum fidelity while preserving the nearest neighbor arrangement among interacting qubits is presented. Our assertion is supported by comprehensive investigations involving various well-known quantum circuit benchmarks. As this scheduling problem is shown to be NP Hard, we also propose a greedy heuristic method which provides 2x and 3x better utilization for 27-qubit and 127-qubit hardware devices respectively in terms of qubits and time.

Read more7/15/2024

🗣️

0

Scalable Circuit Cutting and Scheduling in a Resource-constrained and Distributed Quantum System

Shuwen Kan, Zefan Du, Miguel Palma, Samuel A Stein, Chenxu Liu, Wenqi Wei, Juntao Chen, Ang Li, Ying Mao

Despite quantum computing's rapid development, current systems remain limited in practical applications due to their limited qubit count and quality. Various technologies, such as superconducting, trapped ions, and neutral atom quantum computing technologies are progressing towards a fault tolerant era, however they all face a diverse set of challenges in scalability and control. Recent efforts have focused on multi-node quantum systems that connect multiple smaller quantum devices to execute larger circuits. Future demonstrations hope to use quantum channels to couple systems, however current demonstrations can leverage classical communication with circuit cutting techniques. This involves cutting large circuits into smaller subcircuits and reconstructing them post-execution. However, existing cutting methods are hindered by lengthy search times as the number of qubits and gates increases. Additionally, they often fail to effectively utilize the resources of various worker configurations in a multi-node system. To address these challenges, we introduce FitCut, a novel approach that transforms quantum circuits into weighted graphs and utilizes a community-based, bottom-up approach to cut circuits according to resource constraints, e.g., qubit counts, on each worker. FitCut also includes a scheduling algorithm that optimizes resource utilization across workers. Implemented with Qiskit and evaluated extensively, FitCut significantly outperforms the Qiskit Circuit Knitting Toolbox, reducing time costs by factors ranging from 3 to 2000 and improving resource utilization rates by up to 3.88 times on the worker side, achieving a system-wide improvement of 2.86 times.

Read more5/8/2024

0

Learning to rank quantum circuits for hardware-optimized performance enhancement

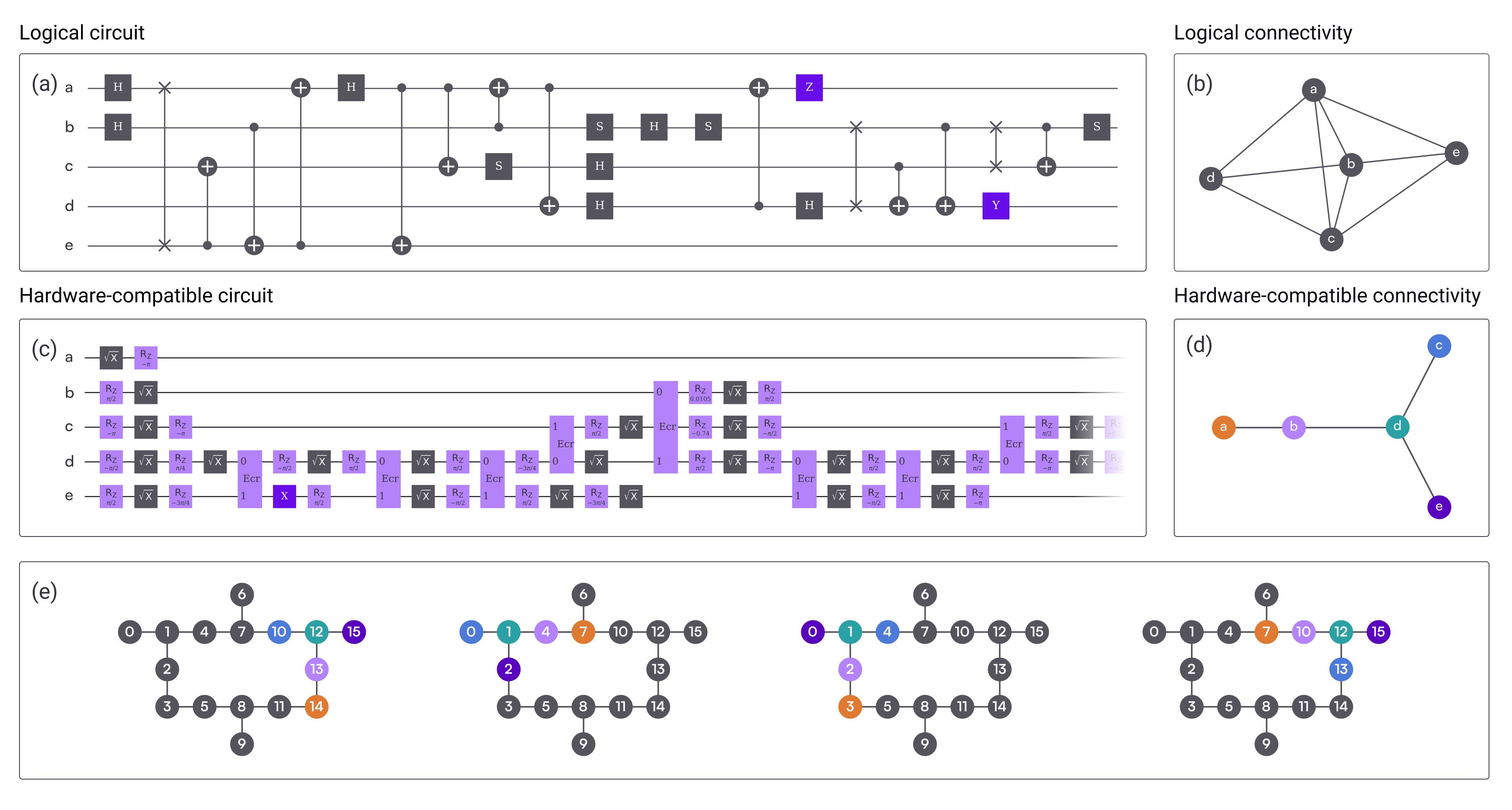

Gavin S. Hartnett, Aaron Barbosa, Pranav S. Mundada, Michael Hush, Michael J. Biercuk, Yuval Baum

We introduce and experimentally test a machine-learning-based method for ranking logically equivalent quantum circuits based on expected performance estimates derived from a training procedure conducted on real hardware. We apply our method to the problem of layout selection, in which abstracted qubits are assigned to physical qubits on a given device. Circuit measurements performed on IBM hardware indicate that the maximum and median fidelities of logically equivalent layouts can differ by an order of magnitude. We introduce a circuit score used for ranking that is parameterized in terms of a physics-based, phenomenological error model whose parameters are fit by training a ranking-loss function over a measured dataset. The dataset consists of quantum circuits exhibiting a diversity of structures and executed on IBM hardware, allowing the model to incorporate the contextual nature of real device noise and errors without the need to perform an exponentially costly tomographic protocol. We perform model training and execution on the 16-qubit ibmq_guadalupe device and compare our method to two common approaches: random layout selection and a publicly available baseline called Mapomatic. Our model consistently outperforms both approaches, predicting layouts that exhibit lower noise and higher performance. In particular, we find that our best model leads to a $1.8times$ reduction in selection error when compared to the baseline approach and a $3.2times$ reduction when compared to random selection. Beyond delivering a new form of predictive quantum characterization, verification, and validation, our results reveal the specific way in which context-dependent and coherent gate errors appear to dominate the divergence from performance estimates extrapolated from simple proxy measures.

Read more4/11/2024

🛠️

0

Quantum Circuit Optimization: Current trends and future direction

Geetha Karuppasamy, Varun Puram, Stevens Johnson, Johnson P Thomas

Optimization of quantum circuits for a given problem is very important in order to achieve faster calculations as well as reduce errors due to noise. Optimization has to be achieved while ensuring correctness at all times. In this survey paper, recent advancements in quantum circuit optimization are explored. Both hardware independent as well as hardware dependent optimization are presented. State-of-the-art methods for optimizing quantum circuits, including analytical algorithms, heuristic algorithms, machine learning-based algorithms, and hybrid quantum-classical algorithms are discussed. Additionally, the advantages and disadvantages of each method and the challenges associated with them are highlighted. Moreover, the potential research opportunities in this field are also discussed.

Read more8/20/2024