Taming Server Memory TCO with Multiple Software-Defined Compressed Tiers

0

Sign in to get full access

Overview

- This paper presents a novel approach to managing server memory costs by using multiple software-defined compressed tiers.

- The proposed system aims to reduce the total cost of ownership (TCO) of server memory while maintaining performance.

- The researchers evaluate their solution using real-world workloads and compare it to existing memory compression techniques.

Plain English Explanation

The paper discusses a new way to manage the cost of server memory, which can be a significant expense for companies running large-scale computing operations. The researchers developed a system that uses multiple layers of compressed memory, each optimized for different types of data and access patterns.

By <a href="https://aimodels.fyi/papers/arxiv/assessing-economic-viability-comparative-analysis-total-cost">carefully managing the trade-offs between memory capacity, performance, and cost</a>, the system can reduce the overall cost of owning and operating server memory while still providing the necessary performance. This could be especially helpful for hyperscale computing environments where memory expenses are a significant portion of the total infrastructure costs.

The researchers tested their system using realistic workloads and compared it to existing memory compression techniques. The results suggest that their approach can provide significant cost savings without sacrificing performance.

Technical Explanation

The paper introduces a novel memory management system that uses multiple software-defined compressed tiers to reduce the total cost of ownership (TCO) of server memory. The key idea is to leverage different compression algorithms and memory technologies to optimize for different data types and access patterns, resulting in a more efficient use of available memory resources.

The system consists of three main components: a hot tier using high-performance in-memory compression, a warm tier using lower-cost high-density memory with moderate compression, and a cold tier using low-cost, high-capacity storage-class memory with aggressive compression. <a href="https://aimodels.fyi/papers/arxiv/comprehensive-survey-model-compression-speed-up-vision">The compression algorithms and memory technologies are selected based on the specific requirements of each tier</a>, allowing the system to scale to 32 GPUs and beyond.

The researchers evaluate their solution using real-world workloads and compare it to existing memory compression techniques. The results show that their approach can achieve significant TCO savings while maintaining the required performance levels.

Critical Analysis

The paper provides a well-designed and thorough evaluation of the proposed memory management system, addressing important considerations such as performance, cost, and scalability. The use of multiple software-defined compressed tiers is a compelling approach to optimizing server memory usage and reducing overall TCO.

One potential limitation of the study is that it focuses primarily on the system-level costs and performance, without delving into the detailed implementation or the specific trade-offs involved in selecting the compression algorithms and memory technologies for each tier. Additional research could explore these lower-level design decisions and their impact on the overall system.

Furthermore, the paper does not discuss the potential challenges in deploying and managing such a complex memory system in a real-world production environment. Factors such as workload variability, dynamic resource allocation, and system reliability could be important considerations for practical adoption.

Conclusion

This paper presents a novel approach to managing server memory costs by using multiple software-defined compressed tiers. The proposed system aims to optimize the trade-offs between memory capacity, performance, and cost, resulting in significant TCO savings while maintaining the required performance.

The researchers provide a thorough evaluation of their solution using realistic workloads, demonstrating its effectiveness in reducing memory-related expenses. This work could have important implications for power-efficient image storage and other applications where memory costs are a significant concern, particularly in large-scale computing environments.

This summary was produced with help from an AI and may contain inaccuracies - check out the links to read the original source documents!

Related Papers

0

Taming Server Memory TCO with Multiple Software-Defined Compressed Tiers

Sandeep Kumar, Aravinda Prasad, Sreenivas Subramoney

Memory accounts for 33 - 50% of the total cost of ownership (TCO) in modern data centers. We propose a novel solution to tame memory TCO through the novel creation and judicious management of multiple software-defined compressed memory tiers. As opposed to the state-of-the-art solutions that employ a 2-Tier solution, a single compressed tier along with DRAM, we define multiple compressed tiers implemented through a combination of different compression algorithms, memory allocators for compressed objects, and backing media to store compressed objects. These compressed memory tiers represent distinct points in the access latency, data compressibility, and unit memory usage cost spectrum, allowing rich and flexible trade-offs between memory TCO savings and application performance impact. A key advantage with ntier is that it enables aggressive memory TCO saving opportunities by placing warm data in low latency compressed tiers with a reasonable performance impact while simultaneously placing cold data in the best memory TCO saving tiers. We believe our work represents an important server system configuration and optimization capability to achieve the best SLA-aware performance per dollar for applications hosted in production data center environments. We present a comprehensive and rigorous analytical cost model for performance and TCO trade-off based on continuous monitoring of the application's data access profile. Guided by this model, our placement model takes informed actions to dynamically manage the placement and migration of application data across multiple software-defined compressed tiers. On real-world benchmarks, our solution increases memory TCO savings by 22% - 40% percentage points while maintaining performance parity or improves performance by 2% - 10% percentage points while maintaining memory TCO parity compared to state-of-the-art 2-Tier solutions.

Read more4/23/2024

0

Streamlining CXL Adoption for Hyperscale Efficiency

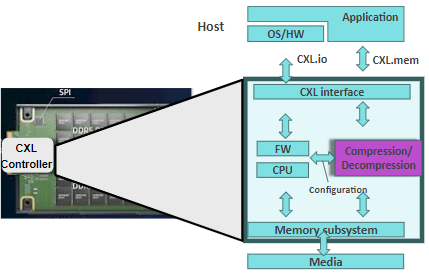

Angelos Arelakis, Nilesh Shah, Yiannis Nikolakopoulos, Dimitrios Palyvos-Giannas

In our exploration of Composable Memory systems utilizing CXL, we focus on overcoming adoption barriers at Hyperscale, underscored by economic models demonstrating Total Cost of Ownership (TCO). While CXL addresses the pressing memory capacity needs of emerging Hyperscale applications, the escalating demands from evolving use cases such as AI outpace the capabilities of current CXL solutions. Hyperscalers resort to software-based memory (de)compression technology, alleviating memory capacity, storage, and network constraints but incurring a notable Tax on Compute CPU cycles. As a pivotal guide to the CXL community, Hyperscalers have formulated the groundbreaking Open Compute Project (OCP) Hyperscale CXL Tiered Memory Expander specification. If implemented, this specification lowers TCO adoption barriers, enabling diverse CXL deployments at both Hyperscaler and Enterprise levels. We present a CXL integrated solution, aligning with the aforementioned specification, introducing an energy-efficient, scalable, hardware-accelerated, Lossless Compressed Memory CXL Tier. This solution, slated for mid-2024 production and open for integration with Memory Expander controller manufacturers, offers 2-3X CXL memory compression in nanoseconds, delivering a 20-25% reduction in TCO for end customers without requiring additional physical slots. In our discussion, we pinpoint areas for collaborative innovation within the CXL Community to expedite software/hardware advancements for CXL Tiered Memory Expansion. Furthermore, we delve into unresolved challenges in Pooled deployment and explore potential solutions, collectively aiming to make CXL adoption a No Brainer at Hyperscale.

Read more4/5/2024

🤖

2

SambaNova SN40L: Scaling the AI Memory Wall with Dataflow and Composition of Experts

Raghu Prabhakar, Ram Sivaramakrishnan, Darshan Gandhi, Yun Du, Mingran Wang, Xiangyu Song, Kejie Zhang, Tianren Gao, Angela Wang, Karen Li, Yongning Sheng, Joshua Brot, Denis Sokolov, Apurv Vivek, Calvin Leung, Arjun Sabnis, Jiayu Bai, Tuowen Zhao, Mark Gottscho, David Jackson, Mark Luttrell, Manish K. Shah, Edison Chen, Kaizhao Liang, Swayambhoo Jain, Urmish Thakker, Dawei Huang, Sumti Jairath, Kevin J. Brown, Kunle Olukotun

Monolithic large language models (LLMs) like GPT-4 have paved the way for modern generative AI applications. Training, serving, and maintaining monolithic LLMs at scale, however, remains prohibitively expensive and challenging. The disproportionate increase in compute-to-memory ratio of modern AI accelerators have created a memory wall, necessitating new methods to deploy AI. Composition of Experts (CoE) is an alternative modular approach that lowers the cost and complexity of training and serving. However, this approach presents two key challenges when using conventional hardware: (1) without fused operations, smaller models have lower operational intensity, which makes high utilization more challenging to achieve; and (2) hosting a large number of models can be either prohibitively expensive or slow when dynamically switching between them. In this paper, we describe how combining CoE, streaming dataflow, and a three-tier memory system scales the AI memory wall. We describe Samba-CoE, a CoE system with 150 experts and a trillion total parameters. We deploy Samba-CoE on the SambaNova SN40L Reconfigurable Dataflow Unit (RDU) - a commercial dataflow accelerator architecture that has been co-designed for enterprise inference and training applications. The chip introduces a new three-tier memory system with on-chip distributed SRAM, on-package HBM, and off-package DDR DRAM. A dedicated inter-RDU network enables scaling up and out over multiple sockets. We demonstrate speedups ranging from 2x to 13x on various benchmarks running on eight RDU sockets compared with an unfused baseline. We show that for CoE inference deployments, the 8-socket RDU Node reduces machine footprint by up to 19x, speeds up model switching time by 15x to 31x, and achieves an overall speedup of 3.7x over a DGX H100 and 6.6x over a DGX A100.

Read more5/14/2024

0

Characterizing the Dilemma of Performance and Index Size in Billion-Scale Vector Search and Breaking It with Second-Tier Memory

Rongxin Cheng, Yifan Peng, Xingda Wei, Hongrui Xie, Rong Chen, Sijie Shen, Haibo Chen

Vector searches on large-scale datasets are critical to modern online services like web search and RAG, which necessity storing the datasets and their index on the secondary storage like SSD. In this paper, we are the first to characterize the trade-off of performance and index size in existing SSD-based graph and cluster indexes: to improve throughput by 5.7$times$ and 1.7$times$, these indexes have to pay a 5.8$times$ storage amplification and 7.7$times$ with respect to the dataset size, respectively. The root cause is that the coarse-grained access of SSD mismatches the fine-grained random read required by vector indexes with small amplification. This paper argues that second-tier memory, such as remote DRAM/NVM connected via RDMA or CXL, is a powerful storage for addressing the problem from a system's perspective, thanks to its fine-grained access granularity. However, putting existing indexes -- primarily designed for SSD -- directly on second-tier memory cannot fully utilize its power. Meanwhile, second-tier memory still behaves more like storage, so using it as DRAM is also inefficient. To this end, we build a graph and cluster index that centers around the performance features of second-tier memory. With careful execution engine and index layout designs, we show that vector indexes can achieve optimal performance with orders of magnitude smaller index amplification, on a variety of second-tier memory devices. Based on our improved graph and vector indexes on second-tier memory, we further conduct a systematic study between them to facilitate developers choosing the right index for their workloads. Interestingly, the findings on the second-tier memory contradict the ones on SSDs.

Read more5/8/2024