ASCENT: Amplifying Power Side-Channel Resilience via Learning & Monte-Carlo Tree Search

0

Sign in to get full access

Overview

• This paper presents ASCENT, a novel technique for improving the power side-channel resilience of hardware designs through a combination of machine learning and Monte Carlo tree search. • Power side-channel attacks are a major threat to the security of hardware devices, as they can potentially extract sensitive information by analyzing the power consumption patterns of a device during operation. • ASCENT aims to make hardware designs more resilient to these attacks by automatically modifying the logic synthesis process to generate circuits with reduced power side-channel leakage.

Plain English Explanation

• Power side-channel attacks are a way for hackers to steal information from electronic devices by analyzing the pattern of power usage during normal operation. This can be a big threat to the security of things like smartphones, computers, and other hardware. • The researchers developed a technique called ASCENT that uses machine learning and a special search algorithm to automatically modify the way the hardware is designed, in order to make it harder for these power side-channel attacks to be successful. • ASCENT works by exploring different possible hardware designs and selecting the ones that are the most resilient to power side-channel attacks, without significantly impacting the performance or functionality of the device.

Technical Explanation

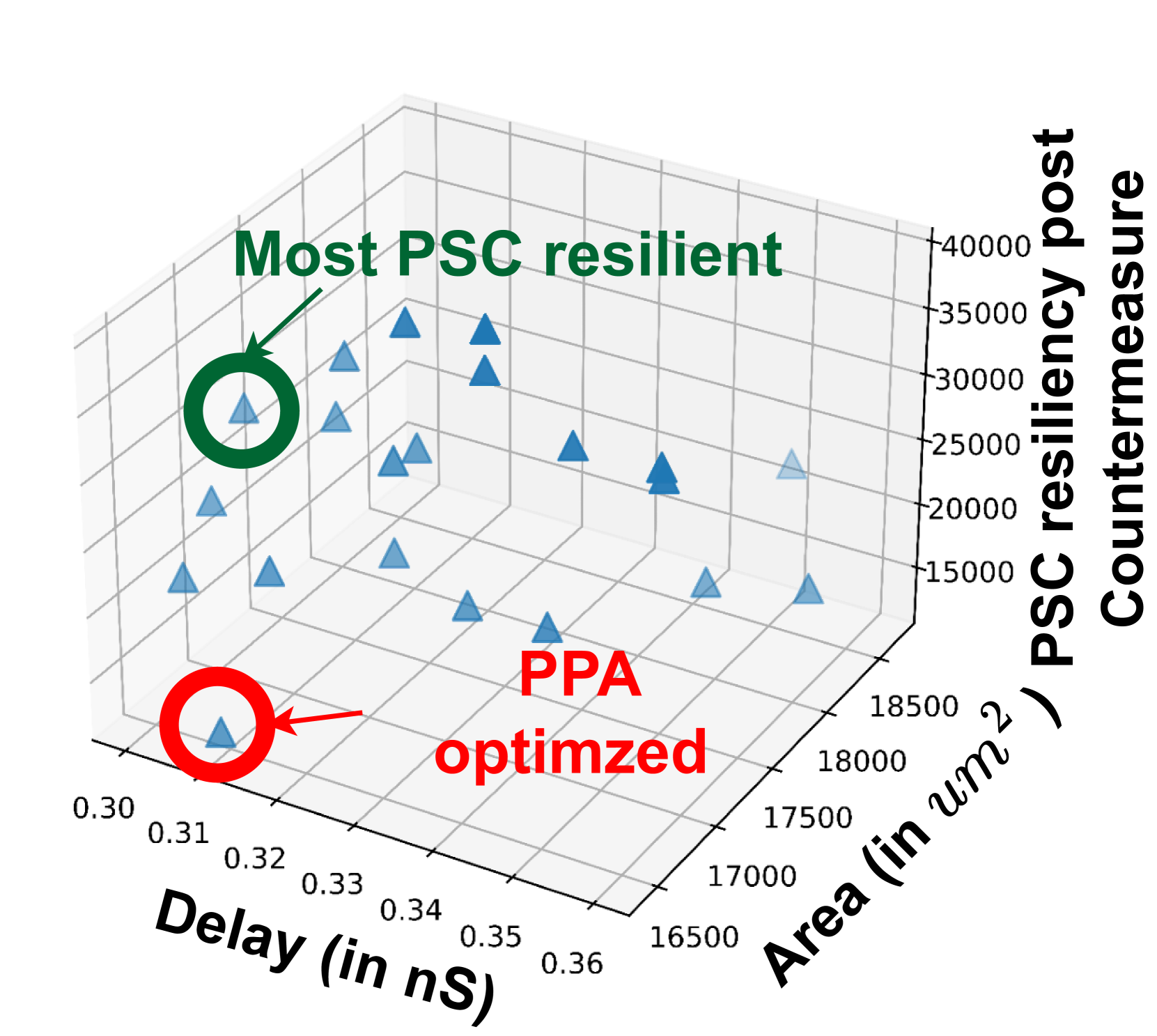

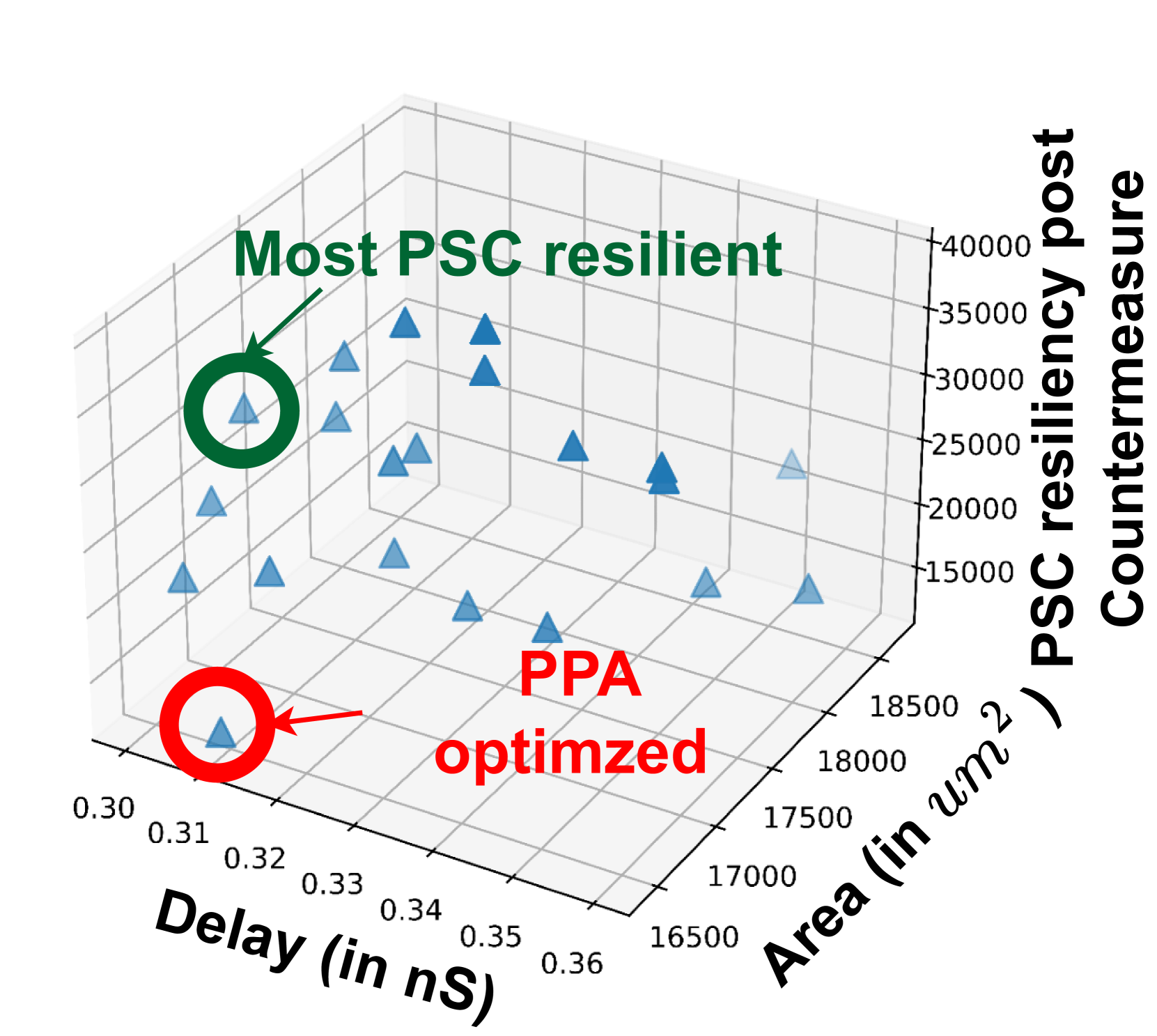

• ASCENT uses Monte Carlo tree search to efficiently explore the design space and identify hardware configurations that are resilient to power side-channel attacks. • The technique also incorporates machine learning to predict the power side-channel leakage of different hardware designs, allowing ASCENT to focus its search on the most promising configurations. • ASCENT is designed to integrate seamlessly with the logic synthesis process, allowing it to be easily adopted by hardware designers without requiring major changes to their existing workflows. • The researchers evaluated ASCENT on several benchmark circuits and found that it was able to generate hardware designs with significantly reduced power side-channel leakage, while maintaining acceptable performance and area overhead.

Critical Analysis

• The paper acknowledges that ASCENT is not a panacea for power side-channel attacks, and that there are still some limitations to the technique. • For example, ASCENT relies on the availability of accurate power models and side-channel leakage predictors, which may not always be easy to obtain, especially for complex hardware designs. • Additionally, the paper does not explore the potential impact of ASCENT on other hardware security properties, such as input-level backdoors or quantum-level attacks. • Further research is needed to understand the broader implications of using ASCENT in real-world hardware design workflows and to address any potential tradeoffs or unintended consequences.

Conclusion

• ASCENT represents a promising step forward in the ongoing effort to protect hardware devices from power side-channel attacks. • By combining machine learning and Monte Carlo tree search, ASCENT can automatically generate hardware designs that are more resilient to these types of attacks, without sacrificing too much in terms of performance or area. • While ASCENT is not a silver bullet, it demonstrates the potential for leveraging advanced algorithms and techniques to enhance the security of hardware systems in the face of increasingly sophisticated threats.

This summary was produced with help from an AI and may contain inaccuracies - check out the links to read the original source documents!

Related Papers

0

ASCENT: Amplifying Power Side-Channel Resilience via Learning & Monte-Carlo Tree Search

Jitendra Bhandari, Animesh Basak Chowdhury, Mohammed Nabeel, Ozgur Sinanoglu, Siddharth Garg, Ramesh Karri, Johann Knechtel

Power side-channel (PSC) analysis is pivotal for securing cryptographic hardware. Prior art focused on securing gate-level netlists obtained as-is from chip design automation, neglecting all the complexities and potential side-effects for security arising from the design automation process. That is, automation traditionally prioritizes power, performance, and area (PPA), sidelining security. We propose a security-first approach, refining the logic synthesis stage to enhance the overall resilience of PSC countermeasures. We introduce ASCENT, a learning-and-search-based framework that (i) drastically reduces the time for post-design PSC evaluation and (ii) explores the security-vs-PPA design space. Thus, ASCENT enables an efficient exploration of a large number of candidate netlists, leading to an improvement in PSC resilience compared to regular PPA-optimized netlists. ASCENT is up to 120x faster than traditional PSC analysis and yields a 3.11x improvement for PSC resilience of state-of-the-art PSC countermeasures

Read more7/2/2024

✨

0

Preserving Power Optimizations Across the High Level Synthesis of Distinct Application-Specific Circuits

Paulo Garcia

We evaluate the use of software interpretation to push High Level Synthesis of application-specific accelerators toward a higher level of abstraction. Our methodology is supported by a formal power consumption model that computes the power consumption of accelerator components, accurately predicting the power consumption on new designs from prior optimization estimations. We demonstrate how our approach simplifies the re-use of power optimizations across distinct designs, by leveraging the higher level of design abstraction, using two accelerators representative of the robotics domain, implemented through the Bambu High Level Synthesis tool. Results support the research hypothesis, achieving predictions accurate within +/- 1%.

Read more7/10/2024

0

Semi-Supervised Multi-Task Learning Based Framework for Power System Security Assessment

Muhy Eddin Za'ter, Amirhossein Sajadi, Bri-Mathias Hodge

This paper develops a novel machine learning-based framework using Semi-Supervised Multi-Task Learning (SS-MTL) for power system dynamic security assessment that is accurate, reliable, and aware of topological changes. The learning algorithm underlying the proposed framework integrates conditional masked encoders and employs multi-task learning for classification-aware feature representation, which improves the accuracy and scalability to larger systems. Additionally, this framework incorporates a confidence measure for its predictions, enhancing its reliability and interpretability. A topological similarity index has also been incorporated to add topological awareness to the framework. Various experiments on the IEEE 68-bus system were conducted to validate the proposed method, employing two distinct database generation techniques to generate the required data to train the machine learning algorithm. The results demonstrate that our algorithm outperforms existing state-of-the-art machine learning based techniques for security assessment in terms of accuracy and robustness. Finally, our work underscores the value of employing auto-encoders for security assessment, highlighting improvements in accuracy, reliability, and robustness. All datasets and codes used have been made publicly available to ensure reproducibility and transparency.

Read more7/15/2024

0

Quantum Circuit Reconstruction from Power Side-Channel Attacks on Quantum Computer Controllers

Ferhat Erata, Chuanqi Xu, Ruzica Piskac, Jakub Szefer

The interest in quantum computing has grown rapidly in recent years, and with it grows the importance of securing quantum circuits. A novel type of threat to quantum circuits that dedicated attackers could launch are power trace attacks. To address this threat, this paper presents first formalization and demonstration of using power traces to unlock and steal quantum circuit secrets. With access to power traces, attackers can recover information about the control pulses sent to quantum computers. From the control pulses, the gate level description of the circuits, and eventually the secret algorithms can be reverse engineered. This work demonstrates how and what information could be recovered. This work uses algebraic reconstruction from power traces to realize two new types of single trace attacks: per-channel and total power attacks. The former attack relies on per-channel measurements to perform a brute-force attack to reconstruct the quantum circuits. The latter attack performs a single-trace attack using Mixed-Integer Linear Programming optimization. Through the use of algebraic reconstruction, this work demonstrates that quantum circuit secrets can be stolen with high accuracy. Evaluation on 32 real benchmark quantum circuits shows that our technique is highly effective at reconstructing quantum circuits. The findings not only show the veracity of the potential attacks, but also the need to develop new means to protect quantum circuits from power trace attacks. Throughout this work real control pulse information from real quantum computers is used to demonstrate potential attacks based on simulation of collection of power traces.

Read more7/16/2024