Challenging Portability Paradigms: FPGA Acceleration Using SYCL and OpenCL

0

🎲

Sign in to get full access

Overview

- The paper "Challenging Portability Paradigms: FPGA Acceleration Using SYCL and OpenCL" was presented at the HeteroPar 2024 conference.

- It explores the use of SYCL and OpenCL programming models for accelerating applications on FPGA platforms.

- The researchers investigate the performance and portability implications of these approaches compared to traditional FPGA programming.

Plain English Explanation

The paper explores new ways to program FPGA devices, which are specialized computer chips that can be reconfigured to accelerate certain types of computations. Traditionally, programming FPGAs has required specialized knowledge and tools, which can make it difficult to use them alongside other types of processors like CPUs and GPUs.

The researchers in this paper looked at using two programming models, SYCL and OpenCL, to program FPGAs. These models allow developers to write code that can run on different types of hardware, including FPGAs, without needing to learn all the low-level details. The goal was to see if these higher-level programming approaches could make it easier to take advantage of FPGA acceleration while also ensuring the code can run on a variety of hardware platforms.

Technical Explanation

The paper investigates the performance and portability tradeoffs of using SYCL and OpenCL for FPGA acceleration compared to traditional FPGA programming approaches. The researchers implemented several benchmark applications, including dense matrix multiplication and a molecular dynamics kernel, using both the SYCL and OpenCL programming models on FPGA hardware.

Their results show that the SYCL and OpenCL implementations can achieve competitive performance compared to manually optimized FPGA designs, while also providing greater portability across different FPGA platforms. The paper also discusses various factors that impact the portability and performance, such as the efficiency of the underlying compiler toolchains and the ability to leverage hardware-specific optimizations.

Critical Analysis

The paper provides a thorough evaluation of the SYCL and OpenCL approaches for FPGA acceleration, highlighting both the benefits and limitations compared to traditional FPGA programming. However, the study is limited to a relatively small set of benchmark applications, and the performance results may not generalize to a wider range of real-world workloads.

Additionally, the paper does not delve deeply into the specific challenges and tradeoffs involved in mapping higher-level programming models like SYCL and OpenCL onto FPGA hardware. Further research may be needed to fully understand the underlying architectural implications and to identify potential areas for improvement in the compiler and runtime support.

Conclusion

This paper demonstrates that SYCL and OpenCL can be viable options for FPGA acceleration, offering improved portability without sacrificing too much performance. As FPGA technology continues to evolve and become more widely adopted, these higher-level programming models may play an increasingly important role in making FPGA acceleration more accessible to a broader range of developers. However, ongoing research and development will be needed to fully realize the potential of these approaches.

This summary was produced with help from an AI and may contain inaccuracies - check out the links to read the original source documents!

Related Papers

🎲

0

Challenging Portability Paradigms: FPGA Acceleration Using SYCL and OpenCL

Manuel de Castro, Francisco J. and'ujar, Roberto R. Osorio, Roc'io Carratal'a-S'aez, Diego R. Llanos

As the interest in FPGA-based accelerators for HPC applications increases, new challenges also arise, especially concerning different programming and portability issues. This paper aims to provide a snapshot of the current state of the FPGA tooling and its problems. To do so, we evaluate the performance portability of two frameworks for developing FPGA solutions for HPC (SYCL and OpenCL) when using them to port a highly-parallel application to FPGAs, using both ND-range and single-task type of kernels. The developer's general recommendation when using FPGAs is to develop single-task kernels for them, as they are commonly regarded as more suited for such hardware. However, we discovered that, when using high-level approaches such as OpenCL and SYCL to program a highly-parallel application with no FPGA-tailored optimizations, ND-range kernels significantly outperform single-task codes. Specifically, while SYCL struggles to produce efficient FPGA implementations of applications described as single-task codes, its performance excels with ND-range kernels, a result that was unexpectedly favorable.

Read more9/6/2024

0

Gaining Cross-Platform Parallelism for HAL's Molecular Dynamics Package using SYCL

Viktor Skoblin, Felix Hofling, Steffen Christgau

Molecular dynamics simulations are one of the methods in scientific computing that benefit from GPU acceleration. For those devices, SYCL is a promising API for writing portable codes. In this paper, we present the case study of HAL's MD package that has been successfully migrated from CUDA to SYCL. We describe the different strategies that we followed in the process of porting the code. Following these strategies, we achieved code portability across major GPU vendors. Depending on the actual kernels, both significant performance improvements and regressions are observed. As a side effect of the migration process, we obtained impressing speedups also for execution on CPUs.

Read more6/7/2024

0

Taking GPU Programming Models to Task for Performance Portability

Joshua H. Davis, Pranav Sivaraman, Joy Kitson, Konstantinos Parasyris, Harshitha Menon, Isaac Minn, Giorgis Georgakoudis, Abhinav Bhatele

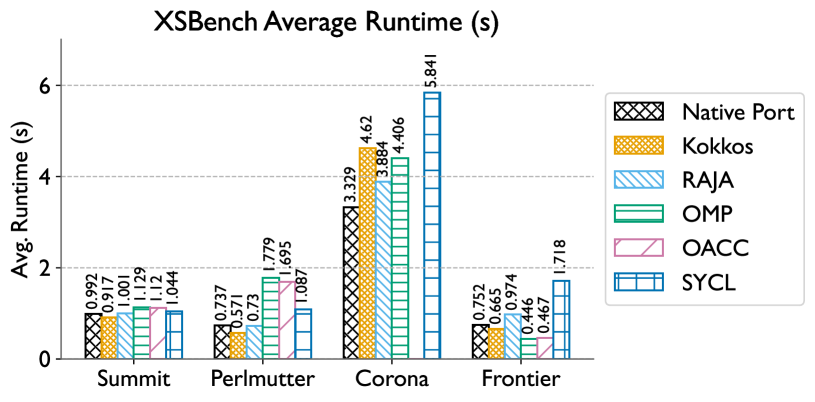

Portability is critical to ensuring high productivity in developing and maintaining scientific software as the diversity in on-node hardware architectures increases. While several programming models provide portability for diverse GPU platforms, they don't make any guarantees about performance portability. In this work, we explore several programming models -- CUDA, HIP, Kokkos, RAJA, OpenMP, OpenACC, and SYCL, to study if the performance of these models is consistently good across NVIDIA and AMD GPUs. We use five proxy applications from different scientific domains, create implementations where missing, and use them to present a comprehensive comparative evaluation of the programming models. We provide a Spack scripting-based methodology to ensure reproducibility of experiments conducted in this work. Finally, we attempt to answer the question -- to what extent does each programming model provide performance portability for heterogeneous systems in real-world usage?

Read more5/22/2024

🚀

0

GROMACS on AMD GPU-Based HPC Platforms: Using SYCL for Performance and Portability

Andrey Alekseenko, Szil'ard P'all, Erik Lindahl

GROMACS is a widely-used molecular dynamics software package with a focus on performance, portability, and maintainability across a broad range of platforms. Thanks to its early algorithmic redesign and flexible heterogeneous parallelization, GROMACS has successfully harnessed GPU accelerators for more than a decade. With the diversification of accelerator platforms in HPC and no obvious choice for a multi-vendor programming model, the GROMACS project found itself at a crossroads. The performance and portability requirements, and a strong preference for a standards-based solution, motivated our choice to use SYCL on both new HPC GPU platforms: AMD and Intel. Since the GROMACS 2022 release, the SYCL backend has been the primary means to target AMD GPUs in preparation for exascale HPC architectures like LUMI and Frontier. SYCL is a cross-platform, royalty-free, C++17-based standard for programming hardware accelerators. It allows using the same code to target GPUs from all three major vendors with minimal specialization. While SYCL implementations build on native toolchains, performance of such an approach is not immediately evident. Biomolecular simulations have challenging performance characteristics: latency sensitivity, the need for strong scaling, and typical iteration times as short as hundreds of microseconds. Hence, obtaining good performance across the range of problem sizes and scaling regimes is particularly challenging. Here, we share the results of our work on readying GROMACS for AMD GPU platforms using SYCL, and demonstrate performance on Cray EX235a machines with MI250X accelerators. Our findings illustrate that portability is possible without major performance compromises. We provide a detailed analysis of node-level kernel and runtime performance with the aim of sharing best practices with the HPC community on using SYCL as a performance-portable GPU framework.

Read more5/3/2024