On-Chip Learning with Memristor-Based Neural Networks: Assessing Accuracy and Efficiency Under Device Variations, Conductance Errors, and Input Noise

0

🧠

Sign in to get full access

Overview

- This paper presents a memristor-based hardware accelerator for training and running neural networks on-chip.

- The accelerator focuses on maintaining accuracy and efficiency despite device variations, conductance errors, and input noise.

- The researchers used realistic SPICE models of commercially available memristors to incorporate non-ideal device characteristics.

- The hardware performs binary image classification using 30 memristors and 4 neurons with three different memristor structures.

- An on-chip training algorithm precisely tunes memristor conductance to achieve target weights.

Plain English Explanation

The paper describes a specialized hardware system built using memristors, which are electronic components that can store and process information like the brain. This hardware is designed to train and run neural networks directly on the chip, without needing to send data to a separate computer.

A key focus of the research is making this memristor-based system robust to imperfections in the hardware, such as variations in the memristor properties and noise in the input data. The researchers used realistic models of commercially available memristors to design the hardware and test it under these real-world conditions.

The hardware is able to perform a simple image classification task, distinguishing between two different types of images, using just 30 memristors and 4 processing units. An algorithm running on the chip itself can precisely adjust the memristors to get the desired performance, even in the presence of significant hardware variations and noisy inputs.

Notably, the researchers found that skipping an initial "reset" step during training can actually reduce the time and energy needed, without a big impact on the system's accuracy. Overall, this work provides insights for building robust and efficient memristor-based neural networks that can operate directly on the edge device, without needing to send data to the cloud.

Technical Explanation

The memristor-based hardware accelerator designed in this paper consists of 30 memristors and 4 neurons, utilizing three different memristor structures based on tungsten, chromium, and carbon. These metal self-directed channel (M-SDC) memristors are modeled using realistic SPICE simulations to incorporate inherent device non-idealities.

The hardware performs binary image classification tasks, with an on-chip training algorithm precisely tuning the memristor conductance to achieve the target weights. Results show that incorporating moderate noise (less than 15%) during training enhances the system's robustness to device variations and noisy input data, achieving up to 97% accuracy despite these challenges.

The network is able to tolerate up to a 10% conductance error without significant accuracy loss. Interestingly, omitting the initial memristor reset pulse during training considerably reduces the training time and energy consumption, with the chromium-based memristor design exhibiting the best performance at 2.4 seconds of training time and 18.9 mJ of energy consumption.

Critical Analysis

The paper provides a thorough evaluation of the memristor-based accelerator's performance under realistic conditions, incorporating device variations and input noise into the simulations. This is a strength, as it helps assess the practicality of deploying such systems in real-world edge applications.

However, the paper does not extensively discuss potential limitations or areas for further research. For example, it would be valuable to understand the scalability of this approach to larger neural networks or more complex tasks, as well as the feasibility of manufacturing the specific memristor structures at scale.

Additionally, the paper could have provided more context on the broader landscape of memristor-based neuromorphic computing and how this work compares to or builds upon other recent advancements in the field.

Conclusion

This research presents a promising memristor-based hardware accelerator for on-chip training and inference of neural networks, with a focus on maintaining accuracy and efficiency despite real-world hardware imperfections. The insights gained from this work, such as the benefits of skipping the initial memristor reset, could help guide the development of robust and energy-efficient memristor-based AI systems for edge computing applications.

This summary was produced with help from an AI and may contain inaccuracies - check out the links to read the original source documents!

Related Papers

🧠

0

On-Chip Learning with Memristor-Based Neural Networks: Assessing Accuracy and Efficiency Under Device Variations, Conductance Errors, and Input Noise

M. Reza Eslami, Dhiman Biswas, Soheib Takhtardeshir, Sarah S. Sharif, Yaser M. Banad

This paper presents a memristor-based compute-in-memory hardware accelerator for on-chip training and inference, focusing on its accuracy and efficiency against device variations, conductance errors, and input noise. Utilizing realistic SPICE models of commercially available silver-based metal self-directed channel (M-SDC) memristors, the study incorporates inherent device non-idealities into the circuit simulations. The hardware, consisting of 30 memristors and 4 neurons, utilizes three different M-SDC structures with tungsten, chromium, and carbon media to perform binary image classification tasks. An on-chip training algorithm precisely tunes memristor conductance to achieve target weights. Results show that incorporating moderate noise (<15%) during training enhances robustness to device variations and noisy input data, achieving up to 97% accuracy despite conductance variations and input noises. The network tolerates a 10% conductance error without significant accuracy loss. Notably, omitting the initial memristor reset pulse during training considerably reduces training time and energy consumption. The hardware designed with chromium-based memristors exhibits superior performance, achieving a training time of 2.4 seconds and an energy consumption of 18.9 mJ. This research provides insights for developing robust and energy-efficient memristor-based neural networks for on-chip learning in edge applications.

Read more8/28/2024

🔮

0

Time-Series Forecasting and Sequence Learning Using Memristor-based Reservoir System

Abdullah M. Zyarah, Dhireesha Kudithipudi

Pushing the frontiers of time-series information processing in the ever-growing domain of edge devices with stringent resources has been impeded by the systems' ability to process information and learn locally on the device. Local processing and learning of time-series information typically demand intensive computations and massive storage as the process involves retrieving information and tuning hundreds of parameters back in time. In this work, we developed a memristor-based echo state network accelerator that features efficient temporal data processing and in-situ online learning. The proposed design is benchmarked using various datasets involving real-world tasks, such as forecasting the load energy consumption and weather conditions. The experimental results illustrate that the hardware model experiences a marginal degradation in performance as compared to the software counterpart. This is mainly attributed to the limited precision and dynamic range of network parameters when emulated using memristor devices. The proposed system is evaluated for lifespan, robustness, and energy-delay product. It is observed that the system demonstrates reasonable robustness for device failure below 10%, which may occur due to stuck-at faults. Furthermore, 247X reduction in energy consumption is achieved when compared to a custom CMOS digital design implemented at the same technology node.

Read more9/17/2024

0

Neuromorphic Circuit Simulation with Memristors: Design and Evaluation Using MemTorch for MNIST and CIFAR

Julio Souto, Guillermo Botella, Daniel Garc'ia, Ra'ul Murillo, Alberto del Barrio

Memristors offer significant advantages as in-memory computing devices due to their non-volatility, low power consumption, and history-dependent conductivity. These attributes are particularly valuable in the realm of neuromorphic circuits for neural networks, which currently face limitations imposed by the Von Neumann architecture and high energy demands. This study evaluates the feasibility of using memristors for in-memory processing by constructing and training three digital convolutional neural networks with the datasets MNIST, CIFAR10 and CIFAR100. Subsequent conversion of these networks into memristive systems was performed using Memtorch. The simulations, conducted under ideal conditions, revealed minimal precision losses of nearly 1% during inference. Additionally, the study analyzed the impact of tile size and memristor-specific non-idealities on performance, highlighting the practical implications of integrating memristors in neuromorphic computing systems. This exploration into memristive neural network applications underscores the potential of Memtorch in advancing neuromorphic architectures.

Read more7/19/2024

0

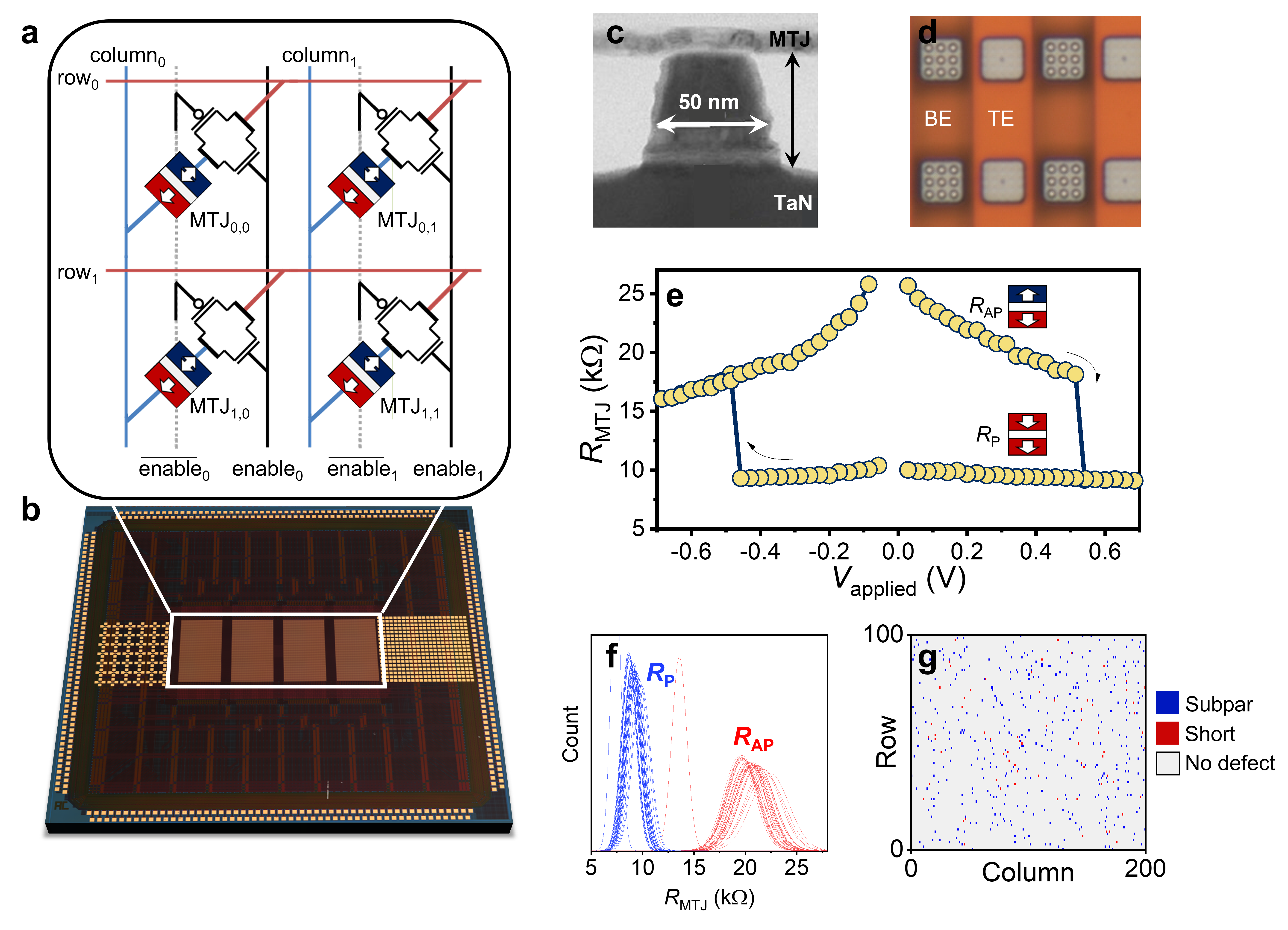

Measurement-driven neural-network training for integrated magnetic tunnel junction arrays

William A. Borders, Advait Madhavan, Matthew W. Daniels, Vasileia Georgiou, Martin Lueker-Boden, Tiffany S. Santos, Patrick M. Braganca, Mark D. Stiles, Jabez J. McClelland, Brian D. Hoskins

The increasing scale of neural networks needed to support more complex applications has led to an increasing requirement for area- and energy-efficient hardware. One route to meeting the budget for these applications is to circumvent the von Neumann bottleneck by performing computation in or near memory. An inevitability of transferring neural networks onto hardware is that non-idealities such as device-to-device variations or poor device yield impact performance. Methods such as hardware-aware training, where substrate non-idealities are incorporated during network training, are one way to recover performance at the cost of solution generality. In this work, we demonstrate inference on hardware neural networks consisting of 20,000 magnetic tunnel junction arrays integrated on a complementary metal-oxide-semiconductor chips that closely resembles market-ready spin transfer-torque magnetoresistive random access memory technology. Using 36 dies, each containing a crossbar array with its own non-idealities, we show that even a small number of defects in physically mapped networks significantly degrades the performance of networks trained without defects and show that, at the cost of generality, hardware-aware training accounting for specific defects on each die can recover to comparable performance with ideal networks. We then demonstrate a robust training method that extends hardware-aware training to statistics-aware training, producing network weights that perform well on most defective dies regardless of their specific defect locations. When evaluated on the 36 physical dies, statistics-aware trained solutions can achieve a mean misclassification error on the MNIST dataset that differs from the software-baseline by only 2 %. This statistics-aware training method could be generalized to networks with many layers that are mapped to hardware suited for industry-ready applications.

Read more5/15/2024