DeepGate3: Towards Scalable Circuit Representation Learning

0

Sign in to get full access

Overview

- This paper introduces DeepGate3, a new approach for scalable circuit representation learning.

- DeepGate3 aims to address the limitations of previous circuit representation learning methods, which have struggled to handle large-scale circuit designs.

- The paper proposes several key innovations, including a novel hierarchical graph neural network architecture and a novel training strategy, to enable efficient and scalable circuit representation learning.

Plain English Explanation

The paper discusses DeepGate3, a new method for representing and understanding the structure of electronic circuits. Circuits are complex, interconnected systems, and being able to effectively model and analyze them is important for tasks like circuit design, optimization, and verification.

Previous methods for representing circuits in a way that computers can understand have had some issues. They've struggled to handle very large, complex circuits that are common in modern electronics. DeepGate3 tries to address these limitations by using a hierarchical graph neural network - a type of machine learning model that can efficiently capture the structure and relationships within a circuit.

The key ideas behind DeepGate3 are:

- Using a hierarchical approach to break down large circuits into smaller, more manageable pieces.

- Designing a specialized neural network architecture that can effectively learn representations of these circuit components and how they fit together.

- Developing a novel training strategy to enable efficient and scalable learning of circuit representations.

By incorporating these innovations, the authors aim to create a circuit representation learning system that can handle the complexity of modern electronics much more effectively than previous approaches. This could have important applications in areas like circuit design automation, verification, and optimization.

Technical Explanation

The paper introduces DeepGate3, a new framework for scalable circuit representation learning. The key aspects of the technical approach are:

-

Hierarchical Graph Neural Network Architecture: DeepGate3 uses a hierarchical graph neural network (HGNN) to capture the multi-scale structure of circuits. The HGNN consists of multiple graph convolutional layers that operate at different levels of abstraction, from individual circuit components up to high-level circuit modules.

-

Adaptive Graph Pooling: To enable efficient learning on large circuits, DeepGate3 employs an adaptive graph pooling mechanism. This allows the model to dynamically adjust the granularity of the circuit representation, focusing computational resources on the most relevant circuit components.

-

Multi-Task Training: The DeepGate3 model is trained in a multi-task fashion, jointly learning representations for circuit topology, functionality, and performance. This helps the model capture a more comprehensive understanding of circuit behavior.

-

Efficient Training Strategy: The paper proposes a novel training strategy that incorporates circuit-specific pretraining and curriculum learning. This enables efficient and scalable training of the DeepGate3 model, even on very large circuit designs.

The authors evaluate DeepGate3 on a range of circuit-related tasks, including circuit classification, property prediction, and circuit generation. The results demonstrate significant performance improvements over state-of-the-art circuit representation learning methods, particularly on large-scale circuit designs.

Critical Analysis

The DeepGate3 paper presents a compelling approach for scalable circuit representation learning, addressing several limitations of prior methods. The hierarchical graph neural network architecture and adaptive pooling mechanism are well-designed innovations that enable efficient handling of large-scale circuit structures.

However, the paper does not fully explore the limitations and potential issues of the DeepGate3 approach. For example, it would be valuable to understand how the model performs on circuits with highly irregular or heterogeneous structures, which may pose challenges for the hierarchical decomposition. Additionally, the paper could delve deeper into the interpretability and explainability of the learned circuit representations, as this is an important consideration for many real-world applications.

Further research could also investigate the generalization capabilities of DeepGate3 to circuit design tasks beyond the specific benchmarks considered in the paper. Exploring the model's robustness to noise, variations, and distribution shifts in the input circuits would also be a valuable extension.

Overall, the DeepGate3 paper represents a significant contribution to the field of circuit representation learning, and the proposed techniques hold promise for enabling more scalable and effective circuit analysis and design. However, as with any research, there are opportunities for further refinement and exploration to fully realize the potential of this approach.

Conclusion

The DeepGate3 paper introduces a novel framework for scalable circuit representation learning, addressing key limitations of previous methods. By using a hierarchical graph neural network architecture and innovative training strategies, the authors have demonstrated significant improvements in the ability to effectively model and analyze large-scale circuit designs.

The core innovations of DeepGate3, including the hierarchical graph neural network, adaptive pooling, and multi-task training, provide a strong foundation for advancing the state of the art in circuit representation learning. This could have important implications for a wide range of applications, such as circuit design automation, verification, and optimization, where the ability to efficiently and accurately model circuit behavior is crucial.

While the paper presents a compelling technical approach, further research is needed to fully explore the limitations, generalization capabilities, and interpretability of the DeepGate3 model. Nonetheless, this work represents a significant step forward in the pursuit of scalable and effective circuit representation learning, which could ultimately lead to more efficient and reliable electronic systems.

This summary was produced with help from an AI and may contain inaccuracies - check out the links to read the original source documents!

Related Papers

0

DeepGate3: Towards Scalable Circuit Representation Learning

Zhengyuan Shi, Ziyang Zheng, Sadaf Khan, Jianyuan Zhong, Min Li, Qiang Xu

Circuit representation learning has shown promising results in advancing the field of Electronic Design Automation (EDA). Existing models, such as DeepGate Family, primarily utilize Graph Neural Networks (GNNs) to encode circuit netlists into gate-level embeddings. However, the scalability of GNN-based models is fundamentally constrained by architectural limitations, impacting their ability to generalize across diverse and complex circuit designs. To address these challenges, we introduce DeepGate3, an enhanced architecture that integrates Transformer modules following the initial GNN processing. This novel architecture not only retains the robust gate-level representation capabilities of its predecessor, DeepGate2, but also enhances them with the ability to model subcircuits through a novel pooling transformer mechanism. DeepGate3 is further refined with multiple innovative supervision tasks, significantly enhancing its learning process and enabling superior representation of both gate-level and subcircuit structures. Our experiments demonstrate marked improvements in scalability and generalizability over traditional GNN-based approaches, establishing a significant step forward in circuit representation learning technology.

Read more7/17/2024

0

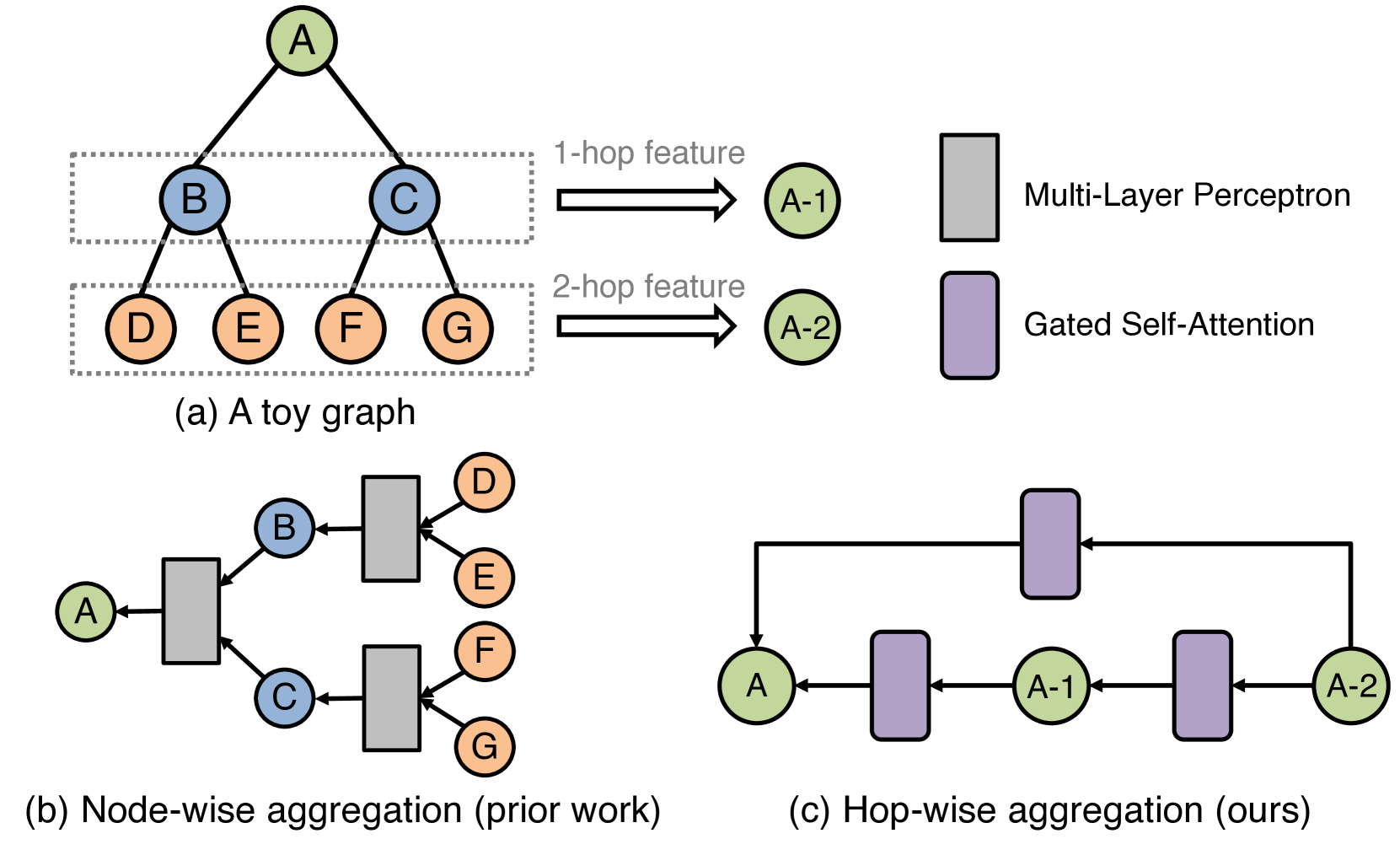

Less is More: Hop-Wise Graph Attention for Scalable and Generalizable Learning on Circuits

Chenhui Deng, Zichao Yue, Cunxi Yu, Gokce Sarar, Ryan Carey, Rajeev Jain, Zhiru Zhang

While graph neural networks (GNNs) have gained popularity for learning circuit representations in various electronic design automation (EDA) tasks, they face challenges in scalability when applied to large graphs and exhibit limited generalizability to new designs. These limitations make them less practical for addressing large-scale, complex circuit problems. In this work we propose HOGA, a novel attention-based model for learning circuit representations in a scalable and generalizable manner. HOGA first computes hop-wise features per node prior to model training. Subsequently, the hop-wise features are solely used to produce node representations through a gated self-attention module, which adaptively learns important features among different hops without involving the graph topology. As a result, HOGA is adaptive to various structures across different circuits and can be efficiently trained in a distributed manner. To demonstrate the efficacy of HOGA, we consider two representative EDA tasks: quality of results (QoR) prediction and functional reasoning. Our experimental results indicate that (1) HOGA reduces estimation error over conventional GNNs by 46.76% for predicting QoR after logic synthesis; (2) HOGA improves 10.0% reasoning accuracy over GNNs for identifying functional blocks on unseen gate-level netlists after complex technology mapping; (3) The training time for HOGA almost linearly decreases with an increase in computing resources.

Read more4/12/2024

0

VLSI Hypergraph Partitioning with Deep Learning

Muhammad Hadir Khan, Bugra Onal, Eren Dogan, Matthew R. Guthaus

Partitioning is a known problem in computer science and is critical in chip design workflows, as advancements in this area can significantly influence design quality and efficiency. Deep Learning (DL) techniques, particularly those involving Graph Neural Networks (GNNs), have demonstrated strong performance in various node, edge, and graph prediction tasks using both inductive and transductive learning methods. A notable area of recent interest within GNNs are pooling layers and their application to graph partitioning. While these methods have yielded promising results across social, computational, and other random graphs, their effectiveness has not yet been explored in the context of VLSI hypergraph netlists. In this study, we introduce a new set of synthetic partitioning benchmarks that emulate real-world netlist characteristics and possess a known upper bound for solution cut quality. We distinguish these benchmarks with the prior work and evaluate existing state-of-the-art partitioning algorithms alongside GNN-based approaches, highlighting their respective advantages and disadvantages.

Read more9/4/2024

0

The Dawn of AI-Native EDA: Opportunities and Challenges of Large Circuit Models

Lei Chen (Huawei Noah's Ark Lab), Yiqi Chen (Peking University), Zhufei Chu (Ningbo University), Wenji Fang (Hong Kong University of Science and Technology), Tsung-Yi Ho (The Chinese University of Hong Kong), Ru Huang (Peking University, Southeast University), Yu Huang (Huawei HiSilicon), Sadaf Khan (The Chinese University of Hong Kong), Min Li (Huawei Noah's Ark Lab), Xingquan Li (Peng Cheng Laboratory), Yu Li (The Chinese University of Hong Kong), Yun Liang (Peking University), Jinwei Liu (The Chinese University of Hong Kong), Yi Liu (The Chinese University of Hong Kong), Yibo Lin (Peking University), Guojie Luo (Peking University), Zhengyuan Shi (The Chinese University of Hong Kong), Guangyu Sun (Peking University), Dimitrios Tsaras (Huawei Noah's Ark Lab), Runsheng Wang (Peking University), Ziyi Wang (The Chinese University of Hong Kong), Xinming Wei (Peking University), Zhiyao Xie (Hong Kong University of Science and Technology), Qiang Xu (The Chinese University of Hong Kong), Chenhao Xue (Peking University), Junchi Yan (Shanghai Jiao Tong University), Jun Yang (Southeast University), Bei Yu (The Chinese University of Hong Kong), Mingxuan Yuan (Huawei Noah's Ark Lab), Evangeline F. Y. Young (The Chinese University of Hong Kong), Xuan Zeng (Fudan University), Haoyi Zhang (Peking University), Zuodong Zhang (Peking University), Yuxiang Zhao (Peking University), Hui-Ling Zhen (Huawei Noah's Ark Lab), Ziyang Zheng (The Chinese University of Hong Kong), Binwu Zhu (The Chinese University of Hong Kong), Keren Zhu (The Chinese University of Hong Kong), Sunan Zou (Peking University)

Within the Electronic Design Automation (EDA) domain, AI-driven solutions have emerged as formidable tools, yet they typically augment rather than redefine existing methodologies. These solutions often repurpose deep learning models from other domains, such as vision, text, and graph analytics, applying them to circuit design without tailoring to the unique complexities of electronic circuits. Such an AI4EDA approach falls short of achieving a holistic design synthesis and understanding, overlooking the intricate interplay of electrical, logical, and physical facets of circuit data. This paper argues for a paradigm shift from AI4EDA towards AI-native EDA, integrating AI at the core of the design process. Pivotal to this vision is the development of a multimodal circuit representation learning technique, poised to provide a comprehensive understanding by harmonizing and extracting insights from varied data sources, such as functional specifications, RTL designs, circuit netlists, and physical layouts. We champion the creation of large circuit models (LCMs) that are inherently multimodal, crafted to decode and express the rich semantics and structures of circuit data, thus fostering more resilient, efficient, and inventive design methodologies. Embracing this AI-native philosophy, we foresee a trajectory that transcends the current innovation plateau in EDA, igniting a profound shift-left in electronic design methodology. The envisioned advancements herald not just an evolution of existing EDA tools but a revolution, giving rise to novel instruments of design tools that promise to radically enhance design productivity and inaugurate a new epoch where the optimization of circuit performance, power, and area (PPA) is achieved not incrementally, but through leaps that redefine the benchmarks of electronic systems' capabilities.

Read more5/2/2024