Integrating SystemC-AMS Power Modeling with a RISC-V ISS for Virtual Prototyping of Battery-operated Embedded Devices

0

Sign in to get full access

Overview

- This paper presents a virtual prototyping approach that integrates SystemC-AMS power modeling with a RISC-V instruction set simulator (ISS) for the design and evaluation of battery-operated embedded devices.

- The goal is to enable early-stage power analysis and design space exploration to optimize the energy efficiency of embedded systems.

- The proposed architecture combines a RISC-V ISS with a SystemC-AMS model for power estimation, allowing for detailed simulation and analysis of power consumption at the hardware-software interface.

Plain English Explanation

The paper describes a new way to design and test battery-powered electronic devices, like those found in smartphones, wearables, or Internet of Things (IoT) gadgets. Designing these devices is challenging because engineers need to balance performance, features, and battery life.

The key idea is to use a "virtual prototype" - a computer simulation of the device's hardware and software. This allows engineers to experiment with different design choices and see how they impact power consumption, without having to build physical prototypes.

The virtual prototype combines two main components:

- A RISC-V processor simulator, which models the behavior of the device's main microprocessor.

- A power model built using SystemC-AMS, which estimates how much power the different hardware components will use.

By integrating these two pieces, engineers can get a detailed, early-stage understanding of how their design choices will affect the device's battery life. They can try out different processors, memory sizes, peripheral devices, and software algorithms, and see the tradeoffs in terms of power usage.

This helps identify power-hungry areas of the design and optimize them before building any physical hardware. It's like being able to test-drive a car digitally to check the fuel efficiency, rather than waiting until after it's manufactured.

Technical Explanation

The proposed virtual prototyping architecture consists of two main components:

-

RISC-V Instruction Set Simulator (ISS):

- This models the behavior of the embedded device's main processor, which is based on the open-source RISC-V instruction set.

- The ISS accurately simulates the execution of software running on the processor, including all the low-level hardware interactions.

-

SystemC-AMS Power Model:

- This models the power consumption of the various hardware components in the embedded device, such as the processor, memory, sensors, and peripherals.

- The SystemC-AMS framework allows creating detailed power models that capture the analog/mixed-signal nature of the hardware.

- These power models are integrated with the RISC-V ISS to provide cycle-accurate power estimation during the software execution.

By coupling the RISC-V ISS and the SystemC-AMS power model, the virtual prototyping platform enables early design space exploration. Engineers can experiment with different processor configurations, hardware peripherals, and software workloads, and immediately see the impact on the device's power consumption.

This allows them to identify power optimization opportunities and make informed decisions about the hardware-software co-design of the embedded system. The virtual prototype serves as a fast, flexible, and accurate tool for evaluating the energy efficiency of the device before committing to physical implementation.

Critical Analysis

The paper provides a thorough description of the virtual prototyping architecture and demonstrates its capabilities through several case studies. However, a few potential limitations or areas for further research are worth considering:

-

Validation of the power models: The accuracy of the power estimation ultimately depends on the fidelity of the SystemC-AMS power models. The paper mentions validation against measurements, but more extensive validation across a broader range of hardware and workloads could strengthen the confidence in the results.

-

Scalability to larger, more complex systems: The examples in the paper focus on relatively simple embedded systems. Applying this approach to larger, more complex systems with multiple processors, extensive peripherals, and complex software stacks could present additional challenges that need to be addressed.

-

Integration with higher-level system modeling: While the virtual prototype enables detailed hardware-software co-design, integrating it with higher-level system-level models (e.g., system-level power management, thermal effects) could provide a more holistic view of the embedded device's behavior and optimization opportunities.

-

Automation and tool support: Automating the process of generating and configuring the virtual prototype, as well as providing user-friendly interfaces for design space exploration, could further enhance the practicality and adoption of this approach in industrial settings.

Overall, the proposed virtual prototyping approach demonstrates promising capabilities for early-stage power-aware design of battery-operated embedded devices. Addressing the identified areas for improvement could further strengthen the utility and impact of this research.

Conclusion

This paper presents a virtual prototyping framework that tightly integrates a RISC-V instruction set simulator with a SystemC-AMS power modeling approach. This enables detailed simulation and analysis of power consumption for battery-operated embedded devices, allowing engineers to explore the design space and optimize energy efficiency early in the development process.

The key innovation is the seamless coupling of the processor simulation and the power modeling, which provides cycle-accurate power estimates during software execution. This enables designers to quickly evaluate the impact of hardware and software choices on the device's power consumption, without having to build physical prototypes.

The proposed virtual prototyping platform has the potential to significantly improve the design process for a wide range of battery-powered embedded systems, from smartphones and wearables to IoT devices. By providing a flexible, accurate, and efficient tool for power-aware design space exploration, this research can contribute to the development of more energy-efficient electronic devices that deliver enhanced performance and longer battery life.

This summary was produced with help from an AI and may contain inaccuracies - check out the links to read the original source documents!

Related Papers

0

Integrating SystemC-AMS Power Modeling with a RISC-V ISS for Virtual Prototyping of Battery-operated Embedded Devices

Mohamed Amine Hamdi, Giovanni Pollo, Matteo Risso, Germain Haugou, Alessio Burrello, Enrico Macii, Massimo Poncino, Sara Vinco, Daniele Jahier Pagliari

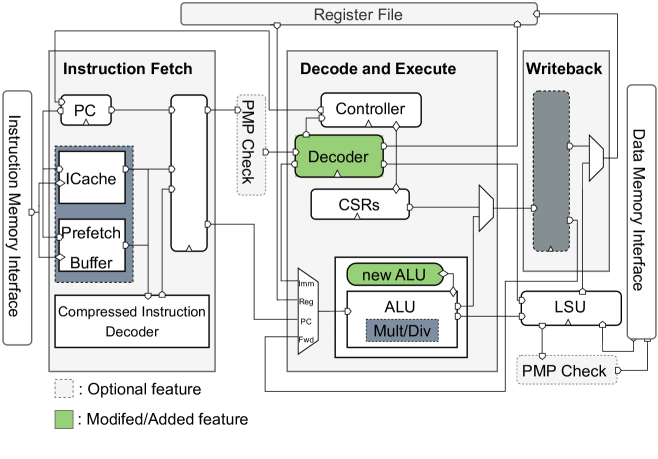

RISC-V cores have gained a lot of popularity over the last few years. However, being quite a recent and novel technology, there is still a gap in the availability of comprehensive simulation frameworks for RISC-V that cover both the functional and extra-functional aspects. This gap hinders progress in the field, as fast yet accurate system-level simulation is crucial for Design Space Exploration (DSE). This work presents an open-source framework designed to tackle this challenge, integrating functional RISC-V simulation (achieved with GVSoC) with SystemC-AMS (used to model extra-functional aspects, in detail power storage and distribution). The combination of GVSoC and SystemC-AMS in a single simulation framework allows to perform a DSE that is dependent on the mutual impact between functional and extra-functional aspects. In our experiments, we validate the framework's effectiveness by creating a virtual prototype of a compact, battery-powered embedded system.

Read more4/3/2024

0

Mixed-precision Neural Networks on RISC-V Cores: ISA extensions for Multi-Pumped Soft SIMD Operations

Giorgos Armeniakos, Alexis Maras, Sotirios Xydis, Dimitrios Soudris

Recent advancements in quantization and mixed-precision approaches offers substantial opportunities to improve the speed and energy efficiency of Neural Networks (NN). Research has shown that individual parameters with varying low precision, can attain accuracies comparable to full-precision counterparts. However, modern embedded microprocessors provide very limited support for mixed-precision NNs regarding both Instruction Set Architecture (ISA) extensions and their hardware design for efficient execution of mixed-precision operations, i.e., introducing several performance bottlenecks due to numerous instructions for data packing and unpacking, arithmetic unit under-utilizations etc. In this work, we bring together, for the first time, ISA extensions tailored to mixed-precision hardware optimizations, targeting energy-efficient DNN inference on leading RISC-V CPU architectures. To this end, we introduce a hardware-software co-design framework that enables cooperative hardware design, mixed-precision quantization, ISA extensions and inference in cycle-accurate emulations. At hardware level, we firstly expand the ALU unit within our proof-of-concept micro-architecture to support configurable fine grained mixed-precision arithmetic operations. Subsequently, we implement multi-pumping to minimize execution latency, with an additional soft SIMD optimization applied for 2-bit operations. At the ISA level, three distinct MAC instructions are encoded extending the RISC-V ISA, and exposed up to the compiler level, each corresponding to a different mixed-precision operational mode. Our extensive experimental evaluation over widely used DNNs and datasets, such as CIFAR10 and ImageNet, demonstrates that our framework can achieve, on average, 15x energy reduction for less than 1% accuracy loss and outperforms the ISA-agnostic state-of-the-art RISC-V cores.

Read more8/14/2024

✨

0

Preserving Power Optimizations Across the High Level Synthesis of Distinct Application-Specific Circuits

Paulo Garcia

We evaluate the use of software interpretation to push High Level Synthesis of application-specific accelerators toward a higher level of abstraction. Our methodology is supported by a formal power consumption model that computes the power consumption of accelerator components, accurately predicting the power consumption on new designs from prior optimization estimations. We demonstrate how our approach simplifies the re-use of power optimizations across distinct designs, by leveraging the higher level of design abstraction, using two accelerators representative of the robotics domain, implemented through the Bambu High Level Synthesis tool. Results support the research hypothesis, achieving predictions accurate within +/- 1%.

Read more7/10/2024

0

Vessim: A Testbed for Carbon-Aware Applications and Systems

Philipp Wiesner, Ilja Behnke, Paul Kilian, Marvin Steinke, Odej Kao

To reduce the carbon footprint of computing and stabilize electricity grids, there is an increasing focus on approaches that align the power usage of IT infrastructure with the availability of clean energy. Unfortunately, research on energy-aware and carbon-aware applications, as well as the interfaces between computing and energy systems, remains complex due to the scarcity of available testing environments. To this day, almost all new approaches are evaluated on custom simulation testbeds, which leads to repeated development efforts and limited comparability of results. In this paper, we present Vessim, a co-simulation environment for testing applications and computing systems that interact with their energy systems. Our testbed connects domain-specific simulators for renewable power generation and energy storage, and enables users to implement interfaces to integrate real systems through software and hardware-in-the-loop simulation. Vessim offers an easy-to-use interface, is extendable to new simulators, and provides direct access to historical datasets. We aim to not only accelerate research in carbon-aware computing but also facilitate development and operation, as in continuous testing or digital twins. Vessim is publicly available: https://github.com/dos-group/vessim.

Read more6/21/2024