Low Latency Transformer Inference on FPGAs for Physics Applications with hls4ml

0

Sign in to get full access

Overview

- The paper explores using FPGAs (Field Programmable Gate Arrays) to accelerate the inference of Transformer models for physics applications, such as those used in LIGO (Laser Interferometer Gravitational-Wave Observatory) data analysis.

- The researchers leverage the hls4ml (High-Level Synthesis for Machine Learning) tool to efficiently implement Transformer models on FPGAs, achieving low-latency inference.

- The key focus is on optimizing Transformer inference for high-energy physics applications, where low-latency is crucial for real-time data processing.

Plain English Explanation

The paper discusses how researchers are using a special type of hardware called FPGAs to run machine learning models, specifically Transformer models, more efficiently. Transformer models are a type of machine learning model that has been very successful in many applications, including analyzing data from physics experiments like LIGO.

The challenge is that running these Transformer models on regular computers can be slow, which is a problem for physics experiments that need to process data in real-time. The researchers in this paper found a way to use FPGAs, which are a type of programmable hardware, to run the Transformer models much faster. They used a tool called hls4ml to help them efficiently implement the Transformer models on the FPGA hardware.

By using FPGAs and the hls4ml tool, the researchers were able to achieve low-latency inference of the Transformer models, meaning the models could process the data very quickly. This is important for physics applications like LIGO, where the data needs to be analyzed in real-time to detect things like gravitational waves.

Technical Explanation

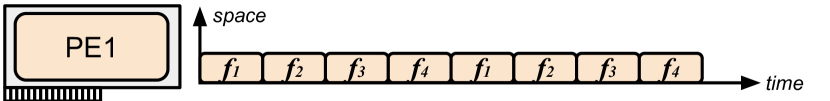

The paper investigates the use of FPGAs to accelerate the inference of Transformer models for physics applications, leveraging the hls4ml (High-Level Synthesis for Machine Learning) tool. FPGAs are a type of programmable hardware that can be customized to efficiently execute specific computational tasks, making them well-suited for low-latency machine learning inference.

The researchers focus on optimizing Transformer inference for high-energy physics applications, where low-latency is crucial for real-time data processing. They utilize the hls4ml framework to automatically generate FPGA-optimized implementations of Transformer models, allowing for efficient mapping of the model's computations onto the FPGA fabric.

The paper evaluates the performance of the FPGA-accelerated Transformer inference on several physics-related datasets, including LIGO data analysis tasks. The results demonstrate significant improvements in latency and throughput compared to CPU-based inference, making the FPGA-based approach well-suited for real-time applications in high-energy physics.

Critical Analysis

The paper provides a compelling demonstration of the potential for FPGA-based acceleration of Transformer models in physics applications. The use of the hls4ml tool to efficiently map the Transformer architecture onto FPGA hardware is a notable contribution, as it simplifies the process of deploying these models on specialized hardware.

However, the paper does not address some potential limitations or areas for further research. For example, the scalability of the FPGA-based approach as the size and complexity of Transformer models continue to grow is not discussed. Additionally, the power efficiency and energy consumption of the FPGA-based inference compared to other hardware platforms, such as GPUs or specialized AI accelerators, could be an interesting area for further investigation.

Furthermore, the paper focuses primarily on the performance metrics of latency and throughput, but does not provide a comprehensive analysis of the trade-offs between these metrics and other factors, such as model accuracy or resource utilization. Exploring these trade-offs could help inform the selection of the most appropriate hardware platform for different physics applications.

Conclusion

The paper demonstrates the potential of using FPGAs to accelerate the inference of Transformer models for physics applications, such as those used in LIGO data analysis. By leveraging the hls4ml tool, the researchers were able to efficiently implement Transformer models on FPGA hardware, achieving significant improvements in latency and throughput compared to CPU-based inference.

The results highlight the growing importance of specialized hardware, like FPGAs, in the field of machine learning, particularly for real-time applications where low-latency is a critical requirement. As Transformer models continue to advance and become more widely adopted in scientific domains, the ability to deploy these models on power-efficient and low-latency hardware platforms will be increasingly valuable.

The research presented in this paper lays the groundwork for further exploration of FPGA-based acceleration of machine learning models in high-energy physics and other domains where low-latency inference is essential.

This summary was produced with help from an AI and may contain inaccuracies - check out the links to read the original source documents!

Related Papers

0

Low Latency Transformer Inference on FPGAs for Physics Applications with hls4ml

Zhixing Jiang, Dennis Yin, Yihui Chen, Elham E Khoda, Scott Hauck, Shih-Chieh Hsu, Ekaterina Govorkova, Philip Harris, Vladimir Loncar, Eric A. Moreno

This study presents an efficient implementation of transformer architectures in Field-Programmable Gate Arrays(FPGAs) using hls4ml. We demonstrate the strategy for implementing the multi-head attention, softmax, and normalization layer and evaluate three distinct models. Their deployment on VU13P FPGA chip achieved latency less than 2us, demonstrating the potential for real-time applications. HLS4ML compatibility with any TensorFlow-built transformer model further enhances the scalability and applicability of this work. Index Terms: FPGAs, machine learning, transformers, high energy physics, LIGO

Read more9/10/2024

🤯

0

HLSTransform: Energy-Efficient Llama 2 Inference on FPGAs Via High Level Synthesis

Andy He, Darren Key, Mason Bulling, Andrew Chang, Skyler Shapiro, Everett Lee

Graphics Processing Units (GPUs) have become the leading hardware accelerator for deep learning applications and are used widely in training and inference of transformers; transformers have achieved state-of-the-art performance in many areas of machine learning and are especially used in most modern Large Language Models (LLMs). However, GPUs require large amounts of energy, which poses environmental concerns, demands high operational costs, and causes GPUs to be unsuitable for edge computing. We develop an accelerator for transformers, namely, Llama 2, an open-source state-of-the-art LLM, using high level synthesis (HLS) on Field Programmable Gate Arrays (FPGAs). HLS allows us to rapidly prototype FPGA designs without writing code at the register-transfer level (RTL). We name our method HLSTransform, and the FPGA designs we synthesize with HLS achieve up to a 12.75x reduction and 8.25x reduction in energy used per token on the Xilinx Virtex UltraScale+ VU9P FPGA compared to an Intel Xeon Broadwell E5-2686 v4 CPU and NVIDIA RTX 3090 GPU respectively, while increasing inference speeds by up to 2.46x compared to CPU and maintaining 0.53x the speed of an RTX 3090 GPU despite the GPU's 4 times higher base clock rate. With the lack of existing open-source FPGA accelerators for transformers, we open-source our code and document our steps for synthesis. We hope this work will serve as a step in democratizing the use of FPGAs in transformer inference and inspire research into energy-efficient inference methods as a whole. The code can be found on https://github.com/HLSTransform/submission.

Read more5/3/2024

➖

0

The Feasibility of Implementing Large-Scale Transformers on Multi-FPGA Platforms

Yu Gao, Juan Camilo Vega, Paul Chow

FPGAs are rarely mentioned when discussing the implementation of large machine learning applications, such as Large Language Models (LLMs), in the data center. There has been much evidence showing that single FPGAs can be competitive with GPUs in performance for some computations, especially for low latency, and often much more efficient when power is considered. This suggests that there is merit to exploring the use of multiple FPGAs for large machine learning applications. The challenge with using multiple FPGAs is that there is no commonly-accepted flow for developing and deploying multi-FPGA applications, i.e., there are no tools to describe a large application, map it to multiple FPGAs and then deploy the application on a multi-FPGA platform. In this paper, we explore the feasibility of implementing large transformers using multiple FPGAs by developing a scalable multi-FPGA platform and some tools to map large applications to the platform. We validate our approach by designing an efficient multi-FPGA version of the I-BERT transformer and implement one encoder using six FPGAs as a working proof-of-concept to show that our platform and tools work. Based on our proof-of-concept prototype and the estimations of performance using the latest FPGAs compared to GPUs, we conclude that there can be a place for FPGAs in the world of large machine learning applications. We demonstrate a promising first step that shows that with the right infrastructure and tools it is reasonable to continue to explore the possible benefits of using FPGAs for applications such as LLMs.

Read more4/26/2024

0

Understanding the Potential of FPGA-Based Spatial Acceleration for Large Language Model Inference

Hongzheng Chen, Jiahao Zhang, Yixiao Du, Shaojie Xiang, Zichao Yue, Niansong Zhang, Yaohui Cai, Zhiru Zhang

Recent advancements in large language models (LLMs) boasting billions of parameters have generated a significant demand for efficient deployment in inference workloads. The majority of existing approaches rely on temporal architectures that reuse hardware units for different network layers and operators. However, these methods often encounter challenges in achieving low latency due to considerable memory access overhead. This paper investigates the feasibility and potential of model-specific spatial acceleration for LLM inference on FPGAs. Our approach involves the specialization of distinct hardware units for specific operators or layers, facilitating direct communication between them through a dataflow architecture while minimizing off-chip memory accesses. We introduce a comprehensive analytical model for estimating the performance of a spatial LLM accelerator, taking into account the on-chip compute and memory resources available on an FPGA. Through our analysis, we can determine the scenarios in which FPGA-based spatial acceleration can outperform its GPU-based counterpart. To enable more productive implementations of an LLM model on FPGAs, we further provide a library of high-level synthesis (HLS) kernels that are composable and reusable. This library will be made available as open-source. To validate the effectiveness of both our analytical model and HLS library, we have implemented BERT and GPT2 on an AMD Alveo U280 FPGA device. Experimental results demonstrate our approach can achieve up to 13.4x speedup when compared to previous FPGA-based accelerators for the BERT model. For GPT generative inference, we attain a 2.2x speedup compared to DFX, an FPGA overlay, in the prefill stage, while achieving a 1.9x speedup and a 5.7x improvement in energy efficiency compared to the NVIDIA A100 GPU in the decode stage.

Read more4/9/2024