Mapping Large Memory-constrained Workflows onto Heterogeneous Platforms

0

Sign in to get full access

Overview

- This paper explores techniques for efficiently mapping large, memory-constrained workflows onto heterogeneous computing platforms.

- The authors focus on the challenges of partitioning and scheduling such workflows while adhering to memory constraints.

- The proposed approaches aim to improve the performance and resource utilization of these workflows on diverse hardware architectures.

Plain English Explanation

In the world of computing, there are often complex tasks, known as "workflows," that need to be carried out. These workflows can involve multiple steps, data processing, and various types of hardware to complete the job. The challenge arises when these workflows are large in scale and have strict memory constraints, meaning they can only use a limited amount of available memory.

The researchers in this paper tackled this problem by developing techniques to efficiently map these large, memory-constrained workflows onto heterogeneous computing platforms. Heterogeneous platforms refer to a mix of different types of hardware, such as CPUs, GPUs, and specialized accelerators.

The key aspects of their approach involve:

-

Partitioning the Workflow: The researchers developed methods to break down the workflow into smaller, manageable pieces, or "partitions," while ensuring that these partitions fit within the available memory constraints.

-

Scheduling the Partitions: Once the workflow is partitioned, the researchers focused on scheduling the execution of these partitions on the heterogeneous computing resources in the most efficient way. This involves deciding which tasks should run on which hardware components to optimize performance and resource utilization.

By addressing these challenges, the researchers aimed to improve the overall performance and efficiency of large, memory-constrained workflows running on diverse hardware setups. This can have significant implications for a wide range of applications, from data analysis and scientific computing to machine learning and distributed data processing.

Technical Explanation

The paper presents a framework for mapping large, memory-constrained workflows onto heterogeneous computing platforms. The key components of their approach include:

-

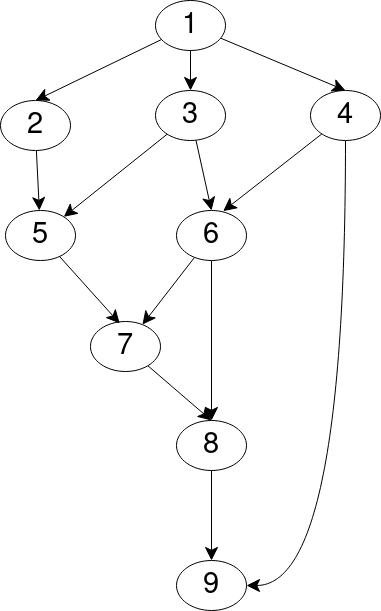

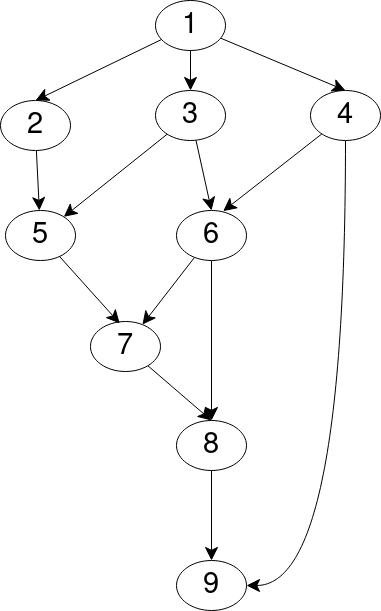

Workflow Representation: The authors model the workflow as a Directed Acyclic Graph (DAG), where nodes represent tasks and edges represent data dependencies between tasks.

-

Partitioning the Workflow: To address memory constraints, the researchers develop a partitioning algorithm that divides the workflow DAG into smaller partitions, ensuring that each partition fits within the available memory.

-

Scheduling the Partitions: The authors propose a scheduling algorithm that considers the memory requirements of each partition and assigns them to the appropriate hardware resources (e.g., CPUs, GPUs, accelerators) to optimize performance and resource utilization.

-

Heterogeneous Platform Modeling: The researchers model the heterogeneous computing platform, including the various hardware components and their characteristics (e.g., processing power, memory capacity, power consumption), to inform the partitioning and scheduling decisions.

The authors evaluate their approaches through extensive simulations, comparing their techniques to existing methods. They demonstrate significant improvements in terms of workflow completion time, resource utilization, and energy efficiency.

Critical Analysis

The researchers have identified an important problem in the field of workflow management and resource allocation on heterogeneous computing platforms. Their partitioning and scheduling algorithms aim to address the challenges posed by memory constraints, which is a crucial concern for many real-world applications.

One potential limitation of the study is that it is primarily based on simulations and does not include a thorough evaluation on actual hardware setups. While the simulation results are promising, it would be valuable to see how the proposed techniques perform in real-world deployments, where additional factors, such as network latency and system-level overheads, may come into play.

Additionally, the paper does not explicitly address the potential trade-offs between different optimization objectives, such as performance, resource utilization, and energy consumption. In practice, there may be scenarios where these objectives conflict, and the researchers could explore techniques to balance these tradeoffs.

Further research could also investigate the adaptability of the proposed algorithms to dynamic changes in the workflow or the computing environment, as real-world workflows often face unpredictable conditions and resource availability.

Conclusion

This paper presents a comprehensive framework for efficiently mapping large, memory-constrained workflows onto heterogeneous computing platforms. The key innovations include workflow partitioning and scheduling algorithms that consider memory constraints and the heterogeneous nature of the underlying hardware.

The researchers have demonstrated the potential of their techniques through extensive simulations, showing improvements in workflow completion time, resource utilization, and energy efficiency. While the study is primarily based on simulations, the findings suggest that the proposed approach could have significant practical implications for a wide range of applications that rely on complex, memory-intensive workflows.

Overall, this work contributes to the ongoing efforts to optimize the performance and efficiency of large-scale computing tasks on diverse hardware architectures, paving the way for more effective utilization of available resources and potentially enabling new classes of computationally-intensive applications.

This summary was produced with help from an AI and may contain inaccuracies - check out the links to read the original source documents!

Related Papers

0

Mapping Large Memory-constrained Workflows onto Heterogeneous Platforms

Svetlana Kulagina, Henning Meyerhenke, Anne Benoit

Scientific workflows are often represented as directed acyclic graphs (DAGs), where vertices correspond to tasks and edges represent the dependencies between them. Since these graphs are often large in both the number of tasks and their resource requirements, it is important to schedule them efficiently on parallel or distributed compute systems. Typically, each task requires a certain amount of memory to be executed and needs to communicate data to its successor tasks. The goal is thus to execute the workflow as fast as possible (i.e., to minimize its makespan) while satisfying the memory constraints. Hence, we investigate the partitioning and mapping of DAG-shaped workflows onto heterogeneous platforms where each processor can have a different speed and a different memory size. We first propose a baseline algorithm in the absence of existing memory-aware solutions. As our main contribution, we then present a four-step heuristic. Its first step is to partition the input DAG into smaller blocks with an existing DAG partitioner. The next two steps adapt the resulting blocks of the DAG to fit the processor memories and optimize for the overall makespan by further splitting and merging these blocks. Finally, we use local search via block swaps to further improve the makespan. Our experimental evaluation on real-world and simulated workflows with up to 30,000 tasks shows that exploiting the heterogeneity with the four-step heuristic reduces the makespan by a factor of 2.44 on average (even more on large workflows), compared to the baseline that ignores heterogeneity.

Read more7/15/2024

🔄

0

Efficient Multi-Processor Scheduling in Increasingly Realistic Models

P'al Andr'as Papp, Georg Anegg, Aikaterini Karanasiou, A. N. Yzelman

We study the problem of efficiently scheduling a computational DAG on multiple processors. The majority of previous works have developed and compared algorithms for this problem in relatively simple models; in contrast to this, we analyze this problem in a more realistic model that captures many real-world aspects, such as communication costs, synchronization costs, and the hierarchical structure of modern processing architectures. For this we extend the well-established BSP model of parallel computing with non-uniform memory access (NUMA) effects. We then develop a range of new scheduling algorithms to minimize the scheduling cost in this more complex setting: several initialization heuristics, a hill-climbing local search method, and several approaches that formulate (and solve) the scheduling problem as an Integer Linear Program (ILP). We combine these algorithms into a single framework, and conduct experiments on a diverse set of real-world computational DAGs to show that the resulting scheduler significantly outperforms both academic and practical baselines. In particular, even without NUMA effects, our scheduler finds solutions of 24%-44% smaller cost on average than the baselines, and in case of NUMA effects, it achieves up to a factor $2.5times$ improvement compared to the baselines. Finally, we also develop a multilevel scheduling algorithm, which provides up to almost a factor $5times$ improvement in the special case when the problem is dominated by very high communication costs.

Read more4/24/2024

🤿

0

Automated Deep Neural Network Inference Partitioning for Distributed Embedded Systems

Fabian Kress, El Mahdi El Annabi, Tim Hotfilter, Julian Hoefer, Tanja Harbaum, Juergen Becker

Distributed systems can be found in various applications, e.g., in robotics or autonomous driving, to achieve higher flexibility and robustness. Thereby, data flow centric applications such as Deep Neural Network (DNN) inference benefit from partitioning the workload over multiple compute nodes in terms of performance and energy-efficiency. However, mapping large models on distributed embedded systems is a complex task, due to low latency and high throughput requirements combined with strict energy and memory constraints. In this paper, we present a novel approach for hardware-aware layer scheduling of DNN inference in distributed embedded systems. Therefore, our proposed framework uses a graph-based algorithm to automatically find beneficial partitioning points in a given DNN. Each of these is evaluated based on several essential system metrics such as accuracy and memory utilization, while considering the respective system constraints. We demonstrate our approach in terms of the impact of inference partitioning on various performance metrics of six different DNNs. As an example, we can achieve a 47.5 % throughput increase for EfficientNet-B0 inference partitioned onto two platforms while observing high energy-efficiency.

Read more7/1/2024

0

Ponder: Online Prediction of Task Memory Requirements for Scientific Workflows

Fabian Lehmann, Jonathan Bader, Ninon De Mecquenem, Xing Wang, Vasilis Bountris, Florian Friederici, Ulf Leser, Lauritz Thamsen

Scientific workflows are used to analyze large amounts of data. These workflows comprise numerous tasks, many of which are executed repeatedly, running the same custom program on different inputs. Users specify resource allocations for each task, which must be sufficient for all inputs to prevent task failures. As a result, task memory allocations tend to be overly conservative, wasting precious cluster resources, limiting overall parallelism, and increasing workflow makespan. In this paper, we first benchmark a state-of-the-art method on four real-life workflows from the nf-core workflow repository. This analysis reveals that certain assumptions underlying current prediction methods, which typically were evaluated only on simulated workflows, cannot generally be confirmed for real workflows and executions. We then present Ponder, a new online task-sizing strategy that considers and chooses between different methods to cater to different memory demand patterns. We implemented Ponder for Nextflow and made the code publicly available. In an experimental evaluation that also considers the impact of memory predictions on scheduling, Ponder improves Memory Allocation Quality on average by 71.0% and makespan by 21.8% in comparison to a state-of-the-art method. Moreover, Ponder produces 93.8% fewer task failures.

Read more8/2/2024