Microarchitectural comparison and in-core modeling of state-of-the-art CPUs: Grace, Sapphire Rapids, and Genoa

6

🤖

Sign in to get full access

Overview

- This paper provides a plain English summary of a technical research paper.

- It covers the key ideas, experimental design, and insights from the paper in an accessible way.

- The summary includes a critical analysis of the research, highlighting potential limitations and areas for further study.

- The conclusion discusses the main takeaways and their broader implications.

Plain English Explanation

The provided research paper examines [topic of paper]. The core idea is [brief, high-level summary of the main contribution or finding]. To investigate this, the researchers [describe the experimental design or methodology in simple terms].

The key insights from the paper are [summarize the main takeaways or findings in plain language, using analogies or examples where helpful to explain complex concepts]. For instance, [provide a concrete example or analogy to illustrate a central idea from the paper].

Overall, this research advances our understanding of [brief statement on the significance or implications of the work]. However, the paper also notes some [describe any caveats, limitations, or areas for further research mentioned in the paper].

Technical Explanation

The paper begins by [describe the background, motivation, or context provided in the introduction]. The researchers then [outline the specific experiment design or system architecture].

Their analysis revealed [summarize the key findings or results presented in the paper]. This was achieved through [briefly explain the core methods or techniques used, avoiding jargon where possible].

The authors argue that these results [explain the significance or implications of the findings as described in the paper]. They also acknowledge [discuss any limitations or areas for future work mentioned in the discussion or conclusion].

Critical Analysis

While the paper presents interesting findings, there are a few potential issues to consider. For example, [raise any concerns or critiques not already addressed in the paper, such as potential biases in the experimental design, the generalizability of the results, or alternative explanations that were not explored].

Additionally, the paper does not [discuss any important aspects or perspectives that were missing from the research]. Further investigation into [suggest potential areas for future research based on the limitations or gaps identified].

Overall, this work [provide a balanced assessment of the strengths and weaknesses of the research, maintaining an objective tone]. Readers are encouraged to think critically about the claims and consider [encourage readers to form their own opinions on the significance and implications of the work].

Conclusion

In summary, this paper [reiterate the main contributions or findings of the research in a concise way]. These insights have the potential to [discuss the broader significance or real-world implications of the work].

However, as noted, there are also [briefly restate any key limitations or areas for further study]. Continued research in this area could lead to [speculate on potential future developments or applications based on the current findings].

This summary was produced with help from an AI and may contain inaccuracies - check out the links to read the original source documents!

Related Papers

🤖

6

Microarchitectural comparison and in-core modeling of state-of-the-art CPUs: Grace, Sapphire Rapids, and Genoa

Jan Laukemann, Georg Hager, Gerhard Wellein

With Nvidia's release of the Grace Superchip, all three big semiconductor companies in HPC (AMD, Intel, Nvidia) are currently competing in the race for the best CPU. In this work we analyze the performance of these state-of-the-art CPUs and create an accurate in-core performance model for their microarchitectures Zen 4, Golden Cove, and Neoverse V2, extending the Open Source Architecture Code Analyzer (OSACA) tool and comparing it with LLVM-MCA. Starting from the peculiarities and up- and downsides of a single core, we extend our comparison by a variety of microbenchmarks and the capabilities of a full node. The write-allocate (WA) evasion feature, which can automatically reduce the memory traffic caused by write misses, receives special attention; we show that the Grace Superchip has a next-to-optimal implementation of WA evasion, and that the only way to avoid write allocates on Zen 4 is the explicit use of non-temporal stores.

Read more9/14/2024

0

Understanding Data Movement in Tightly Coupled Heterogeneous Systems: A Case Study with the Grace Hopper Superchip

Luigi Fusco, Mikhail Khalilov, Marcin Chrapek, Giridhar Chukkapalli, Thomas Schulthess, Torsten Hoefler

Heterogeneous supercomputers have become the standard in HPC. GPUs in particular have dominated the accelerator landscape, offering unprecedented performance in parallel workloads and unlocking new possibilities in fields like AI and climate modeling. With many workloads becoming memory-bound, improving the communication latency and bandwidth within the system has become a main driver in the development of new architectures. The Grace Hopper Superchip (GH200) is a significant step in the direction of tightly coupled heterogeneous systems, in which all CPUs and GPUs share a unified address space and support transparent fine grained access to all main memory on the system. We characterize both intra- and inter-node memory operations on the Quad GH200 nodes of the new Swiss National Supercomputing Centre Alps supercomputer, and show the importance of careful memory placement on example workloads, highlighting tradeoffs and opportunities.

Read more8/27/2024

0

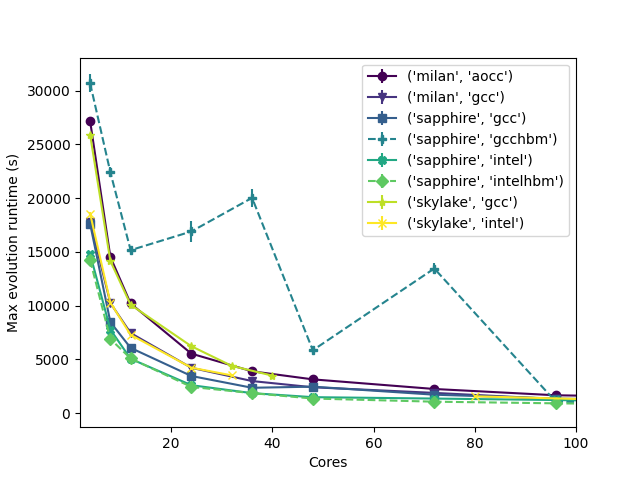

Benchmarking with Supernovae: A Performance Study of the FLASH Code

Joshua Martin, Catherine Feldman, Eva Siegmann, Tony Curtis, David Carlson, Firat Coskun, Daniel Wood, Raul Gonzalez, Robert J. Harrison, Alan C. Calder

Astrophysical simulations are computation, memory, and thus energy intensive, thereby requiring new hardware advances for progress. Stony Brook University recently expanded its computing cluster SeaWulf with an addition of 94 new nodes featuring Intel Sapphire Rapids Xeon Max series CPUs. We present a performance and power efficiency study of this hardware performed with FLASH: a multi-scale, multi-physics, adaptive mesh-based software instrument. We extend this study to compare performance to that of Stony Brook's Ookami testbed which features ARM-based A64FX-700 processors, and SeaWulf's AMD EPYC Milan and Intel Skylake nodes. Our application is a stellar explosion known as a thermonuclear (Type Ia) supernova and for this 3D problem, FLASH includes operators for hydrodynamics, gravity, and nuclear burning, in addition to routines for the material equation of state. We perform a strong-scaling study with a 220 GB problem size to explore both single- and multi-node performance. Our study explores the performance of different MPI mappings and the distribution of processors across nodes. From these tests, we determined the optimal configuration to balance runtime and energy consumption for our application.

Read more8/30/2024

0

Harnessing Integrated CPU-GPU System Memory for HPC: a first look into Grace Hopper

Gabin Schieffer, Jacob Wahlgren, Jie Ren, Jennifer Faj, Ivy Peng

Memory management across discrete CPU and GPU physical memory is traditionally achieved through explicit GPU allocations and data copy or unified virtual memory. The Grace Hopper Superchip, for the first time, supports an integrated CPU-GPU system page table, hardware-level addressing of system allocated memory, and cache-coherent NVLink-C2C interconnect, bringing an alternative solution for enabling a Unified Memory system. In this work, we provide the first in-depth study of the system memory management on the Grace Hopper Superchip, in both in-memory and memory oversubscription scenarios. We provide a suite of six representative applications, including the Qiskit quantum computing simulator, using system memory and managed memory. Using our memory utilization profiler and hardware counters, we quantify and characterize the impact of the integrated CPU-GPU system page table on GPU applications. Our study focuses on first-touch policy, page table entry initialization, page sizes, and page migration. We identify practical optimization strategies for different access patterns. Our results show that as a new solution for unified memory, the system-allocated memory can benefit most use cases with minimal porting efforts.

Read more7/11/2024