Multi-Objective Neural Architecture Search for In-Memory Computing

0

Sign in to get full access

Overview

- This paper presents a multi-objective neural architecture search (MONAS) approach for designing in-memory computing (IMC) systems.

- The goal is to optimize neural network architectures for IMC hardware, considering objectives like power, latency, and accuracy.

- The authors use a multi-objective Bayesian optimization algorithm to efficiently explore the design space and identify optimal architectures.

Plain English Explanation

The researchers have developed a technique to help design specialized computer chips that can perform machine learning tasks more efficiently. These chips, called in-memory computing (IMC) systems, can perform calculations directly on the memory, rather than moving data back and forth between memory and a separate processor. This can save a lot of power and time.

However, designing the best neural network architecture for these IMC chips is a complex challenge. The researchers used a technique called multi-objective neural architecture search (MONAS) to explore many different neural network designs and find the ones that offer the best tradeoffs between important factors like power usage, speed, and accuracy.

Link to paper on multi-objective hardware-aware neural architecture search

They used a kind of optimization algorithm called Bayesian optimization to efficiently search through the vast space of possible neural network designs. This allowed them to identify optimal architectures that work well with the constraints and capabilities of IMC hardware.

The key innovation here is using a multi-objective approach to simultaneously optimize for multiple goals, rather than just trying to maximize accuracy. This helps ensure the resulting neural network designs are well-suited for practical IMC deployment, not just theoretically accurate.

Technical Explanation

The paper introduces a multi-objective neural architecture search (MONAS) approach for designing neural networks optimized for in-memory computing (IMC) hardware.

IMC systems can perform computations directly in memory, avoiding the high energy costs of data movement between memory and a separate processor. However, designing neural network architectures that can efficiently leverage IMC hardware is challenging, as it requires optimizing for multiple objectives like power, latency, and accuracy.

The authors propose a multi-objective Bayesian optimization algorithm to efficiently explore the design space and identify Pareto-optimal neural network architectures for IMC. The algorithm uses a surrogate model to approximate the underlying objective functions, allowing it to intelligently sample the most promising regions of the search space.

The authors evaluate their MONAS approach on image classification and natural language processing tasks, comparing the resulting IMC-optimized architectures to standard neural networks. They demonstrate significant improvements in power and latency compared to baseline models, while maintaining comparable accuracy.

Critical Analysis

The paper presents a compelling approach to the important challenge of designing neural network architectures tailored for in-memory computing hardware. The multi-objective optimization framework allows the authors to navigate the complex tradeoffs between power, latency, and accuracy in a principled manner.

One potential limitation is the reliance on a particular IMC hardware model (memristive crossbars) in the experiments. While this is a reasonable choice, the generalization of the MONAS approach to other IMC architectures, such as SPIKENAS, could be explored further.

Additionally, the authors acknowledge that the current MONAS framework does not consider the carbon footprint of the hardware, which is an increasingly important consideration for real-world deployment. Extending the approach to include end-to-end carbon efficiency as an optimization objective could be a valuable direction for future research.

Overall, this work represents a significant contribution to the field of hardware-aware neural architecture search, and the MONAS technique could have wide-ranging implications for the design of energy-efficient AI systems.

Conclusion

This paper presents a novel multi-objective neural architecture search (MONAS) approach for designing neural networks optimized for in-memory computing (IMC) hardware. By simultaneously optimizing for power, latency, and accuracy, the authors are able to identify Pareto-optimal neural network architectures that can efficiently leverage the capabilities of IMC systems.

The key innovation is the use of multi-objective Bayesian optimization to efficiently explore the vast design space and identify high-performing models. The results demonstrate significant improvements in power and latency over standard neural networks, while maintaining comparable accuracy.

This work represents an important step towards the development of energy-efficient AI systems that can be deployed in a wide range of real-world applications, from edge devices to data centers. The MONAS technique could also be extended to consider other important objectives, such as carbon footprint, to further enhance the sustainability of these systems.

This summary was produced with help from an AI and may contain inaccuracies - check out the links to read the original source documents!

Related Papers

0

Multi-Objective Neural Architecture Search for In-Memory Computing

Md Hasibul Amin, Mohammadreza Mohammadi, Ramtin Zand

In this work, we employ neural architecture search (NAS) to enhance the efficiency of deploying diverse machine learning (ML) tasks on in-memory computing (IMC) architectures. Initially, we design three fundamental components inspired by the convolutional layers found in VGG and ResNet models. Subsequently, we utilize Bayesian optimization to construct a convolutional neural network (CNN) model with adaptable depths, employing these components. Through the Bayesian search algorithm, we explore a vast search space comprising over 640 million network configurations to identify the optimal solution, considering various multi-objective cost functions like accuracy/latency and accuracy/energy. Our evaluation of this NAS approach for IMC architecture deployment spans three distinct image classification datasets, demonstrating the effectiveness of our method in achieving a balanced solution characterized by high accuracy and reduced latency and energy consumption.

Read more6/12/2024

0

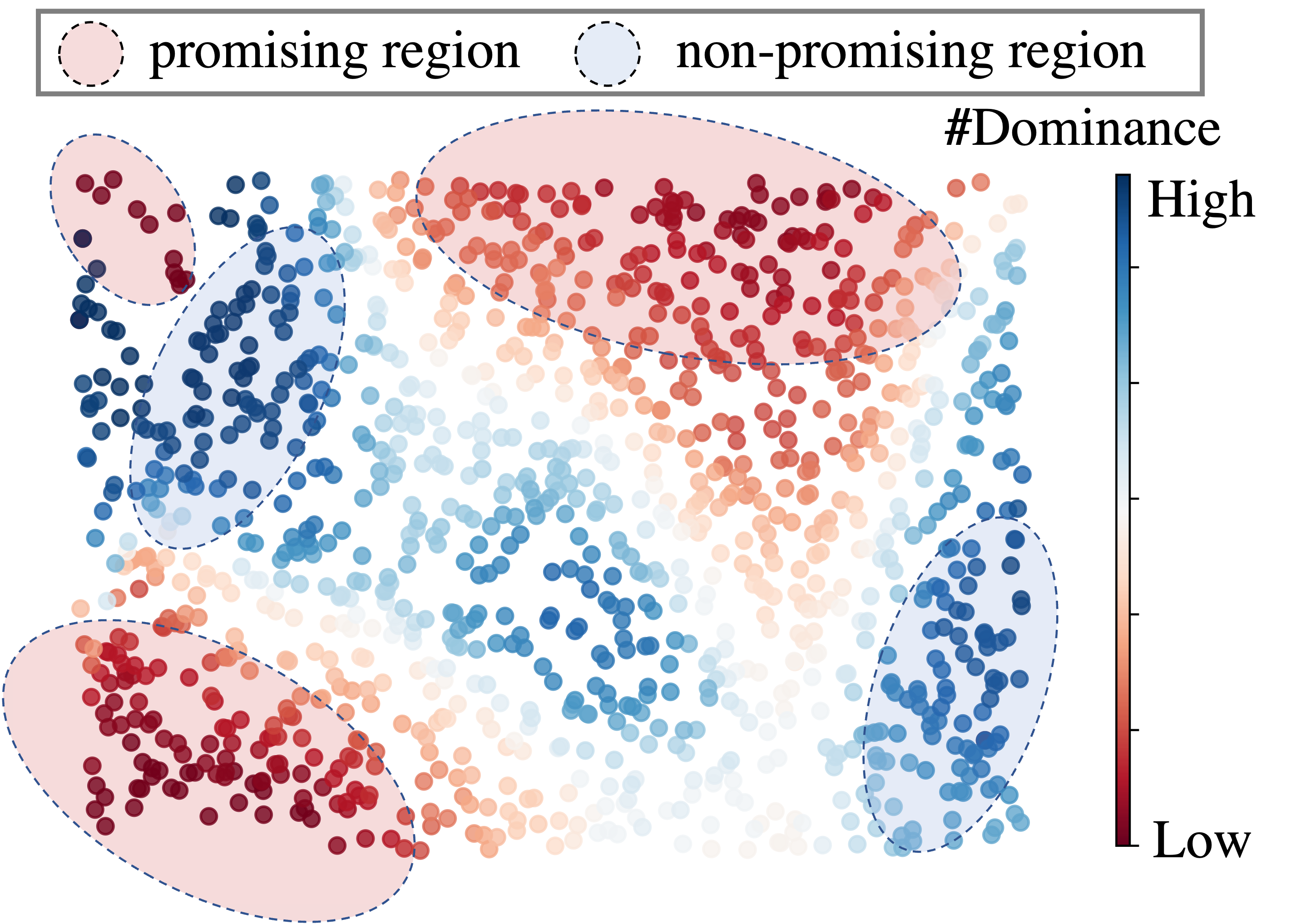

Multi-objective Neural Architecture Search by Learning Search Space Partitions

Yiyang Zhao, Linnan Wang, Tian Guo

Deploying deep learning models requires taking into consideration neural network metrics such as model size, inference latency, and #FLOPs, aside from inference accuracy. This results in deep learning model designers leveraging multi-objective optimization to design effective deep neural networks in multiple criteria. However, applying multi-objective optimizations to neural architecture search (NAS) is nontrivial because NAS tasks usually have a huge search space, along with a non-negligible searching cost. This requires effective multi-objective search algorithms to alleviate the GPU costs. In this work, we implement a novel multi-objectives optimizer based on a recently proposed meta-algorithm called LaMOO on NAS tasks. In a nutshell, LaMOO speedups the search process by learning a model from observed samples to partition the search space and then focusing on promising regions likely to contain a subset of the Pareto frontier. Using LaMOO, we observe an improvement of more than 200% sample efficiency compared to Bayesian optimization and evolutionary-based multi-objective optimizers on different NAS datasets. For example, when combined with LaMOO, qEHVI achieves a 225% improvement in sample efficiency compared to using qEHVI alone in NasBench201. For real-world tasks, LaMOO achieves 97.36% accuracy with only 1.62M #Params on CIFAR10 in only 600 search samples. On ImageNet, our large model reaches 80.4% top-1 accuracy with only 522M #FLOPs.

Read more7/19/2024

0

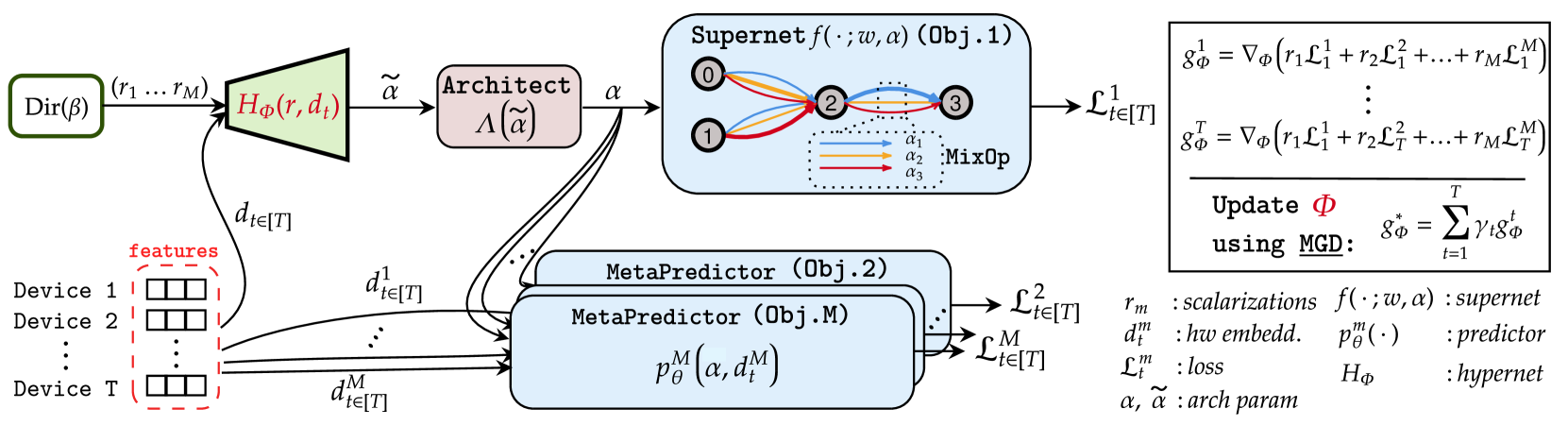

Multi-objective Differentiable Neural Architecture Search

Rhea Sanjay Sukthanker, Arber Zela, Benedikt Staffler, Samuel Dooley, Josif Grabocka, Frank Hutter

Pareto front profiling in multi-objective optimization (MOO), i.e. finding a diverse set of Pareto optimal solutions, is challenging, especially with expensive objectives like neural network training. Typically, in MOO neural architecture search (NAS), we aim to balance performance and hardware metrics across devices. Prior NAS approaches simplify this task by incorporating hardware constraints into the objective function, but profiling the Pareto front necessitates a computationally expensive search for each constraint. In this work, we propose a novel NAS algorithm that encodes user preferences for the trade-off between performance and hardware metrics, and yields representative and diverse architectures across multiple devices in just one search run. To this end, we parameterize the joint architectural distribution across devices and multiple objectives via a hypernetwork that can be conditioned on hardware features and preference vectors, enabling zero-shot transferability to new devices. Extensive experiments with up to 19 hardware devices and 3 objectives showcase the effectiveness and scalability of our method. Finally, we show that, without extra costs, our method outperforms existing MOO NAS methods across a broad range of qualitatively different search spaces and datasets, including MobileNetV3 on ImageNet-1k, an encoder-decoder transformer space for machine translation and a decoder-only transformer space for language modelling.

Read more6/21/2024

0

Multi-Objective Hardware Aware Neural Architecture Search using Hardware Cost Diversity

Nilotpal Sinha, Peyman Rostami, Abd El Rahman Shabayek, Anis Kacem, Djamila Aouada

Hardware-aware Neural Architecture Search approaches (HW-NAS) automate the design of deep learning architectures, tailored specifically to a given target hardware platform. Yet, these techniques demand substantial computational resources, primarily due to the expensive process of assessing the performance of identified architectures. To alleviate this problem, a recent direction in the literature has employed representation similarity metric for efficiently evaluating architecture performance. Nonetheless, since it is inherently a single objective method, it requires multiple runs to identify the optimal architecture set satisfying the diverse hardware cost constraints, thereby increasing the search cost. Furthermore, simply converting the single objective into a multi-objective approach results in an under-explored architectural search space. In this study, we propose a Multi-Objective method to address the HW-NAS problem, called MO-HDNAS, to identify the trade-off set of architectures in a single run with low computational cost. This is achieved by optimizing three objectives: maximizing the representation similarity metric, minimizing hardware cost, and maximizing the hardware cost diversity. The third objective, i.e. hardware cost diversity, is used to facilitate a better exploration of the architecture search space. Experimental results demonstrate the effectiveness of our proposed method in efficiently addressing the HW-NAS problem across six edge devices for the image classification task.

Read more4/22/2024