A Pipelined Memristive Neural Network Analog-to-Digital Converter

0

🧠

Sign in to get full access

Overview

- The paper discusses the growing demand for accurate, fast, and energy-efficient analog-to-digital (ADCs) and digital-to-analog converters (DACs) in high-speed, high-precision, and low-power mixed-signal systems.

- It proposes a scalable and modular neural network ADC architecture based on a pipeline of four-bit converters, which aims to address the speed-power-accuracy trade-off faced by modern ADCs.

- The proposed architecture preserves the inherent advantages of the four-bit converters, such as application reconfiguration, mismatch self-calibration, noise tolerance, and power optimization, while achieving higher resolution and throughput.

Plain English Explanation

As technology advances, there is an increasing need for analog-to-digital converters (ADCs) and digital-to-analog converters (DACs) that can operate at high speeds, with high precision, and with low power consumption. Unfortunately, as CMOS technology is miniaturized, modern ADCs often have to sacrifice one of these factors to achieve the others.

The researchers in this paper propose a new type of ADC architecture that uses a neural network approach. This architecture is based on a series of smaller, four-bit ADCs that can be trained in real-time using machine learning algorithms. By using this modular approach, the researchers believe they can preserve the benefits of the four-bit ADCs, such as the ability to reconfigure for different applications, automatically calibrate to account for manufacturing variations, and optimize for low power consumption.

At the same time, this modular approach allows the architecture to scale up to higher resolutions and faster data throughput, although with a trade-off in increased latency. The researchers' simulations show that an 8-bit version of this pipelined ADC architecture can achieve excellent performance metrics, including low error rates and high energy efficiency.

This research represents an important step towards developing large-scale neuromorphic data converters that can overcome the limitations of traditional ADC and DAC designs.

Technical Explanation

The paper proposes a scalable and modular neural network ADC architecture that is based on a pipeline of four-bit converters. This approach aims to preserve the inherent advantages of the four-bit converters, such as application reconfiguration, mismatch self-calibration, noise tolerance, and power optimization, while achieving higher resolution and throughput.

The researchers use SPICE simulations to evaluate an 8-bit version of the pipelined ADC architecture. The results show that this design achieves 0.18 LSB (Least Significant Bit) integral nonlinearity (INL), 0.20 LSB differential nonlinearity (DNL), 7.6 effective number of bits (ENOB), and an energy efficiency of 0.97 fJ/conversion (FOM).

This modular, neural network-based approach represents a significant step towards realizing large-scale neuromorphic data converters that can overcome the speed-power-accuracy trade-offs faced by traditional ADC and DAC designs. The researchers' use of a pipeline of four-bit converters allows for scalability, while preserving the advantages of the smaller converters, such as real-time reconfiguration and self-calibration.

Critical Analysis

The paper presents a promising approach to developing high-performance ADCs and DACs, but it also raises some potential concerns and areas for further research.

One limitation of the proposed architecture is that scaling it beyond 8 bits may still be challenging, as the researchers acknowledge. The complexity and power consumption of the neural network components could become prohibitive at higher resolutions.

Additionally, the paper does not provide a detailed comparison of the performance and energy efficiency of the proposed architecture against state-of-the-art ADC and DAC designs. It would be helpful to understand how this approach fares against alternative solutions, both in terms of technical metrics and real-world applications.

Further research could also explore the impact of the increased latency introduced by the pipelined architecture, as well as the potential for hybrid analog-digital memory computing approaches to improve the overall efficiency and performance.

Conclusion

This paper presents a novel, scalable, and modular neural network-based ADC architecture that aims to overcome the speed-power-accuracy trade-offs faced by traditional data converters. By leveraging a pipeline of four-bit converters, the proposed design preserves the inherent advantages of the smaller converters, such as reconfigurability, self-calibration, and power optimization, while achieving higher resolution and throughput.

The simulations demonstrate promising performance metrics for an 8-bit version of the pipelined ADC, suggesting that this research represents a significant step towards the realization of large-scale neuromorphic data converters that can meet the growing demand for accurate, fast, and energy-efficient analog-to-digital and digital-to-analog conversion.

This summary was produced with help from an AI and may contain inaccuracies - check out the links to read the original source documents!

Related Papers

🧠

0

A Pipelined Memristive Neural Network Analog-to-Digital Converter

Loai Danial, Kanishka Sharma, Shahar Kvatinsky

With the advent of high-speed, high-precision, and low-power mixed-signal systems, there is an ever-growing demand for accurate, fast, and energy-efficient analog-to-digital (ADCs) and digital-to-analog converters (DACs). Unfortunately, with the downscaling of CMOS technology, modern ADCs trade off speed, power and accuracy. Recently, memristive neuromorphic architectures of four-bit ADC/DAC have been proposed. Such converters can be trained in real-time using machine learning algorithms, to break through the speedpower-accuracy trade-off while optimizing the conversion performance for different applications. However, scaling such architectures above four bits is challenging. This paper proposes a scalable and modular neural network ADC architecture based on a pipeline of four-bit converters, preserving their inherent advantages in application reconfiguration, mismatch selfcalibration, noise tolerance, and power optimization, while approaching higher resolution and throughput in penalty of latency. SPICE evaluation shows that an 8-bit pipelined ADC achieves 0.18 LSB INL, 0.20 LSB DNL, 7.6 ENOB, and 0.97 fJ/conv FOM. This work presents a significant step towards the realization of large-scale neuromorphic data converters.

Read more6/5/2024

0

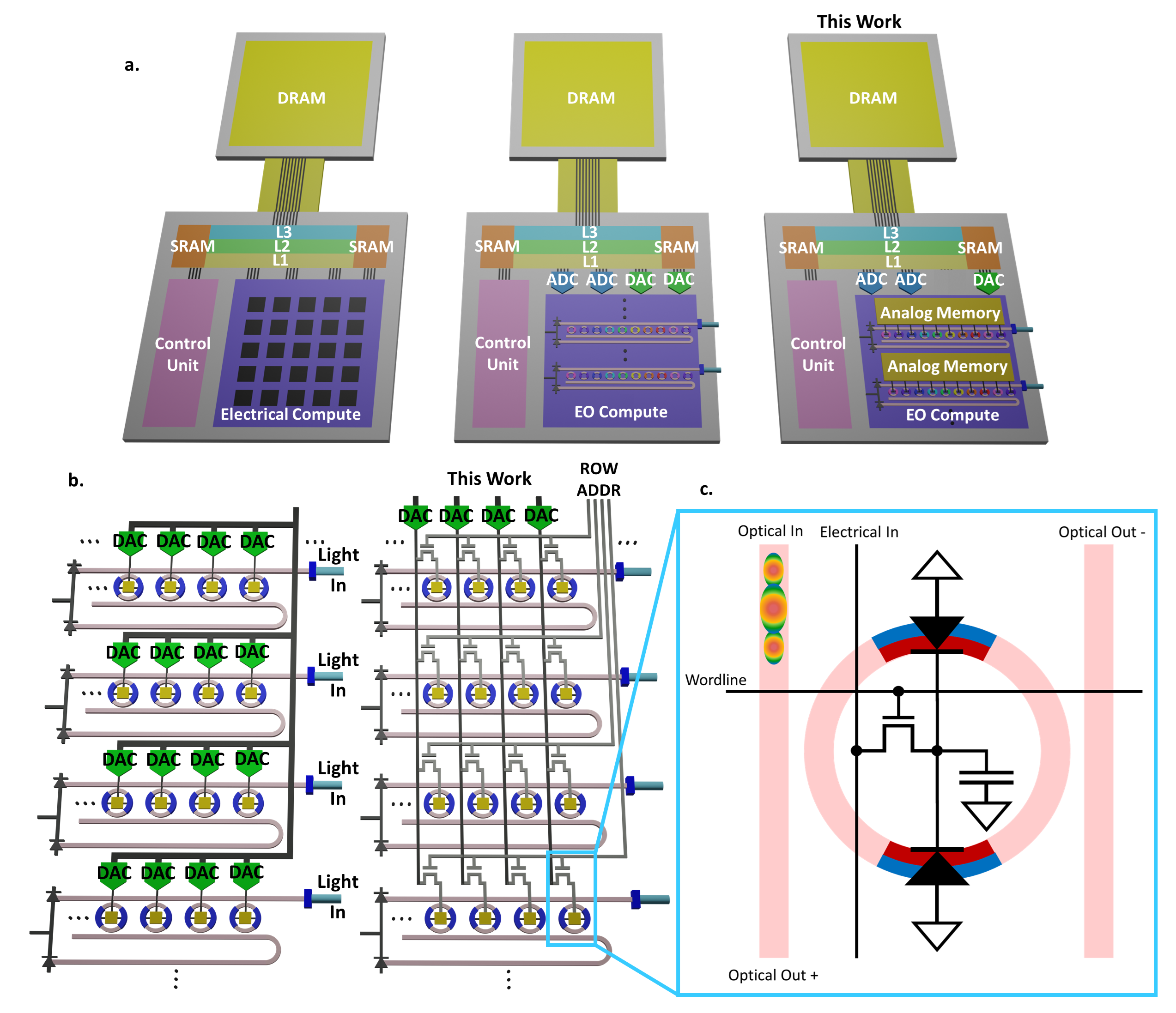

Dynamic Electro-Optic Analog Memory for Neuromorphic Photonic Computing

Sean Lam, Ahmed Khaled, Simon Bilodeau, Bicky A. Marquez, Paul R. Prucnal, Lukas Chrostowski, Bhavin J. Shastri, Sudip Shekhar

Artificial intelligence (AI) has seen remarkable advancements across various domains, including natural language processing, computer vision, autonomous vehicles, and biology. However, the rapid expansion of AI technologies has escalated the demand for more powerful computing resources. As digital computing approaches fundamental limits, neuromorphic photonics emerges as a promising platform to complement existing digital systems. In neuromorphic photonic computing, photonic devices are controlled using analog signals. This necessitates the use of digital-to-analog converters (DAC) and analog-to-digital converters (ADC) for interfacing with these devices during inference and training. However, data movement between memory and these converters in conventional von Neumann computing architectures consumes energy. To address this, analog memory co-located with photonic computing devices is proposed. This approach aims to reduce the reliance on DACs and ADCs and minimize data movement to enhance compute efficiency. This paper demonstrates a monolithically integrated neuromorphic photonic circuit with co-located capacitive analog memory and compares various analog memory technologies for neuromorphic photonic computing using the MNIST dataset as a benchmark.

Read more9/12/2024

0

Analog Spiking Neuron in CMOS 28 nm Towards Large-Scale Neuromorphic Processors

Marwan Besrour, Jacob Lavoie, Takwa Omrani, Gabriel Martin-Hardy, Esmaeil Ranjbar Koleibi, Jeremy Menard, Konin Koua, Philippe Marcoux, Mounir Boukadoum, Rejean Fontaine

The computational complexity of deep learning algorithms has given rise to significant speed and memory challenges for the execution hardware. In energy-limited portable devices, highly efficient processing platforms are indispensable for reproducing the prowess afforded by much bulkier processing platforms. In this work, we present a low-power Leaky Integrate-and-Fire (LIF) neuron design fabricated in TSMC's 28 nm CMOS technology as proof of concept to build an energy-efficient mixed-signal Neuromorphic System-on-Chip (NeuroSoC). The fabricated neuron consumes 1.61 fJ/spike and occupies an active area of 34 $mu m^{2}$, leading to a maximum spiking frequency of 300 kHz at 250 mV power supply. These performances are used in a software model to emulate the dynamics of a Spiking Neural Network (SNN). Employing supervised backpropagation and a surrogate gradient technique, the resulting accuracy on the MNIST dataset, using 4-bit post-training quantization stands at 82.5%. The approach underscores the potential of such ASIC implementation of quantized SNNs to deliver high-performance, energy-efficient solutions to various embedded machine-learning applications.

Read more8/16/2024

🤿

0

Approximate ADCs for In-Memory Computing

Arkapravo Ghosh, Hemkar Reddy Sadana, Mukut Debnath, Panthadip Maji, Shubham Negi, Sumeet Gupta, Mrigank Sharad, Kaushik Roy

In memory computing (IMC) architectures for deep learning (DL) accelerators leverage energy-efficient and highly parallel matrix vector multiplication (MVM) operations, implemented directly in memory arrays. Such IMC designs have been explored based on CMOS as well as emerging non-volatile memory (NVM) technologies like RRAM. IMC architectures generally involve a large number of cores consisting of memory arrays, storing the trained weights of the DL model. Peripheral units like DACs and ADCs are also used for applying inputs and reading out the output values. Recently reported designs reveal that the ADCs required for reading out the MVM results, consume more than 85% of the total compute power and also dominate the area, thereby eschewing the benefits of the IMC scheme. Mitigation of imperfections in the ADCs, namely, non-linearity and variations, incur significant design overheads, due to dedicated calibration units. In this work we present peripheral aware design of IMC cores, to mitigate such overheads. It involves incorporating the non-idealities of ADCs in the training of the DL models, along with that of the memory units. The proposed approach applies equally well to both current mode as well as charge mode MVM operations demonstrated in recent years., and can significantly simplify the design of mixed-signal IMC units.

Read more8/14/2024