A Realistic Simulation Framework for Analog/Digital Neuromorphic Architectures

0

Sign in to get full access

Overview

- This paper proposes a realistic simulation framework for analog/digital neuromorphic architectures.

- The framework aims to accurately model the behavior of analog and digital components in neuromorphic systems.

- The researchers developed the framework to enable efficient testing and validation of neuromorphic hardware and software.

Plain English Explanation

The paper describes a new simulation framework for neuromorphic computing systems. Neuromorphic systems are a type of hardware and software inspired by the human brain, designed to perform efficient and powerful computations.

The key idea behind this framework is to create a realistic simulation environment that can accurately capture the behavior of both analog and digital components in neuromorphic architectures. Analog components are circuits that work with continuously varying signals, while digital components process information using discrete values.

By developing this integrated simulation toolbox, the researchers aim to make it easier for researchers and engineers to test and validate their neuromorphic hardware and software designs before building the actual systems. This can save time and resources, and help identify potential issues early in the development process.

The framework uses advanced modeling techniques to simulate the complex dynamics of neuromorphic circuits, including the effects of noise, variability, and non-linearity. This allows it to provide a more accurate representation of how the system would behave in the real world, compared to simpler, more idealized models.

Overall, this simulation framework is an important step forward in the development of efficient and robust neuromorphic computing systems, which have the potential to revolutionize a wide range of applications, from edge AI to cognitive robotics.

Technical Explanation

The paper presents a comprehensive simulation framework for analog/digital neuromorphic architectures. The framework is designed to accurately model the behavior of both analog and digital components, enabling efficient testing and validation of neuromorphic hardware and software.

The key elements of the proposed framework include:

-

Analog Circuit Modeling: The framework uses advanced circuit modeling techniques, such as Verilog-A and SPICE, to simulate the complex dynamics of analog neuromorphic components, including the effects of noise, variability, and non-linearity.

-

Digital Neuron and Synapse Modeling: The framework also includes detailed models for digital neuromorphic components, such as spiking neurons and synapses, which are crucial for implementing neuromorphic algorithms and applications.

-

Multi-scale Simulation: The framework supports multi-scale simulation, allowing users to simulate the behavior of individual components, as well as the overall system-level performance, within a unified environment.

-

Hardware Acceleration: The framework leverages GPU acceleration to speed up the simulation process, enabling efficient exploration of large-scale neuromorphic architectures.

-

Flexibility and Extensibility: The framework is designed to be flexible and extensible, allowing users to integrate custom models, components, and simulations to suit their specific needs.

The researchers demonstrate the capabilities of the framework through a series of case studies, showcasing its ability to accurately simulate the behavior of both analog and digital neuromorphic systems, and its potential for accelerating the development and validation of neuromorphic hardware and software.

Critical Analysis

The proposed simulation framework represents a significant advancement in the field of neuromorphic computing, as it addresses a key challenge in the development of these systems: the need for a comprehensive and accurate simulation environment.

One of the key strengths of the framework is its ability to model the complex dynamics of analog neuromorphic components, which are critical for achieving high-performance and energy-efficient computations. By accurately capturing the effects of noise, variability, and non-linearity, the framework can provide a more realistic representation of how these systems would behave in the real world.

However, the paper also acknowledges some limitations of the framework, such as the need for further optimization and integration with higher-level neuromorphic design tools. Additionally, the researchers note that the framework may not be suitable for simulating extremely large-scale neuromorphic systems due to the computational resources required.

Further research and development in this area could focus on improving the scalability and usability of the framework, as well as exploring ways to seamlessly integrate it with other neuromorphic design and development tools. Additionally, it would be interesting to see how the framework could be extended to model the interactions between neuromorphic hardware and the physical world, such as in robotic or sensory applications.

Conclusion

The simulation framework proposed in this paper represents an important step forward in the development of analog/digital neuromorphic architectures. By providing a comprehensive and accurate simulation environment, the framework can help researchers and engineers to more efficiently design, test, and validate their neuromorphic hardware and software, ultimately accelerating the adoption and deployment of these powerful and efficient computing systems.

The framework's ability to accurately model the complex dynamics of both analog and digital neuromorphic components, along with its GPU-accelerated performance, makes it a valuable tool for driving the advancement of neuromorphic computing and enabling a wide range of applications, from edge AI to cognitive robotics.

This summary was produced with help from an AI and may contain inaccuracies - check out the links to read the original source documents!

Related Papers

0

A Realistic Simulation Framework for Analog/Digital Neuromorphic Architectures

Fernando M. Quintana, Maryada, Pedro L. Galindo, Elisa Donati, Giacomo Indiveri, Fernando Perez-Pe~na

Developing dedicated neuromorphic computing platforms optimized for embedded or edge-computing applications requires time-consuming design, fabrication, and deployment of full-custom neuromorphic processors.bTo ensure that initial prototyping efforts, exploring the properties of different network architectures and parameter settings, lead to realistic results it is important to use simulation frameworks that match as best as possible the properties of the final hardware. This is particularly challenging for neuromorphic hardware platforms made using mixed-signal analog/digital circuits, due to the variability and noise sensitivity of their components. In this paper, we address this challenge by developing a software spiking neural network simulator explicitly designed to account for the properties of mixed-signal neuromorphic circuits, including device mismatch variability. The simulator, called ARCANA (A Realistic Simulation Framework for Analog/Digital Neuromorphic Architectures), is designed to reproduce the dynamics of mixed-signal synapse and neuron electronic circuits with autogradient differentiation for parameter optimization and GPU acceleration. We demonstrate the effectiveness of this approach by matching software simulation results with measurements made from an existing neuromorphic processor. We show how the results obtained provide a reliable estimate of the behavior of the spiking neural network trained in software, once deployed in hardware. This framework enables the development and innovation of new learning rules and processing architectures in neuromorphic embedded systems.

Read more9/24/2024

🐍

0

GPU-RANC: A CUDA Accelerated Simulation Framework for Neuromorphic Architectures

Sahil Hassan, Michael Inouye, Miguel C. Gonzalez, Ilkin Aliyev, Joshua Mack, Maisha Hafiz, Ali Akoglu

Open-source simulation tools play a crucial role for neuromorphic application engineers and hardware architects to investigate performance bottlenecks and explore design optimizations before committing to silicon. Reconfigurable Architecture for Neuromorphic Computing (RANC) is one such tool that offers ability to execute pre-trained Spiking Neural Network (SNN) models within a unified ecosystem through both software-based simulation and FPGA-based emulation. RANC has been utilized by the community with its flexible and highly parameterized design to study implementation bottlenecks, tune architectural parameters or modify neuron behavior based on application insights and study the trade space on hardware performance and network accuracy. In designing architectures for use in neuromorphic computing, there are an incredibly large number of configuration parameters such as number and precision of weights per neuron, neuron and axon counts per core, network topology, and neuron behavior. To accelerate such studies and provide users with a streamlined productive design space exploration, in this paper we introduce the GPU-based implementation of RANC. We summarize our parallelization approach and quantify the speedup gains achieved with GPU-based tick-accurate simulations across various use cases. We demonstrate up to 780 times speedup compared to serial version of the RANC simulator based on a 512 neuromorphic core MNIST inference application. We believe that the RANC ecosystem now provides a much more feasible avenue in the research of exploring different optimizations for accelerating SNNs and performing richer studies by enabling rapid convergence to optimized neuromorphic architectures.

Read more4/26/2024

0

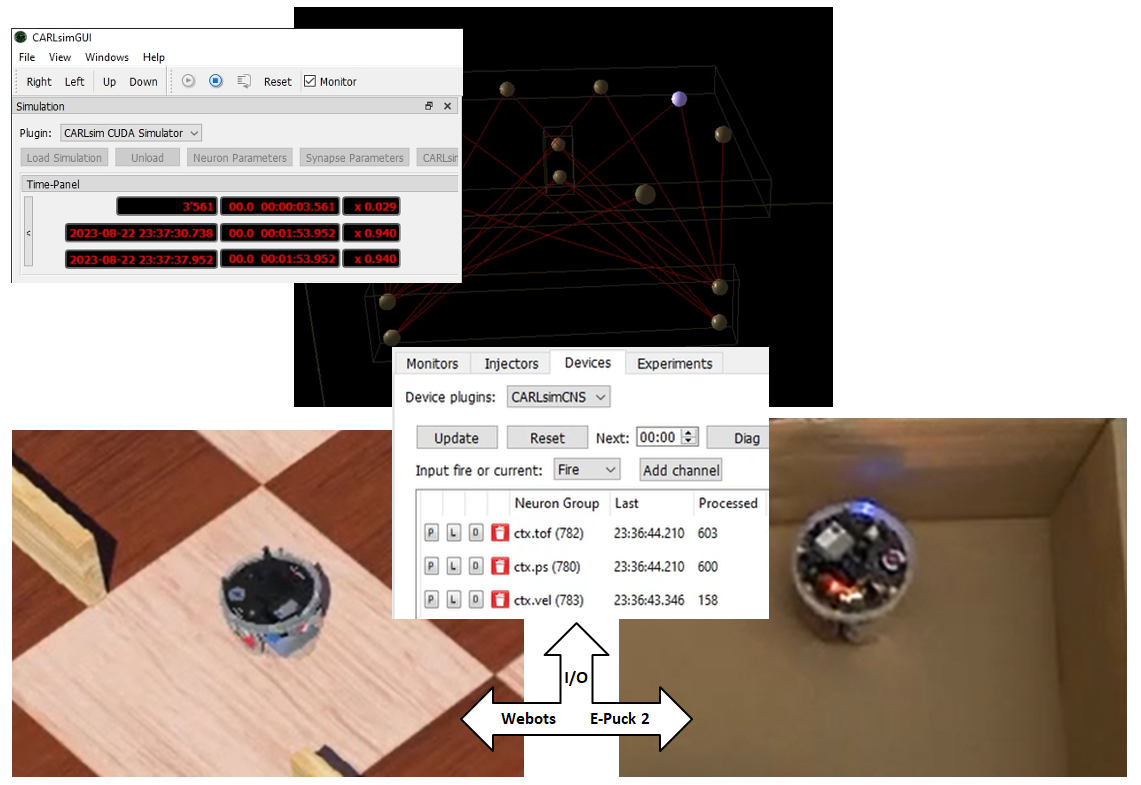

An Integrated Toolbox for Creating Neuromorphic Edge Applications

Lars Niedermeier (Niedermeier Consulting, Zurich, ZH, Switzerland), Jeffrey L. Krichmar (Department of Cognitive Sciences, Department of Computer Science, University of California, Irvine, CA, USA)

Spiking Neural Networks (SNNs) and neuromorphic models are more efficient and have more biological realism than the activation functions typically used in deep neural networks, transformer models and generative AI. SNNs have local learning rules, are able to learn on small data sets, and can adapt through neuromodulation. Although research has shown their advantages, there are still few compelling practical applications, especially at the edge where sensors and actuators need to be processed in a timely fashion. One reason for this might be that SNNs are much more challenging to understand, build, and operate due to their intrinsic properties. For instance, the mathematical foundation involves differential equations rather than basic activation functions. To address these challenges, we have developed CARLsim++. It is an integrated toolbox that enables fast and easy creation of neuromorphic applications. It encapsulates the mathematical intrinsics and low-level C++ programming by providing a graphical user interface for users who do not have a background in software engineering but still want to create neuromorphic models. Developers can easily configure inputs and outputs to devices and robots. These can be accurately simulated before deploying on physical devices. CARLsim++ can lead to rapid development of neuromorphic applications for simulation or edge processing.

Read more4/16/2024

0

Fast Algorithms for Spiking Neural Network Simulation with FPGAs

Bjorn A. Lindqvist, Artur Podobas

Using OpenCL-based high-level synthesis, we create a number of spiking neural network (SNN) simulators for the Potjans-Diesmann cortical microcircuit for a high-end Field-Programmable Gate Array (FPGA). Our best simulators simulate the circuit 25% faster than real-time, require less than 21 nJ per synaptic event, and are bottle-necked by the device's on-chip memory. Speed-wise they compare favorably to the state-of-the-art GPU-based simulators and their energy usage is lower than any other published result. This result is the first for simulating the circuit on a single hardware accelerator. We also extensively analyze the techniques and algorithms we implement our simulators with, many of which can be realized on other types of hardware. Thus, this article is of interest to any researcher or practitioner interested in efficient SNN simulation, whether they target FPGAs or not.

Read more5/6/2024