Tascade: Hardware Support for Atomic-free, Asynchronous and Efficient Reduction Trees

2311.15810

0

0

Abstract

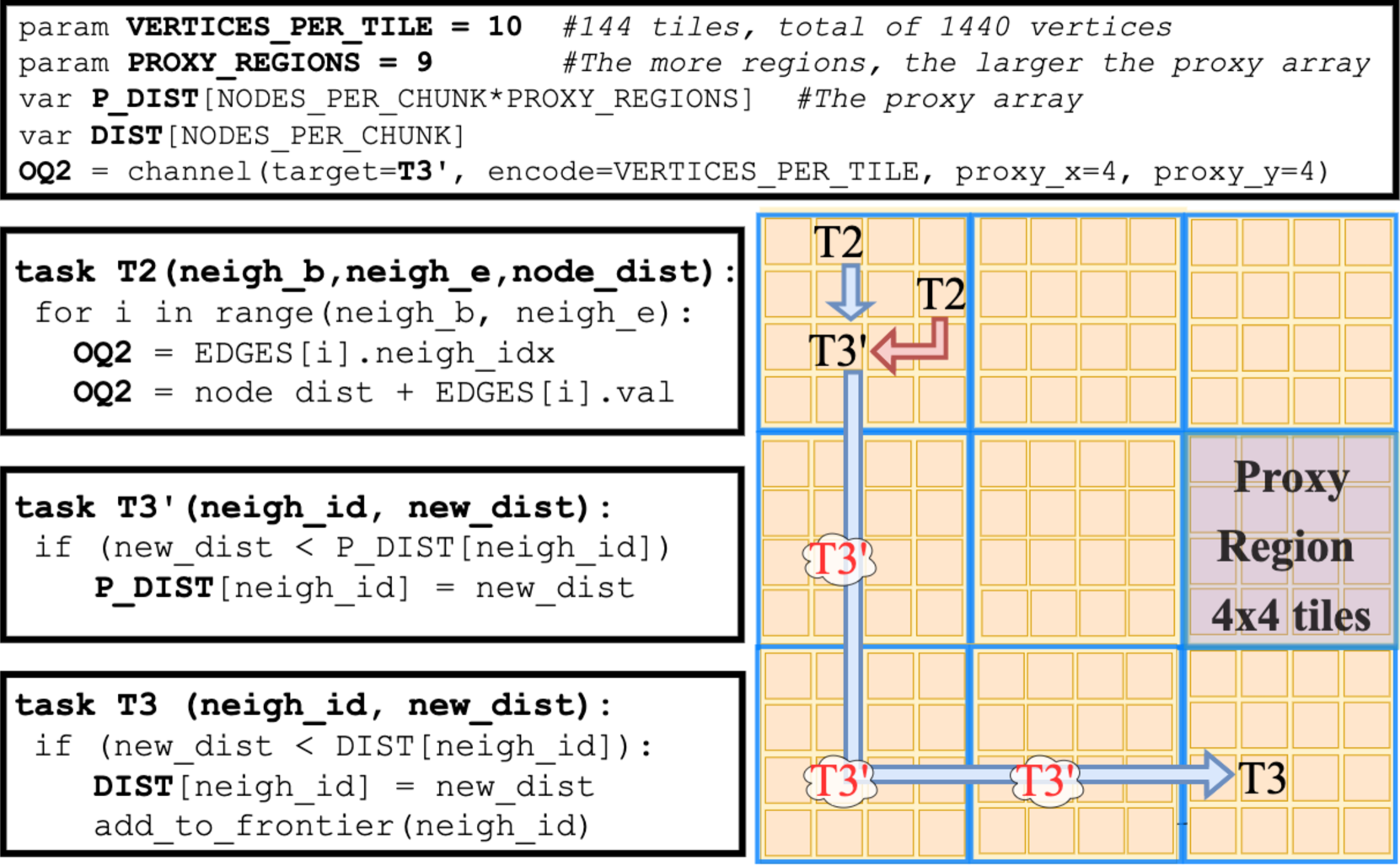

Graph search and sparse data-structure traversal workloads contain challenging irregular memory patterns on global data structures that need to be modified atomically. Distributed processing of these workloads has relied on server threads operating on their own data copies that are merged upon global synchronization. As parallelism increases within each server, the communication challenges that arose in distributed systems a decade ago are now being encountered within large manycore servers. Prior work has achieved scalability for sparse applications up to thousands of PUs on-chip, but does not scale further due to increasing communication distances and load-imbalance across PUs. To address these challenges we propose Tascade, a hardware-software co-design that offers support for storage-efficient data-private reductions as well as asynchronous and opportunistic reduction trees. Tascade introduces an execution model along with supporting hardware design that allows coalescing of data updates regionally and merges the data from these regions through cascaded updates. Together, Tascade innovations minimize communication and increase work balance in task-based parallelization schemes and scales up to a million PUs. We evaluate six applications and four datasets to provide a detailed analysis of Tascade's performance, power, and traffic-reduction gains over prior work. Our parallelization of Breadth-First-Search with RMAT-26 across a million PUs -- the largest of the literature -- reaches over 7600 GTEPS.

Get summaries of the top AI research delivered straight to your inbox:

Overview

- This paper introduces Tascade, a hardware-based approach to support efficient and asynchronous reduction trees without relying on complex atomic instructions.

- Reduction trees are commonly used in parallel computing to aggregate data, but they can be challenging to implement efficiently due to the need for synchronization and atomic operations.

- Tascade aims to address these challenges by providing specialized hardware support for reduction trees, enabling higher performance and scalability.

Plain English Explanation

Tascade is a new hardware-based system that helps computers work with reduction trees more efficiently. Reduction trees are a common way for computers to combine lots of small pieces of data into a single result. This is useful for many parallel computing tasks, like summing up values from many different processors.

However, implementing reduction trees can be tricky. Computers need to carefully coordinate the different parts of the tree to avoid conflicts and make sure the final result is correct. This often requires the use of complex atomic instructions, which can be slow and limit the scalability of the system.

Tascade: Hardware Support for Atomic-free, Asynchronous and Efficient Reduction Trees introduces a new hardware-based approach to address these challenges. By providing specialized support for reduction trees directly in the hardware, Tascade can enable faster and more scalable parallel computations without relying on slow atomic instructions.

The key insight behind Tascade is to offload the coordination of the reduction tree to dedicated hardware, rather than having the main processors handle it. This allows the processors to focus on their core computations while the hardware manages the reduction tree in the background. This can lead to significant performance improvements, especially for large-scale parallel applications.

Technical Explanation

Tascade: Hardware Support for Atomic-free, Asynchronous and Efficient Reduction Trees proposes a hardware-based approach to support efficient and asynchronous reduction trees without relying on complex atomic instructions.

Reduction trees are a common pattern in parallel computing, where data needs to be aggregated from many sources into a single result. However, implementing reduction trees efficiently can be challenging due to the need for synchronization and the use of expensive atomic operations.

To address these challenges, the authors of Tascade introduce a specialized hardware module that can manage the coordination of the reduction tree in the background. This offloads the complexity of the reduction tree from the main processors, allowing them to focus on their core computations.

The Tascade hardware module includes several key components:

- Reduction Network: A hardware-based implementation of the reduction tree, which can perform the aggregation of data asynchronously without the need for atomic instructions.

- Task Scheduler: A module that manages the scheduling and execution of reduction tasks, ensuring that data dependencies are respected and the reduction tree is updated efficiently.

- Consistency Manager: A component that maintains the consistency of the reduction tree, handling any potential conflicts or race conditions that may arise during the asynchronous execution.

The authors evaluate the performance of Tascade using a range of benchmarks and applications, and demonstrate significant improvements in execution time and scalability compared to traditional software-based approaches that rely on atomic instructions.

Critical Analysis

The Tascade: Hardware Support for Atomic-free, Asynchronous and Efficient Reduction Trees paper presents a promising approach to addressing the challenges of efficient reduction tree implementation in parallel computing. By offloading the complexity of the reduction tree to specialized hardware, the authors are able to achieve significant performance improvements without the need for complex atomic instructions.

One potential limitation of the Tascade approach is the additional hardware cost and complexity required to implement the dedicated reduction network and task scheduling components. The authors do not provide a detailed analysis of the area and power overhead of the Tascade hardware, which would be important for evaluating its practical feasibility and adoption in real-world systems.

Additionally, the paper focuses primarily on the performance benefits of Tascade, but does not explore the potential impact on programmability or the ease of use for developers. Integrating Tascade into existing parallel programming frameworks and ensuring that the hardware-based approach is transparent to the software layer could be an important area for further research.

Despite these potential limitations, the Tascade: Hardware Support for Atomic-free, Asynchronous and Efficient Reduction Trees paper represents a significant advancement in the field of parallel computing and data processing. The authors have demonstrated the potential of hardware-based approaches to solving challenging coordination and synchronization problems, and their work could inspire further research in this direction.

Conclusion

The Tascade: Hardware Support for Atomic-free, Asynchronous and Efficient Reduction Trees paper introduces a novel hardware-based approach to supporting efficient and asynchronous reduction trees in parallel computing. By offloading the complexity of the reduction tree to specialized hardware, Tascade can achieve significant performance improvements and improved scalability compared to traditional software-based approaches.

This work represents an important step forward in the ongoing effort to develop more scalable and efficient parallel computing systems, and could have broader implications for the design of future hardware architectures and programming models. As the computational demands of modern applications continue to grow, innovative solutions like Tascade will be increasingly important for unlocking the full potential of parallel processing.

This summary was produced with help from an AI and may contain inaccuracies - check out the links to read the original source documents!

Related Papers

🧠

Near-Optimal Wafer-Scale Reduce

Piotr Luczynski, Lukas Gianinazzi, Patrick Iff, Leighton Wilson, Daniele De Sensi, Torsten Hoefler

0

0

Efficient Reduce and AllReduce communication collectives are a critical cornerstone of high-performance computing (HPC) applications. We present the first systematic investigation of Reduce and AllReduce on the Cerebras Wafer-Scale Engine (WSE). This architecture has been shown to achieve unprecedented performance both for machine learning workloads and other computational problems like FFT. We introduce a performance model to estimate the execution time of algorithms on the WSE and validate our predictions experimentally for a wide range of input sizes. In addition to existing implementations, we design and implement several new algorithms specifically tailored to the architecture. Moreover, we establish a lower bound for the runtime of a Reduce operation on the WSE. Based on our model, we automatically generate code that achieves near-optimal performance across the whole range of input sizes. Experiments demonstrate that our new Reduce and AllReduce algorithms outperform the current vendor solution by up to 3.27x. Additionally, our model predicts performance with less than 4% error. The proposed communication collectives increase the range of HPC applications that can benefit from the high throughput of the WSE. Our model-driven methodology demonstrates a disciplined approach that can lead the way to further algorithmic advancements on wafer-scale architectures.

5/17/2024

Efficient Distributed Data Structures for Future Many-core Architectures

Panagiota Fatourou, Nikolaos D. Kallimanis, Eleni Kanellou, Odysseas Makridakis, Christi Symeonidou

0

0

We study general techniques for implementing distributed data structures on top of future many-core architectures with non cache-coherent or partially cache-coherent memory. With the goal of contributing towards what might become, in the future, the concurrency utilities package in Java collections for such architectures, we end up with a comprehensive collection of data structures by considering different variants of these techniques. To achieve scalability, we study a generic scheme which makes all our implementations hierarchical. We consider a collection of known techniques for improving the scalability of concurrent data structures and we adjust them to work in our setting. We have performed experiments which illustrate that some of these techniques have indeed high impact on achieving scalability. Our experiments also reveal the performance and scalability power of the hierarchical approach. We finally present experiments to study energy consumption aspects of the proposed techniques by using an energy model recently proposed for such architectures.

4/9/2024

🗣️

Concurrent aggregate queries

Gal Sela, Erez Petrank

0

0

Concurrent data structures serve as fundamental building blocks for concurrent computing. Many concurrent counterparts have been designed for basic sequential mechanisms; however, one notable omission is a concurrent tree that supports aggregate queries. Aggregate queries essentially compile succinct information about a range of data items, for example, calculating the average salary of employees in their 30s. Such queries play an essential role in various applications and are commonly taught in undergraduate data structures courses. In this paper, we formalize a type of aggregate queries that can be efficiently supported by concurrent trees and present a design for implementing these queries on concurrent trees. We bring two algorithms implementing this design, where one optimizes for tree update time, while the other optimizes for aggregate query time. We analyze their correctness and complexity, demonstrating the trade-offs between query time and update time.

5/14/2024

👀

Low-Depth Spatial Tree Algorithms

Yves Baumann, Tal Ben-Nun, Maciej Besta, Lukas Gianinazzi, Torsten Hoefler, Piotr Luczynski

0

0

Contemporary accelerator designs exhibit a high degree of spatial localization, wherein two-dimensional physical distance determines communication costs between processing elements. This situation presents considerable algorithmic challenges, particularly when managing sparse data, a pivotal component in progressing data science. The spatial computer model quantifies communication locality by weighting processor communication costs by distance, introducing a term named energy. Moreover, it integrates depth, a widely-utilized metric, to promote high parallelism. We propose and analyze a framework for efficient spatial tree algorithms within the spatial computer model. Our primary method constructs a spatial tree layout that optimizes the locality of the neighbors in the compute grid. This approach thereby enables locality-optimized messaging within the tree. Our layout achieves a polynomial factor improvement in energy compared to utilizing a PRAM approach. Using this layout, we develop energy-efficient treefix sum and lowest common ancestor algorithms, which are both fundamental building blocks for other graph algorithms. With high probability, our algorithms exhibit near-linear energy and poly-logarithmic depth. Our contributions augment a growing body of work demonstrating that computations can have both high spatial locality and low depth. Moreover, our work constitutes an advancement in the spatial layout of irregular and sparse computations.

5/8/2024