CHIME: Energy-Efficient STT-RAM-based Concurrent Hierarchical In-Memory Processing

0

Sign in to get full access

Overview

- Processing-in-cache (PiC) and Processing-in-memory (PiM) architectures for energy-efficient computing

- Concurrent hierarchical in-memory processing using spin-transfer torque RAM (STT-RAM)

- Domain-specific computing to accelerate performance for various applications

Plain English Explanation

CHIME: Energy-Efficient STT-RAM-based Concurrent Hierarchical In-Memory Processing explores a new approach to computing called concurrent hierarchical in-memory processing. This technique aims to improve the energy efficiency of computing systems by performing computations directly within the memory, rather than constantly moving data between memory and a separate processor.

The key idea is to use spin-transfer torque RAM (STT-RAM) technology to enable this in-memory processing. STT-RAM is a type of non-volatile memory that can retain information even when the power is turned off. By leveraging the properties of STT-RAM, the researchers were able to develop a system that can perform computations concurrently at multiple levels of a hierarchical memory architecture.

This approach has several potential benefits:

- Energy Efficiency: By eliminating the need to constantly shuttle data between memory and processor, the system can significantly reduce the energy consumed by the computing system.

- Performance Acceleration: The ability to perform computations directly within the memory can speed up certain types of workloads, such as those found in domain-specific applications.

- Scalability: The hierarchical nature of the memory architecture allows the system to scale and handle larger amounts of data and more complex computations.

Overall, this research demonstrates a promising direction for improving the efficiency and performance of computing systems, particularly for applications that can benefit from the unique properties of STT-RAM and in-memory processing.

Technical Explanation

CHIME: Energy-Efficient STT-RAM-based Concurrent Hierarchical In-Memory Processing presents a novel approach to computing called concurrent hierarchical in-memory processing (CHIME). The key idea is to leverage the properties of spin-transfer torque RAM (STT-RAM) to enable computations to be performed directly within the memory hierarchy, rather than constantly moving data between memory and a separate processor.

The researchers designed a hierarchical memory architecture that allows for concurrent processing at multiple levels. This includes a Processing-in-Cache (PiC) layer, which performs computations within the cache, and a Processing-in-Memory (PiM) layer, which performs computations within the main memory. By using STT-RAM technology, the system can perform these computations in a highly energy-efficient manner.

The researchers evaluated the performance and energy efficiency of CHIME using a range of domain-specific applications, including machine learning, graph analytics, and signal processing tasks. Their results demonstrate that CHIME can achieve significant performance improvements and energy savings compared to traditional computing architectures.

Critical Analysis

The research presented in CHIME: Energy-Efficient STT-RAM-based Concurrent Hierarchical In-Memory Processing is a promising step towards more energy-efficient and performance-oriented computing systems. The use of STT-RAM technology and the hierarchical memory architecture with concurrent processing capabilities are well-designed and show strong potential.

However, the paper does not address several potential limitations and areas for further research. For example, the impact of process variations and device-level non-uniformities on the reliability and scalability of the CHIME system is not discussed. Additionally, the paper does not explore the implications of the CHIME approach for distributed optimization algorithms or the potential challenges in integrating the CHIME system with existing computing infrastructure.

Further research is needed to address these concerns and explore the broader implications of this technology for the field of computing. Nonetheless, the CHIME approach represents a significant contribution to the ongoing efforts to develop more energy-efficient and high-performance computing systems.

Conclusion

CHIME: Energy-Efficient STT-RAM-based Concurrent Hierarchical In-Memory Processing presents a novel computing architecture that leverages the properties of spin-transfer torque RAM (STT-RAM) to enable concurrent hierarchical in-memory processing. This approach aims to improve the energy efficiency and performance of computing systems by performing computations directly within the memory hierarchy, rather than constantly moving data between memory and a separate processor.

The researchers demonstrated the potential of this approach through experiments with various domain-specific applications, showcasing significant performance improvements and energy savings. While further research is needed to address potential limitations and explore the broader implications of this technology, the CHIME approach represents an important step towards more efficient and capable computing systems.

This summary was produced with help from an AI and may contain inaccuracies - check out the links to read the original source documents!

Related Papers

0

CHIME: Energy-Efficient STT-RAM-based Concurrent Hierarchical In-Memory Processing

Dhruv Gajaria, Tosiron Adegbija, Kevin Gomez

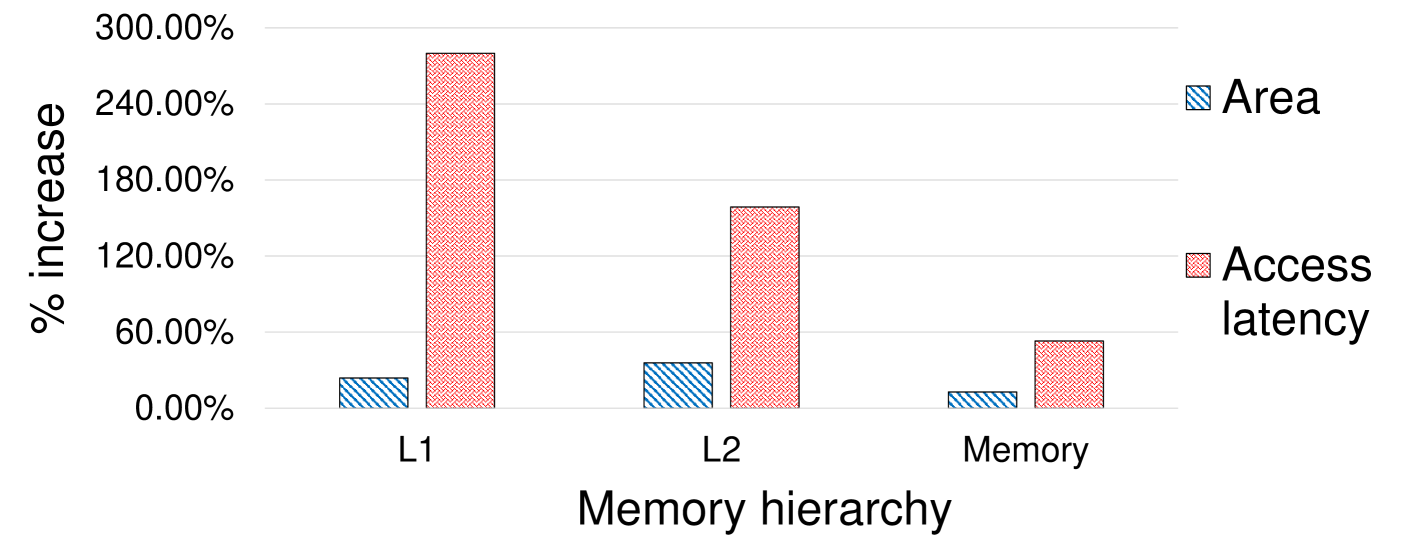

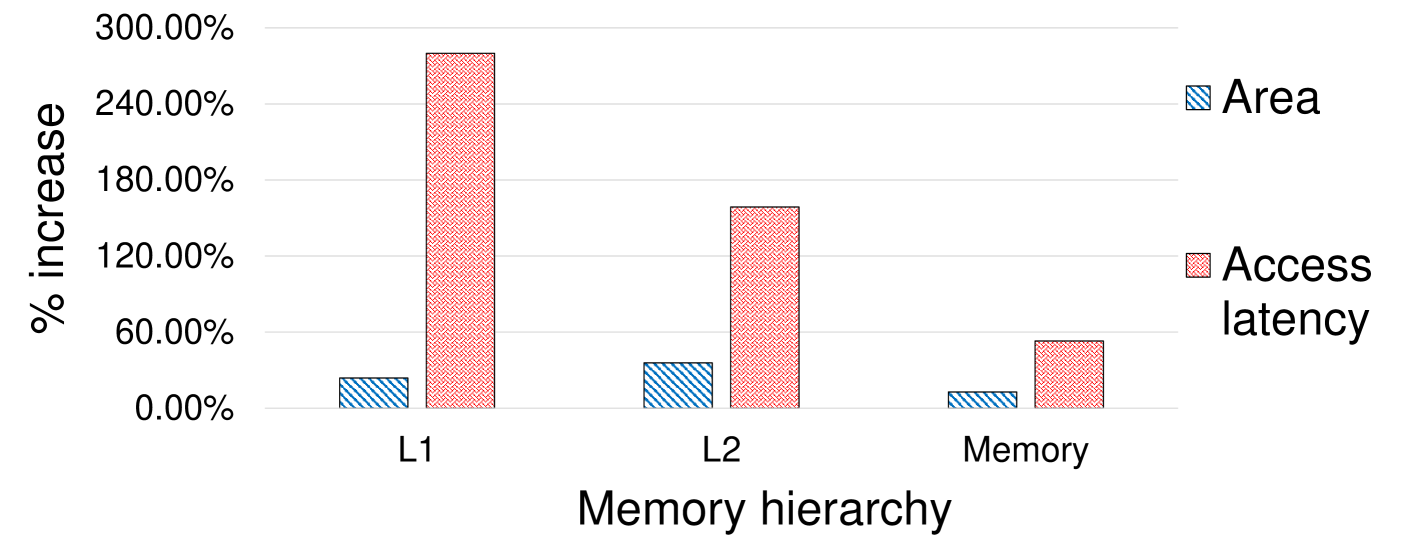

Processing-in-cache (PiC) and Processing-in-memory (PiM) architectures, especially those utilizing bit-line computing, offer promising solutions to mitigate data movement bottlenecks within the memory hierarchy. While previous studies have explored the integration of compute units within individual memory levels, the complexity and potential overheads associated with these designs have often limited their capabilities. This paper introduces a novel PiC/PiM architecture, Concurrent Hierarchical In-Memory Processing (CHIME), which strategically incorporates heterogeneous compute units across multiple levels of the memory hierarchy. This design targets the efficient execution of diverse, domain-specific workloads by placing computations closest to the data where it optimizes performance, energy consumption, data movement costs, and area. CHIME employs STT-RAM due to its various advantages in PiC/PiM computing, such as high density, low leakage, and better resiliency to data corruption from activating multiple word lines. We demonstrate that CHIME enhances concurrency and improves compute unit utilization at each level of the memory hierarchy. We present strategies for exploring the design space, grouping, and placing the compute units across the memory hierarchy. Experiments reveal that, compared to the state-of-the-art bit-line computing approaches, CHIME achieves significant speedup and energy savings of 57.95% and 78.23% for various domain-specific workloads, while reducing the overheads associated with single-level compute designs.

Read more7/30/2024

0

STT-RAM-based Hierarchical In-Memory Computing

Dhruv Gajaria, Kevin Antony Gomez, Tosiron Adegbija

In-memory computing promises to overcome the von Neumann bottleneck in computer systems by performing computations directly within the memory. Previous research has suggested using Spin-Transfer Torque RAM (STT-RAM) for in-memory computing due to its non-volatility, low leakage power, high density, endurance, and commercial viability. This paper explores hierarchical in-memory computing, where different levels of the memory hierarchy are augmented with processing elements to optimize workload execution. The paper investigates processing in memory (PiM) using non-volatile STT-RAM and processing in cache (PiC) using volatile STT-RAM with relaxed retention, which helps mitigate STT-RAM's write latency and energy overheads. We analyze tradeoffs and overheads associated with data movement for PiC versus write overheads for PiM using STT-RAMs for various workloads. We examine workload characteristics, such as computational intensity and CPU-dependent workloads with limited instruction-level parallelism, and their impact on PiC/PiM tradeoffs. Using these workloads, we evaluate computing in STT-RAM versus SRAM at different cache hierarchy levels and explore the potential of heterogeneous STT-RAM cache architectures with various retention times for PiC and CPU-based computing. Our experiments reveal significant advantages of STT-RAM-based PiC over PiM for specific workloads. Finally, we describe open research problems in hierarchical in-memory computing architectures to further enhance this paradigm.

Read more7/30/2024

0

A Collaborative PIM Computing Optimization Framework for Multi-Tenant DNN

Bojing Li, Duo Zhong, Xiang Chen, Chenchen Liu

Modern Artificial Intelligence (AI) applications are increasingly utilizing multi-tenant deep neural networks (DNNs), which lead to a significant rise in computing complexity and the need for computing parallelism. ReRAM-based processing-in-memory (PIM) computing, with its high density and low power consumption characteristics, holds promising potential for supporting the deployment of multi-tenant DNNs. However, direct deployment of complex multi-tenant DNNs on exsiting ReRAM-based PIM designs poses challenges. Resource contention among different tenants can result in sever under-utilization of on-chip computing resources. Moreover, area-intensive operators and computation-intensive operators require excessively large on-chip areas and long processing times, leading to high overall latency during parallel computing. To address these challenges, we propose a novel ReRAM-based in-memory computing framework that enables efficient deployment of multi-tenant DNNs on ReRAM-based PIM designs. Our approach tackles the resource contention problems by iteratively partitioning the PIM hardware at tenant level. In addition, we construct a fine-grained reconstructed processing pipeline at the operator level to handle area-intensive operators. Compared to the direct deployments on traditional ReRAM-based PIM designs, our proposed PIM computing framework achieves significant improvements in speed (ranges from 1.75x to 60.43x) and energy(up to 1.89x).

Read more8/12/2024

0

WWW: What, When, Where to Compute-in-Memory

Tanvi Sharma, Mustafa Ali, Indranil Chakraborty, Kaushik Roy

Compute-in-memory (CiM) has emerged as a highly energy efficient solution for performing matrix multiplication during Machine Learning (ML) inference. However, integrating compute in memory poses key questions, such as 1) What type of CiM to use: Given a multitude of CiM design characteristics, determining their suitability from architecture perspective is needed. 2) When to use CiM: ML inference includes workloads with a variety of memory and compute requirements, making it difficult to identify when CiM is more beneficial. 3) Where to integrate CiM: Each memory level has different bandwidth and capacity, creating different data reuse opportunities for CiM integration. To answer such questions regarding on-chip CiM integration for accelerating ML workloads, we use an analytical architecture evaluation methodology where we tailor the dataflow mapping. The mapping algorithm aims to achieve highest weight reuse and reduced data movements for a given CiM prototype and workload. Our experiments show that CiM integrated memory improves energy efficiency by up to 3.4x and throughput by up to 15.6x compared to tensor-core-like baseline architecture, with INT-8 precision under iso-area constraints. We believe the proposed work provides insights into what type of CiM to use, and when and where to optimally integrate it in the cache hierarchy for efficient matrix multiplication.

Read more6/21/2024