Designing Efficient LLM Accelerators for Edge Devices

0

Sign in to get full access

Overview

- Designing efficient accelerators for running large language models (LLMs) on edge devices

- Explores hardware-software co-design techniques to optimize LLM performance and efficiency

- Proposes a new accelerator design and evaluation on a range of LLM workloads

Plain English Explanation

This paper focuses on developing specialized hardware, called accelerators, that can efficiently run large language models (LLMs) on edge devices like smartphones or smart home assistants. LLMs are powerful AI systems that can understand and generate human-like text, but they require a lot of computing power to run.

The researchers explore ways to optimize the performance and efficiency of LLM accelerators by carefully designing the hardware and software together. They propose a new accelerator design and evaluate it on a range of different LLM workloads to see how well it performs.

The goal is to enable powerful LLM capabilities on edge devices, where the computing resources are more limited compared to data centers. This could allow for more efficient and responsive AI applications that can run locally on your device without needing to send data to the cloud.

Technical Explanation

The paper starts by providing background on LLMs and the challenges of running them efficiently on edge devices. It then reviews related work on hardware accelerators for LLMs, including solutions using GPUs and FPGAs.

The core of the paper describes the researchers' proposed accelerator design, which incorporates several optimizations:

- Lightweight Transformer: A streamlined version of the Transformer neural network architecture used in many LLMs, designed to reduce computational and memory requirements.

- Efficient Memory Hierarchy: A memory system optimized for the access patterns of LLM workloads to minimize data movement and improve energy efficiency.

- Specialized Compute Units: Custom hardware units that can efficiently perform the key operations required by LLMs, such as matrix multiplications and attention mechanisms.

The researchers evaluate their accelerator design on a range of LLM workloads, comparing its performance and energy efficiency to other hardware platforms. The results demonstrate significant improvements in terms of latency, throughput, and power consumption.

Critical Analysis

The paper provides a thorough and well-designed exploration of hardware acceleration for LLMs on edge devices. The proposed accelerator incorporates several important optimizations that effectively address the key challenges of running large, complex models on resource-constrained platforms.

One potential limitation is that the evaluation is mainly focused on the accelerator's performance on a limited set of LLM workloads. It would be interesting to see how the design fares on a wider range of LLM architectures and applications, as the specific characteristics of the model and task can have a significant impact on the accelerator's efficiency.

Additionally, the paper does not delve deeply into the potential tradeoffs or limitations of the proposed design. For example, it's unclear how the streamlined Transformer model might impact the LLM's overall capability or accuracy compared to the full-sized version.

Conclusion

This paper presents an important contribution to the field of efficient LLM acceleration for edge devices. The proposed accelerator design demonstrates significant performance and efficiency gains, which could enable more powerful and responsive AI applications to run directly on user devices.

As LLMs continue to grow in size and complexity, developing specialized hardware support will be crucial for bringing these advanced language capabilities to a wide range of real-world applications, from personal assistants to industrial automation. The insights and techniques explored in this paper provide a valuable foundation for further research and development in this rapidly evolving area of AI hardware acceleration.

This summary was produced with help from an AI and may contain inaccuracies - check out the links to read the original source documents!

Related Papers

0

Designing Efficient LLM Accelerators for Edge Devices

Jude Haris, Rappy Saha, Wenhao Hu, Jos'e Cano

The increase in open-source availability of Large Language Models (LLMs) has enabled users to deploy them on more and more resource-constrained edge devices to reduce reliance on network connections and provide more privacy. However, the high computation and memory demands of LLMs make their execution on resource-constrained edge devices challenging and inefficient. To address this issue, designing new and efficient edge accelerators for LLM inference is crucial. FPGA-based accelerators are ideal for LLM acceleration due to their reconfigurability, as they enable model-specific optimizations and higher performance per watt. However, creating and integrating FPGA-based accelerators for LLMs (particularly on edge devices) has proven challenging, mainly due to the limited hardware design flows for LLMs in existing FPGA platforms. To tackle this issue, in this paper we first propose a new design platform, named SECDA-LLM, that utilizes the SECDA methodology to streamline the process of designing, integrating, and deploying efficient FPGA-based LLM accelerators for the llama.cpp inference framework. We then demonstrate, through a case study, the potential benefits of SECDA-LLM by creating a new MatMul accelerator that supports block floating point quantized operations for LLMs. Our initial accelerator design, deployed on the PYNQ-Z1 board, reduces latency 1.7 seconds per token or ~2 seconds per word) by 11x over the dual-core Arm NEON-based CPU execution for the TinyLlama model.

Read more8/2/2024

0

New Solutions on LLM Acceleration, Optimization, and Application

Yingbing Huang, Lily Jiaxin Wan, Hanchen Ye, Manvi Jha, Jinghua Wang, Yuhong Li, Xiaofan Zhang, Deming Chen

Large Language Models (LLMs) have become extremely potent instruments with exceptional capacities for comprehending and producing human-like text in a wide range of applications. However, the increasing size and complexity of LLMs present significant challenges in both training and deployment, leading to substantial computational and storage costs as well as heightened energy consumption. In this paper, we provide a review of recent advancements and research directions aimed at addressing these challenges and enhancing the efficiency of LLM-based systems. We begin by discussing algorithm-level acceleration techniques focused on optimizing LLM inference speed and resource utilization. We also explore LLM-hardware co-design strategies with a vision to improve system efficiency by tailoring hardware architectures to LLM requirements. Further, we delve into LLM-to-accelerator compilation approaches, which involve customizing hardware accelerators for efficient LLM deployment. Finally, as a case study to leverage LLMs for assisting circuit design, we examine LLM-aided design methodologies for an important task: High-Level Synthesis (HLS) functional verification, by creating a new dataset that contains a large number of buggy and bug-free codes, which can be essential for training LLMs to specialize on HLS verification and debugging. For each aspect mentioned above, we begin with a detailed background study, followed by the presentation of several novel solutions proposed to overcome specific challenges. We then outline future research directions to drive further advancements. Through these efforts, we aim to pave the way for more efficient and scalable deployment of LLMs across a diverse range of applications.

Read more6/18/2024

0

Understanding the Potential of FPGA-Based Spatial Acceleration for Large Language Model Inference

Hongzheng Chen, Jiahao Zhang, Yixiao Du, Shaojie Xiang, Zichao Yue, Niansong Zhang, Yaohui Cai, Zhiru Zhang

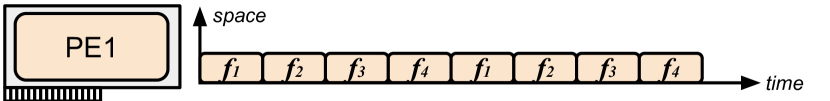

Recent advancements in large language models (LLMs) boasting billions of parameters have generated a significant demand for efficient deployment in inference workloads. The majority of existing approaches rely on temporal architectures that reuse hardware units for different network layers and operators. However, these methods often encounter challenges in achieving low latency due to considerable memory access overhead. This paper investigates the feasibility and potential of model-specific spatial acceleration for LLM inference on FPGAs. Our approach involves the specialization of distinct hardware units for specific operators or layers, facilitating direct communication between them through a dataflow architecture while minimizing off-chip memory accesses. We introduce a comprehensive analytical model for estimating the performance of a spatial LLM accelerator, taking into account the on-chip compute and memory resources available on an FPGA. Through our analysis, we can determine the scenarios in which FPGA-based spatial acceleration can outperform its GPU-based counterpart. To enable more productive implementations of an LLM model on FPGAs, we further provide a library of high-level synthesis (HLS) kernels that are composable and reusable. This library will be made available as open-source. To validate the effectiveness of both our analytical model and HLS library, we have implemented BERT and GPT2 on an AMD Alveo U280 FPGA device. Experimental results demonstrate our approach can achieve up to 13.4x speedup when compared to previous FPGA-based accelerators for the BERT model. For GPT generative inference, we attain a 2.2x speedup compared to DFX, an FPGA overlay, in the prefill stage, while achieving a 1.9x speedup and a 5.7x improvement in energy efficiency compared to the NVIDIA A100 GPU in the decode stage.

Read more4/9/2024

186

Hardware Acceleration of LLMs: A comprehensive survey and comparison

Nikoletta Koilia, Christoforos Kachris

Large Language Models (LLMs) have emerged as powerful tools for natural language processing tasks, revolutionizing the field with their ability to understand and generate human-like text. In this paper, we present a comprehensive survey of the several research efforts that have been presented for the acceleration of transformer networks for Large Language Models using hardware accelerators. The survey presents the frameworks that have been proposed and then performs a qualitative and quantitative comparison regarding the technology, the processing platform (FPGA, ASIC, In-Memory, GPU), the speedup, the energy efficiency, the performance (GOPs), and the energy efficiency (GOPs/W) of each framework. The main challenge in comparison is that every proposed scheme is implemented on a different process technology making hard a fair comparison. The main contribution of this paper is that we extrapolate the results of the performance and the energy efficiency on the same technology to make a fair comparison; one theoretical and one more practical. We implement part of the LLMs on several FPGA chips to extrapolate the results to the same process technology and then we make a fair comparison of the performance.

Read more9/6/2024