Energy Efficient Knapsack Optimization Using Probabilistic Memristor Crossbars

0

🛠️

Sign in to get full access

Overview

- Constrained optimization is crucial for many real-world problems but is computationally challenging

- The big data era demands low-latency, low-energy optimization at the edge, which digital processors struggle with

- Recent efforts using parallel hardware like memristor crossbars and quantum processors have shown promise, but struggle with certain problem types

- The paper presents a novel randomized competitive Ising-inspired (RaCI) algorithm that can efficiently solve these challenging optimization problems

Plain English Explanation

Constrained optimization is a type of mathematical problem that underlies many important real-world challenges, like stock trading and bandwidth allocation. These problems involve finding the best solution while satisfying certain constraints.

However, these optimization problems can be incredibly complex, with the computational difficulty growing exponentially as the problem size increases. This makes them very challenging to solve, especially in the "big data" era where we need to make decisions quickly and efficiently, often right at the "edge" (i.e. close to where the data is being generated).

Traditional digital processors struggle with this type of optimization due to their sequential, non-parallel architecture. Recent efforts have turned to more parallel hardware like memristor crossbars and quantum processors running specialized "annealing" algorithms. While promising, these approaches have been limited to relatively simple, stable optimization problems with sparse or binary representations.

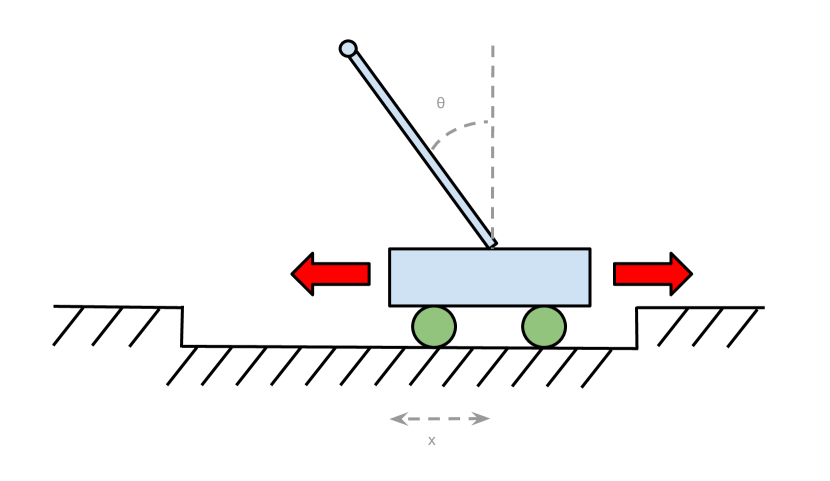

In contrast, most real-world optimization problems have three key features that make them much more difficult: dense and non-binary representations, and destabilizing self-feedback. The knapsack problem is a classic example that embodies these challenges.

The paper introduces a new algorithm called RaCI that can efficiently solve these types of complex optimization problems. It is inspired by the physics of competitive Ising models and can be implemented using specialized analog hardware, providing huge gains in energy efficiency compared to digital and quantum approaches.

Technical Explanation

The core of the RaCI algorithm is a randomized, competitive process that mimics the dynamics of an Ising spin model. It encodes the optimization problem as an energy landscape, where the goal is to find the configuration of "spins" (binary variables) that minimizes the total energy.

The algorithm uses a massively parallel, probabilistic analog memristor crossbar to efficiently explore this energy landscape. The memristor crossbar acts as an analog optimization engine, with the memristor devices representing the binary variables and their interconnections storing the problem constraints and objectives.

By leveraging the intrinsic physics of the analog memristor hardware, the RaCI algorithm can rapidly converge to high-quality solutions for complex optimization problems, even with dense, non-binary representations and destabilizing feedback. The authors demonstrate the effectiveness of their approach on the knapsack problem, showing over 4 orders of magnitude improvement in energy efficiency compared to digital and quantum methods.

Critical Analysis

The paper presents a compelling solution to a critical challenge in the big data era - the need for efficient, low-latency optimization at the edge. The RaCI algorithm and its analog memristor implementation represent a significant advance in addressing the limitations of digital and quantum approaches for these types of complex optimization problems.

That said, the authors acknowledge several caveats and areas for further research. For example, the current implementation is limited to relatively small problem sizes, and the performance may degrade as the problem complexity increases. Additionally, the analog hardware required for the memristor crossbar is still an emerging technology with its own set of challenges around scalability, robustness, and manufacturability.

It would also be valuable to see the RaCI algorithm tested on a wider range of real-world optimization problems beyond the knapsack example, to better understand its broad applicability and limitations. The authors touch on this, but more extensive validation would strengthen the case for this approach.

Overall, the RaCI algorithm and its analog memristor implementation represent an exciting step forward in addressing the computational challenges of constrained optimization. However, continued research and development will be needed to fully realize the potential of this approach and transition it from the lab to real-world deployments.

Conclusion

The paper presents a novel randomized competitive Ising-inspired (RaCI) algorithm that can efficiently solve complex constrained optimization problems, a crucial challenge in the big data era. By leveraging specialized analog hardware like memristor crossbars, the RaCI algorithm achieves over 4 orders of magnitude improvement in energy efficiency compared to digital and quantum approaches.

This work represents an important advance in addressing the limitations of current optimization methods, which struggle with the dense, non-binary representations and destabilizing feedback common in real-world problems. The RaCI algorithm's ability to rapidly converge to high-quality solutions could have significant implications for a wide range of applications, from stock trading to bandwidth allocation.

While the current implementation has some limitations, the potential of this approach is clear. Continued research and development in analog hardware and optimization algorithms like RaCI will be crucial for unlocking the full potential of efficient, low-latency optimization at the edge, with far-reaching implications for society.

This summary was produced with help from an AI and may contain inaccuracies - check out the links to read the original source documents!

Related Papers

🛠️

0

Energy Efficient Knapsack Optimization Using Probabilistic Memristor Crossbars

Jinzhan Li, Suhas Kumar, Su-in Yi

Constrained optimization underlies crucial societal problems (for instance, stock trading and bandwidth allocation), but is often computationally hard (complexity grows exponentially with problem size). The big-data era urgently demands low-latency and low-energy optimization at the edge, which cannot be handled by digital processors due to their non-parallel von Neumann architecture. Recent efforts using massively parallel hardware (such as memristor crossbars and quantum processors) employing annealing algorithms, while promising, have handled relatively easy and stable problems with sparse or binary representations (such as the max-cut or traveling salesman problems).However, most real-world applications embody three features, which are encoded in the knapsack problem, and cannot be handled by annealing algorithms - dense and non-binary representations, with destabilizing self-feedback. Here we demonstrate a post-digital-hardware-friendly randomized competitive Ising-inspired (RaCI) algorithm performing knapsack optimization, experimentally implemented on a foundry-manufactured CMOS-integrated probabilistic analog memristor crossbar. Our solution outperforms digital and quantum approaches by over 4 orders of magnitude in energy efficiency.

Read more7/8/2024

🎯

0

Comparative Evaluation of Memory Technologies for Synaptic Crossbar Arrays- Part 2: Design Knobs and DNN Accuracy Trends

Jeffry Victor, Chunguang Wang, Sumeet K. Gupta

Crossbar memory arrays have been touted as the workhorse of in-memory computing (IMC)-based acceleration of Deep Neural Networks (DNNs), but the associated hardware non-idealities limit their efficacy. To address this, cross-layer design solutions that reduce the impact of hardware non-idealities on DNN accuracy are needed. In Part 1 of this paper, we established the co-optimization strategies for various memory technologies and their crossbar arrays, and conducted a comparative technology evaluation in the context of IMC robustness. In this part, we analyze various design knobs such as array size and bit-slice (number of bits per device) and their impact on the performance of 8T SRAM, ferroelectric transistor (FeFET), Resistive RAM (ReRAM) and spin-orbit-torque magnetic RAM (SOT-MRAM) in the context of inference accuracy at 7nm technology node. Further, we study the effect of circuit design solutions such as Partial Wordline Activation (PWA) and custom ADC reference levels that reduce the hardware non-idealities and comparatively analyze the response of each technology to such accuracy enhancing techniques. Our results on ResNet-20 (with CIFAR-10) show that PWA increases accuracy by up to 32.56% while custom ADC reference levels yield up to 31.62% accuracy enhancement. We observe that compared to the other technologies, FeFET, by virtue of its small layout height and high distinguishability of its memory states, is best suited for large arrays. For higher bit-slices and a more complex dataset (ResNet-50 with Cifar-100) we found that ReRAM matches the performance of FeFET.

Read more8/13/2024

0

Efficient Reinforcement Learning On Passive RRAM Crossbar Array

Arjun Tyagi, Shubham Sahay

The unprecedented growth in the field of machine learning has led to the development of deep neuromorphic networks trained on labelled dataset with capability to mimic or even exceed human capabilities. However, for applications involving continuous decision making in unknown environments, such as rovers for space exploration, robots, unmanned aerial vehicles, etc., explicit supervision and generation of labelled data set is extremely difficult and expensive. Reinforcement learning (RL) allows the agents to take decisions without any (human/external) supervision or training on labelled dataset. However, the conventional implementations of RL on advanced digital CPUs/GPUs incur a significantly large power dissipation owing to their inherent von-Neumann architecture. Although crossbar arrays of emerging non-volatile memories such as resistive (R)RAMs with their innate capability to perform energy-efficient in situ multiply-accumulate operation appear promising for Q-learning-based RL implementations, their limited endurance restricts their application in practical RL systems with overwhelming weight updates. To address this issue and realize the true potential of RRAM-based RL implementations, in this work, for the first time, we perform an algorithm-hardware co-design and propose a novel implementation of Monte Carlo (MC) RL algorithm on passive RRAM crossbar array. We analyse the performance of the proposed MC RL implementation on the classical cart-pole problem and demonstrate that it not only outperforms the prior digital and active 1-Transistor-1-RRAM (1T1R)-based implementations by more than five orders of magnitude in terms of area but is also robust against the spatial and temporal variations and endurance failure of RRAMs.

Read more7/12/2024

0

All-to-all reconfigurability with sparse and higher-order Ising machines

Srijan Nikhar, Sidharth Kannan, Navid Anjum Aadit, Shuvro Chowdhury, Kerem Y. Camsari

Domain-specific hardware to solve computationally hard optimization problems has generated tremendous excitement recently. Here, we evaluate probabilistic bit (p-bit) based on Ising Machines (IM) or p-computers with a benchmark combinatorial optimization problem, namely the 3-regular 3-XOR Satisfiability (3R3X). The 3R3X problem has a glassy energy landscape, and it has recently been used to benchmark various IMs and other solvers. We introduce a multiplexed architecture where p-computers emulate all-to-all (complete) graph functionality despite being interconnected in sparse networks, enabling a highly parallelized chromatic Gibbs sampling. We implement this architecture in FPGAs and show that p-bit networks running an adaptive version of the powerful parallel tempering algorithm demonstrate competitive algorithmic and prefactor advantages over alternative IMs by D-Wave, Toshiba, and Fujitsu, except a greedy algorithm accelerated on a GPU. We further extend our APT results using higher-order interactions in FPGAs and show that while higher-order interactions lead to prefactor advantages, they do not show any algorithmic scaling advantages for the XORSAT problem, settling an open conjecture. Even though FPGA implementations of p-bits are still not quite as fast as the best possible greedy algorithms implemented in GPUs, scaled magnetic versions of p-computers could lead to orders of magnitude over such algorithms according to experimentally established projections.

Read more5/24/2024