FPCA: Field-Programmable Pixel Convolutional Array for Extreme-Edge Intelligence

0

Sign in to get full access

Overview

- The paper describes the development of a Field-Programmable Pixel Convolutional Array (FPCA) for extreme-edge intelligence applications.

- The FPCA is a hardware accelerator that can efficiently run convolutional neural networks (CNNs) on low-power, resource-constrained devices like IoT sensors.

- The key innovations include a flexible, reconfigurable pixel-level convolution architecture and a novel training method to optimize for energy efficiency.

Plain English Explanation

The paper introduces a new type of hardware called the Field-Programmable Pixel Convolutional Array (FPCA). This device is designed to run advanced convolutional neural networks (CNNs) - a type of machine learning model - on small, low-power devices like sensors and cameras.

The FPCA has a unique architecture that allows it to be reconfigured to efficiently perform the calculations required by different CNN models. This flexibility is important because it means the same hardware can be used for a variety of AI-powered applications, rather than needing a specialized chip for each one.

The researchers also developed a new training method to optimize the FPCA for energy efficiency. This is crucial for enabling AI capabilities on battery-powered, extreme-edge devices that need to operate for long periods without recharging.

Overall, the FPCA represents an important advancement in bringing powerful AI closer to the sensors and devices where the data is collected, rather than relying on cloud computing. This can unlock new real-time, low-latency applications in areas like computer vision, autonomous systems, and Internet of Things.

Technical Explanation

The key innovation in this paper is the Field-Programmable Pixel Convolutional Array (FPCA), a hardware accelerator designed for efficient execution of convolutional neural networks (CNNs) on resource-constrained edge devices.

The FPCA architecture features a flexible, reconfigurable pixel-level convolution scheme that can adapt to the specific requirements of different CNN models. This is achieved through a novel Pixel Convolution Unit (PCU) that performs the core convolution operations. By programming the interconnections between these PCUs, the FPCA can be dynamically reconfigured to match the CNN's layer structure.

To further optimize for energy efficiency, the researchers developed a multi-objective training method that jointly optimizes the CNN model parameters and the FPCA hardware configuration. This approach allows the system to find the most energy-efficient implementation for a given CNN, balancing accuracy, latency, and power consumption.

The paper demonstrates the FPCA's effectiveness through extensive experiments. They show that the FPCA can achieve over 100x improvement in energy efficiency compared to a CPU baseline, while maintaining competitive accuracy on standard computer vision benchmarks. The reconfigurability of the FPCA also allows it to efficiently support a diverse range of CNN models.

Critical Analysis

The FPCA introduces an innovative approach to enabling efficient CNN inference on extreme-edge devices. However, the paper does not provide a comprehensive analysis of the FPCA's limitations or potential downsides.

One potential concern is the scalability of the FPCA architecture. While the reconfigurability is a strength, the paper does not discuss how the FPCA design scales to larger, more complex CNN models. The flexibility may come at the cost of area and power efficiency for certain workloads.

Additionally, the training method proposed in the paper relies on jointly optimizing the CNN and FPCA parameters. This may introduce additional complexity and training time compared to a more traditional approach of training the CNN first and then mapping it to the hardware. The feasibility of this method for real-world deployment scenarios is not fully explored.

Further research is needed to understand the generalization of the FPCA beyond the specific CNN models and computer vision tasks evaluated in the paper. Exploring the FPCA's performance on a wider range of applications, including other domains like natural language processing or speech recognition, would help assess its broader applicability.

Conclusion

The Field-Programmable Pixel Convolutional Array (FPCA) presented in this paper represents a significant advancement in bringing efficient CNN inference to resource-constrained, extreme-edge devices. The novel, reconfigurable architecture and energy-optimized training method enable impressive improvements in energy efficiency compared to traditional CPU-based approaches.

This work has the potential to unlock new real-time, low-latency applications of AI in domains like computer vision, autonomous systems, and the Internet of Things. By pushing the intelligence closer to the sensors and devices where data is generated, the FPCA can enable a new generation of smart, energy-efficient edge devices that can operate for extended periods without recharging.

While the paper highlights the FPCA's strengths, further research is needed to fully understand its limitations and broader applicability. Exploring scalability, training complexity, and generalization to other domains would help assess the FPCA's true impact and guide future development of efficient edge AI hardware.

This summary was produced with help from an AI and may contain inaccuracies - check out the links to read the original source documents!

Related Papers

0

FPCA: Field-Programmable Pixel Convolutional Array for Extreme-Edge Intelligence

Zihan Yin, Akhilesh Jaiswal

The rapid advancement of neural network applications necessitates hardware that not only accelerates computation but also adapts efficiently to dynamic processing requirements. While processing-in-pixel has emerged as a promising solution to overcome the bottlenecks of traditional architectures at the extreme-edge, existing implementations face limitations in reconfigurability and scalability due to their static nature and inefficient area usage. Addressing these challenges, we present a novel architecture that significantly enhances the capabilities of processing-in-pixel for convolutional neural networks. Our design innovatively integrates non-volatile memory (NVM) with novel unit pixel circuit design, enabling dynamic reconfiguration of synaptic weights, kernel size, channel size and stride size. Thus offering unprecedented flexibility and adaptability. With using a separate die for pixel circuit and storing synaptic weights, our circuit achieves a substantial reduction in the required area per pixel thereby increasing the density and scalability of the pixel array. Simulation results demonstrate dot product operations of the circuit, the non-linearity of its analog output and a novel bucket-select curvefit model is proposed to capture it. This work not only addresses the limitations of current in-pixel computing approaches but also opens new avenues for developing more efficient, flexible, and scalable neural network hardware, paving the way for advanced AI applications.

Read more8/21/2024

0

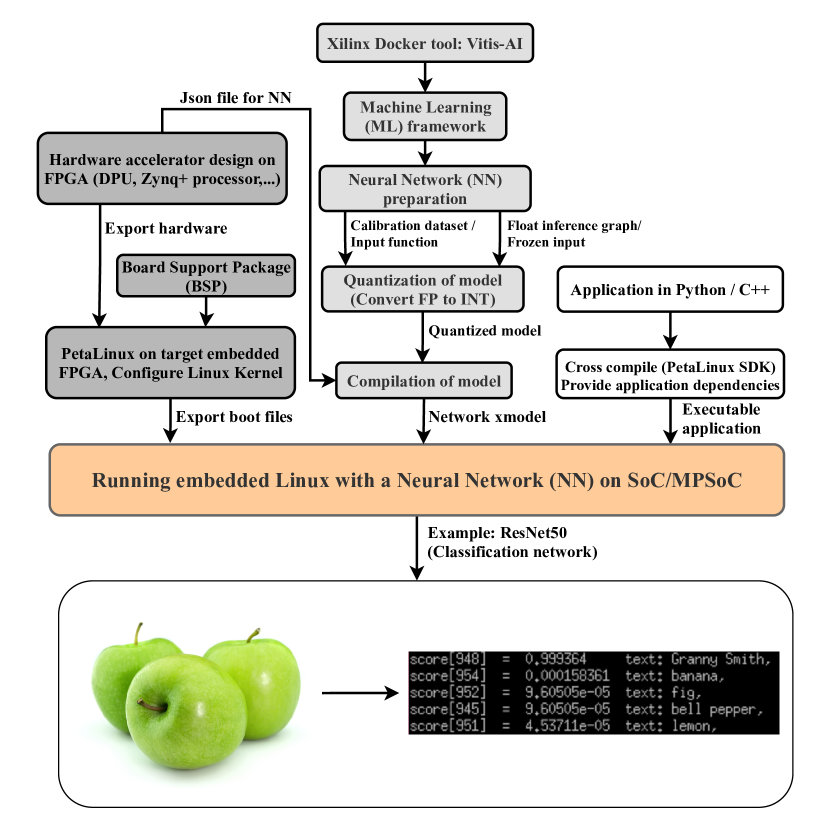

Latency optimized Deep Neural Networks (DNNs): An Artificial Intelligence approach at the Edge using Multiprocessor System on Chip (MPSoC)

Seyed Nima Omidsajedi, Rekha Reddy, Jianming Yi, Jan Herbst, Christoph Lipps, Hans Dieter Schotten

Almost in every heavily computation-dependent application, from 6G communication systems to autonomous driving platforms, a large portion of computing should be near to the client side. Edge computing (AI at Edge) in mobile devices is one of the optimized approaches for addressing this requirement. Therefore, in this work, the possibilities and challenges of implementing a low-latency and power-optimized smart mobile system are examined. Utilizing Field Programmable Gate Array (FPGA) based solutions at the edge will lead to bandwidth-optimized designs and as a consequence can boost the computational effectiveness at a system-level deadline. Moreover, various performance aspects and implementation feasibilities of Neural Networks (NNs) on both embedded FPGA edge devices (using Xilinx Multiprocessor System on Chip (MPSoC)) and Cloud are discussed throughout this research. The main goal of this work is to demonstrate a hybrid system that uses the deep learning programmable engine developed by Xilinx Inc. as the main component of the hardware accelerator. Then based on this design, an efficient system for mobile edge computing is represented by utilizing an embedded solution.

Read more7/29/2024

🌐

0

Data-Driven Pixel Control: Challenges and Prospects

Saurabh Farkya, Zachary Alan Daniels, Aswin Raghavan, Gooitzen van der Wal, Michael Isnardi, Michael Piacentino, David Zhang

Recent advancements in sensors have led to high resolution and high data throughput at the pixel level. Simultaneously, the adoption of increasingly large (deep) neural networks (NNs) has lead to significant progress in computer vision. Currently, visual intelligence comes at increasingly high computational complexity, energy, and latency. We study a data-driven system that combines dynamic sensing at the pixel level with computer vision analytics at the video level and propose a feedback control loop to minimize data movement between the sensor front-end and computational back-end without compromising detection and tracking precision. Our contributions are threefold: (1) We introduce anticipatory attention and show that it leads to high precision prediction with sparse activation of pixels; (2) Leveraging the feedback control, we show that the dimensionality of learned feature vectors can be significantly reduced with increased sparsity; and (3) We emulate analog design choices (such as varying RGB or Bayer pixel format and analog noise) and study their impact on the key metrics of the data-driven system. Comparative analysis with traditional pixel and deep learning models shows significant performance enhancements. Our system achieves a 10X reduction in bandwidth and a 15-30X improvement in Energy-Delay Product (EDP) when activating only 30% of pixels, with a minor reduction in object detection and tracking precision. Based on analog emulation, our system can achieve a throughput of 205 megapixels/sec (MP/s) with a power consumption of only 110 mW per MP, i.e., a theoretical improvement of ~30X in EDP.

Read more8/12/2024

🧠

0

Photonic Neuromorphic Accelerator for Convolutional Neural Networks based on an Integrated Reconfigurable Mesh

Aris Tsirigotis, Gerge Sarantoglou, Stavros Deligiannidis, Erica Sanchez, Ana Gutierrez, Adonis Bogris, Jose Capmany, Charis Mesaritakis

In this work, we present and experimentally validate a passive photonic-integrated neuromorphic accelerator that uses a hardware-friendly optical spectrum slicing technique through a reconfigurable silicon photonic mesh. The proposed scheme acts as an analogue convolutional engine, enabling information preprocessing in the optical domain, dimensionality reduction and extraction of spatio-temporal features. Numerical results demonstrate that utilizing only 7 passive photonic nodes, critical modules of a digital convolutional neural network can be replaced. As a result, a 98.6% accuracy on the MNIST dataset was achieved, with a power consumption reduction of at least 26% compared to digital CNNs. Experimental results confirm these findings, achieving 97.7% accuracy with only 3 passive nodes.

Read more5/13/2024