Graph Attention-Based Symmetry Constraint Extraction for Analog Circuits

0

Sign in to get full access

Overview

- This paper presents a graph attention-based method for extracting symmetry constraints in analog circuit layouts.

- The proposed approach uses a graph neural network to learn the relationships between circuit components and automatically identify symmetry constraints.

- The method can help streamline the analog design process by reducing the manual effort required to specify symmetry constraints.

Plain English Explanation

Analog circuits, like those used in audio equipment or sensors, often require careful design to ensure they function properly. One important aspect of this design is ensuring that certain components are positioned symmetrically on the circuit board. This symmetry helps the circuit perform better and reduces unwanted effects.

Traditionally, engineers have had to manually identify and specify these symmetry constraints during the design process. This can be a time-consuming and error-prone task, especially for complex circuits.

The researchers in this paper propose a new approach that uses a type of machine learning model called a graph neural network to automatically detect and extract the symmetry constraints in an analog circuit layout. The graph neural network learns to understand the relationships between the different components in the circuit, similar to how a human engineer would. It can then use this understanding to identify the symmetry constraints, which the researchers can then incorporate into the circuit design process.

This automation can help make the analog design process more efficient and less prone to human error. It could be particularly useful for complex circuits where manually identifying all the necessary symmetry constraints would be challenging.

Technical Explanation

The key technical components of this paper are:

-

Graph Representation of Analog Circuits: The researchers represent the analog circuit layout as a graph, where the nodes correspond to circuit components and the edges represent the connections between them. This graph-based representation allows the use of graph neural networks for analyzing the circuit structure.

-

Graph Attention Network: The researchers employ a graph attention network (GAT) to learn the relationships between circuit components. The GAT model learns to assign different levels of importance (attention) to the connections between components, allowing it to identify patterns and symmetries in the circuit layout.

-

Symmetry Constraint Extraction: The trained GAT model is used to extract the symmetry constraints in the analog circuit layout. The model's attention mechanism indicates which components should be placed symmetrically, and the researchers can then incorporate these constraints into the circuit design process.

The researchers evaluate their approach on several benchmark analog circuit layouts and demonstrate that it can effectively identify symmetry constraints, outperforming traditional rule-based methods. This highlights the potential of graph neural networks for automating key tasks in analog circuit design.

Critical Analysis

The researchers acknowledge several limitations of their approach:

-

Dependence on Circuit Netlists: The proposed method requires the availability of a detailed circuit netlist, which may not always be the case, especially in the early stages of the design process.

-

Potential Sensitivity to Circuit Complexity: While the researchers test their method on several benchmark circuits, it is unclear how well it would scale to highly complex, real-world analog circuits with thousands of components.

Further research could explore ways to address these limitations, such as developing techniques to handle incomplete circuit information or analyzing the scalability of the graph attention-based approach.

Conclusion

This paper presents a novel graph attention-based method for extracting symmetry constraints in analog circuit layouts. By automating this critical design task, the proposed approach has the potential to streamline the analog design process and reduce the manual effort required.

The ability to automatically identify symmetry constraints could be particularly valuable for complex analog circuits, where manually specifying these constraints can be challenging and time-consuming. As the complexity of analog systems continues to grow, this type of automated, data-driven approach may become increasingly important for maintaining design quality and productivity.

This summary was produced with help from an AI and may contain inaccuracies - check out the links to read the original source documents!

Related Papers

0

Graph Attention-Based Symmetry Constraint Extraction for Analog Circuits

Qi Xu, Lijie Wang, Jing Wang, Lin Cheng, Song Chen, Yi Kang

In recent years, analog circuits have received extensive attention and are widely used in many emerging applications. The high demand for analog circuits necessitates shorter circuit design cycles. To achieve the desired performance and specifications, various geometrical symmetry constraints must be carefully considered during the analog layout process. However, the manual labeling of these constraints by experienced analog engineers is a laborious and time-consuming process. To handle the costly runtime issue, we propose a graph-based learning framework to automatically extract symmetric constraints in analog circuit layout. The proposed framework leverages the connection characteristics of circuits and the devices' information to learn the general rules of symmetric constraints, which effectively facilitates the extraction of device-level constraints on circuit netlists. The experimental results demonstrate that compared to state-of-the-art symmetric constraint detection approaches, our framework achieves higher accuracy and F1-score.

Read more5/17/2024

0

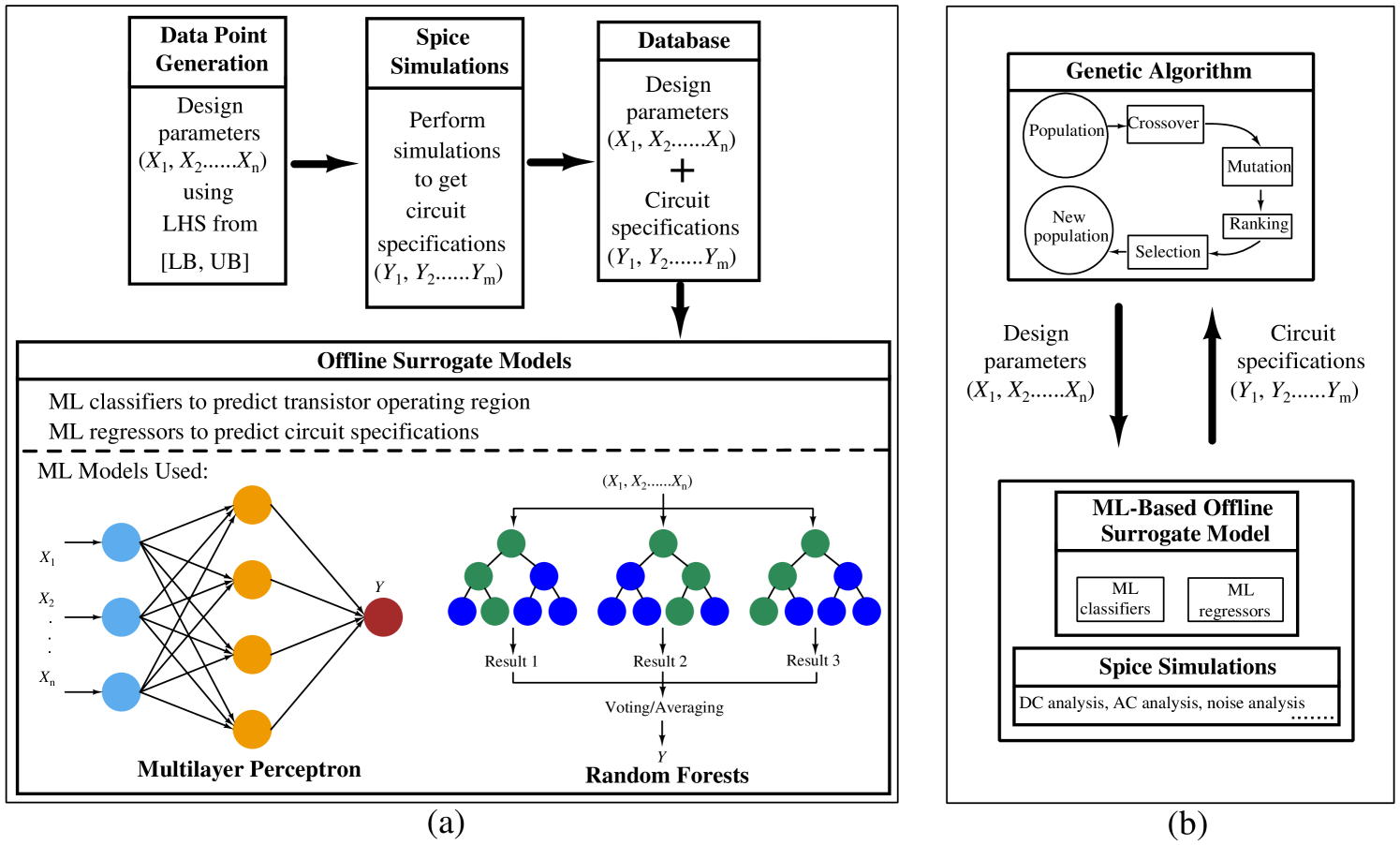

Machine Learning Driven Global Optimisation Framework for Analog Circuit Design

Ria Rashid, Komala Krishna, Clint Pazhayidam George, Nandakumar Nambath

We propose a machine learning-driven optimisation framework for analog circuit design in this paper. The primary objective is to determine the device sizes for the optimal performance of analog circuits for a given set of specifications. Our methodology entails employing machine learning models and spice simulations to direct the optimisation algorithm towards achieving the optimal design for analog circuits. Machine learning based global offline surrogate models, with the circuit design parameters as the input, are built in the design space for the analog circuits under study and is used to guide the optimisation algorithm, resulting in faster convergence and a reduced number of spice simulations. Multi-layer perceptron and random forest regressors are employed to predict the required design specifications of the analog circuit. Since the saturation condition of transistors is vital in the proper working of analog circuits, multi-layer perceptron classifiers are used to predict the saturation condition of each transistor in the circuit. The feasibility of the candidate solutions is verified using machine learning models before invoking spice simulations. We validate the proposed framework using three circuit topologies--a bandgap reference, a folded cascode operational amplifier, and a two-stage operational amplifier. The simulation results show better optimum values and lower standard deviations for fitness functions after convergence. Incorporating the machine learning-based predictions proposed in the optimisation method has resulted in the reduction of spice calls by 56%, 59%, and 83% when compared with standard approaches in the three test cases considered in the study.

Read more4/5/2024

0

LLM-Enhanced Bayesian Optimization for Efficient Analog Layout Constraint Generation

Guojin Chen, Keren Zhu, Seunggeun Kim, Hanqing Zhu, Yao Lai, Bei Yu, David Z. Pan

Analog layout synthesis faces significant challenges due to its dependence on manual processes, considerable time requirements, and performance instability. Current Bayesian Optimization (BO)-based techniques for analog layout synthesis, despite their potential for automation, suffer from slow convergence and extensive data needs, limiting their practical application. This paper presents the texttt{LLANA} framework, a novel approach that leverages Large Language Models (LLMs) to enhance BO by exploiting the few-shot learning abilities of LLMs for more efficient generation of analog design-dependent parameter constraints. Experimental results demonstrate that texttt{LLANA} not only achieves performance comparable to state-of-the-art (SOTA) BO methods but also enables a more effective exploration of the analog circuit design space, thanks to LLM's superior contextual understanding and learning efficiency. The code is available at https://github.com/dekura/LLANA.

Read more6/21/2024

0

CIRCUITSYNTH: Leveraging Large Language Models for Circuit Topology Synthesis

Prashanth Vijayaraghavan, Luyao Shi, Ehsan Degan, Xin Zhang

Circuit topology generation plays a crucial role in the design of electronic circuits, influencing the fundamental functionality of the circuit. In this paper, we introduce CIRCUITSYNTH, a novel approach that harnesses LLMs to facilitate the automated synthesis of valid circuit topologies. With a dataset comprising both valid and invalid circuit configurations, CIRCUITSYNTH employs a sophisticated two-phase methodology, comprising Circuit Topology Generation and Circuit Topology Refinement. Experimental results demonstrate the effectiveness of CIRCUITSYNTH compared to various fine-tuned LLM variants. Our approach lays the foundation for future research aimed at enhancing circuit efficiency and specifying output voltage, thus enabling the automated generation of circuit topologies with improved performance and adherence to design requirements.

Read more7/17/2024