LLM-Enhanced Bayesian Optimization for Efficient Analog Layout Constraint Generation

0

Sign in to get full access

Overview

- This paper presents a new approach to generating analog layout constraints using a combination of large language models (LLMs) and Bayesian optimization.

- The proposed method aims to improve the efficiency of the constraint generation process, which is a critical step in analog circuit design.

- The paper demonstrates the effectiveness of the LLM-enhanced Bayesian optimization approach through experiments and comparisons with existing techniques.

Plain English Explanation

Designing analog circuits, such as those used in electronics and communication systems, is a complex and challenging task. One crucial step in this process is generating constraints, which are rules or guidelines that the circuit must follow to ensure it functions correctly.

The researchers in this paper have developed a new way to generate these constraints that is more efficient and effective than previous methods. They combine the power of large language models (LLMs), which are AI systems trained on vast amounts of text data, with a technique called Bayesian optimization.

LLMs can understand and generate human-like text, which the researchers use to capture the domain knowledge and design intuitions of experienced circuit designers. They then use Bayesian optimization, a powerful optimization algorithm, to explore the space of possible constraints and find the ones that work best for a given circuit design.

By integrating these two powerful techniques, the researchers have created a system that can generate high-quality constraints more quickly and with less manual effort than traditional methods. This could significantly streamline the analog circuit design process, making it easier and more efficient for engineers to create the advanced electronics we rely on in our daily lives.

Technical Explanation

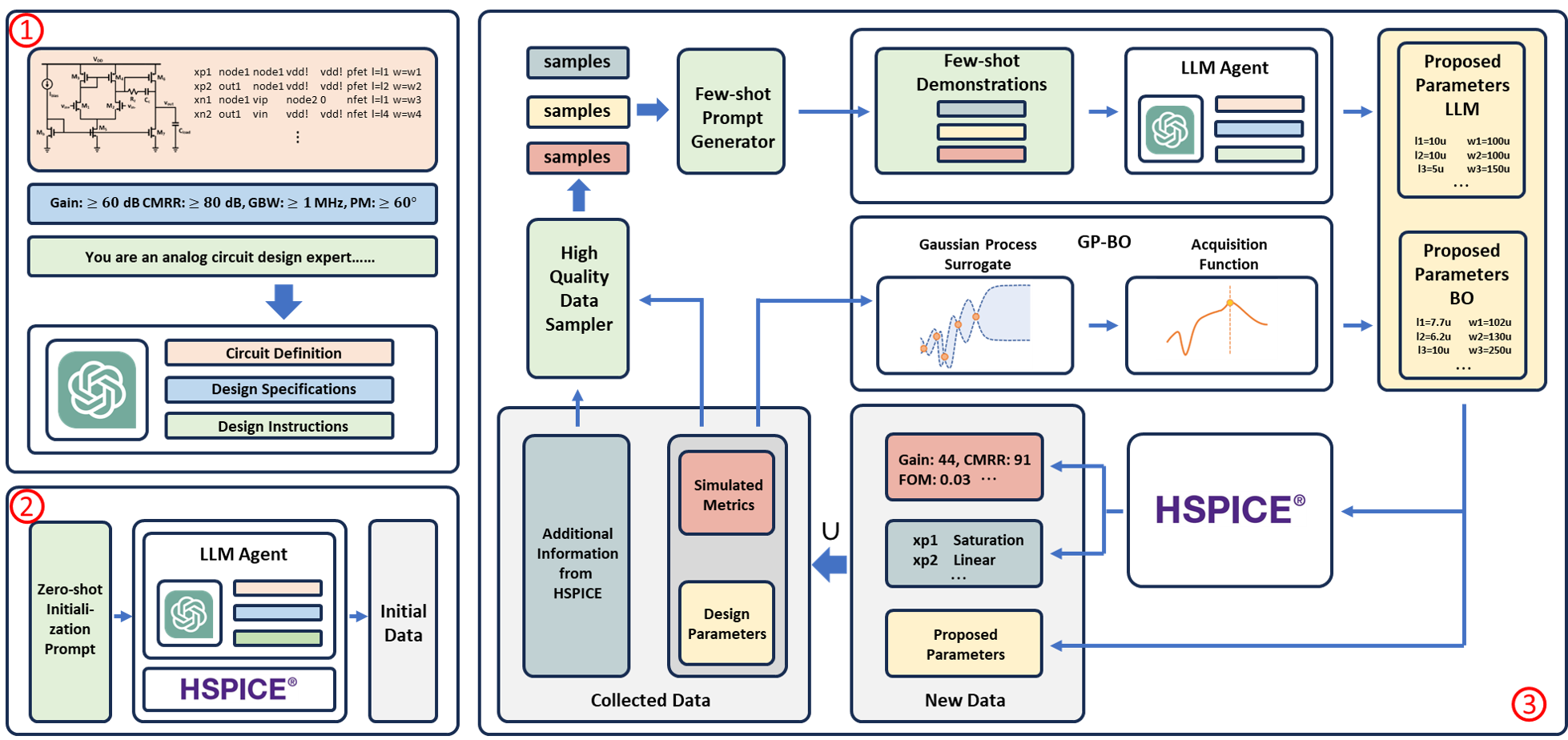

The paper introduces a novel approach to analog layout constraint generation that leverages the strengths of large language models (LLMs) and Bayesian optimization.

The key components of the proposed method are:

-

LLM-based Constraint Modeling: The researchers use an LLM to capture the domain knowledge and design intuitions of experienced circuit designers, which are then used to generate candidate constraints.

-

Bayesian Optimization for Constraint Selection: The researchers employ Bayesian optimization to efficiently explore the space of possible constraints and identify the ones that best meet the desired performance criteria for a given circuit design.

-

Iterative Refinement: The system iteratively refines the generated constraints by incorporating feedback from the circuit designer, further improving the quality and relevance of the final constraint set.

The paper presents experimental results demonstrating the effectiveness of the LLM-enhanced Bayesian optimization approach compared to existing techniques. The method is shown to generate high-quality constraints more efficiently, reducing the time and manual effort required for the constraint generation process.

Critical Analysis

The paper presents a well-designed and methodologically sound approach to addressing the challenge of analog layout constraint generation. The incorporation of LLMs to leverage domain knowledge and Bayesian optimization to efficiently explore the constraint space is a clever and promising strategy.

However, the paper does not delve into the potential limitations or caveats of the proposed method. For example, the performance and reliability of the LLM-based constraint modeling may be influenced by the quality and coverage of the training data, and the paper does not discuss how the system might handle edge cases or unexpected circuit designs.

Additionally, while the experimental results are promising, the paper could benefit from a more thorough analysis of the tradeoffs and potential drawbacks of the LLM-enhanced Bayesian optimization approach compared to other state-of-the-art techniques in the field. Exploring the scalability and generalizability of the method across a wider range of analog circuit designs would also strengthen the critical analysis.

Conclusion

This paper presents a novel and promising approach to analog layout constraint generation that combines the strengths of large language models and Bayesian optimization. The LLM-enhanced Bayesian optimization method has the potential to significantly streamline the analog circuit design process by generating high-quality constraints more efficiently than traditional techniques.

The integration of domain knowledge captured by LLMs and the powerful optimization capabilities of Bayesian optimization is a compelling solution to a critical challenge in analog circuit design. While the paper provides a solid technical foundation, further research is needed to explore the limitations, scalability, and broader applicability of the proposed method.

Overall, this work represents an important step forward in the field of analog circuit design, and the findings may have broader implications for the use of advanced AI techniques in other engineering and optimization domains.

This summary was produced with help from an AI and may contain inaccuracies - check out the links to read the original source documents!

Related Papers

0

LLM-Enhanced Bayesian Optimization for Efficient Analog Layout Constraint Generation

Guojin Chen, Keren Zhu, Seunggeun Kim, Hanqing Zhu, Yao Lai, Bei Yu, David Z. Pan

Analog layout synthesis faces significant challenges due to its dependence on manual processes, considerable time requirements, and performance instability. Current Bayesian Optimization (BO)-based techniques for analog layout synthesis, despite their potential for automation, suffer from slow convergence and extensive data needs, limiting their practical application. This paper presents the texttt{LLANA} framework, a novel approach that leverages Large Language Models (LLMs) to enhance BO by exploiting the few-shot learning abilities of LLMs for more efficient generation of analog design-dependent parameter constraints. Experimental results demonstrate that texttt{LLANA} not only achieves performance comparable to state-of-the-art (SOTA) BO methods but also enables a more effective exploration of the analog circuit design space, thanks to LLM's superior contextual understanding and learning efficiency. The code is available at https://github.com/dekura/LLANA.

Read more6/21/2024

0

ADO-LLM: Analog Design Bayesian Optimization with In-Context Learning of Large Language Models

Yuxuan Yin, Yu Wang, Boxun Xu, Peng Li

Analog circuit design requires substantial human expertise and involvement, which is a significant roadblock to design productivity. Bayesian Optimization (BO), a popular machine learning based optimization strategy, has been leveraged to automate analog design given its applicability across various circuit topologies and technologies. Traditional BO methods employ black box Gaussian Process surrogate models and optimized labeled data queries to find optimization solutions by trading off between exploration and exploitation. However, the search for the optimal design solution in BO can be expensive from both a computational and data usage point of view, particularly for high dimensional optimization problems. This paper presents ADO-LLM, the first work integrating large language models (LLMs) with Bayesian Optimization for analog design optimization. ADO-LLM leverages the LLM's ability to infuse domain knowledge to rapidly generate viable design points to remedy BO's inefficiency in finding high value design areas specifically under the limited design space coverage of the BO's probabilistic surrogate model. In the meantime, sampling of design points evaluated in the iterative BO process provides quality demonstrations for the LLM to generate high quality design points while leveraging infused broad design knowledge. Furthermore, the diversity brought by BO's exploration enriches the contextual understanding of the LLM and allows it to more broadly search in the design space and prevent repetitive and redundant suggestions. We evaluate the proposed framework on two different types of analog circuits and demonstrate notable improvements in design efficiency and effectiveness.

Read more6/28/2024

🛠️

0

A Sober Look at LLMs for Material Discovery: Are They Actually Good for Bayesian Optimization Over Molecules?

Agustinus Kristiadi, Felix Strieth-Kalthoff, Marta Skreta, Pascal Poupart, Al'an Aspuru-Guzik, Geoff Pleiss

Automation is one of the cornerstones of contemporary material discovery. Bayesian optimization (BO) is an essential part of such workflows, enabling scientists to leverage prior domain knowledge into efficient exploration of a large molecular space. While such prior knowledge can take many forms, there has been significant fanfare around the ancillary scientific knowledge encapsulated in large language models (LLMs). However, existing work thus far has only explored LLMs for heuristic materials searches. Indeed, recent work obtains the uncertainty estimate -- an integral part of BO -- from point-estimated, non-Bayesian LLMs. In this work, we study the question of whether LLMs are actually useful to accelerate principled Bayesian optimization in the molecular space. We take a sober, dispassionate stance in answering this question. This is done by carefully (i) viewing LLMs as fixed feature extractors for standard but principled BO surrogate models and by (ii) leveraging parameter-efficient finetuning methods and Bayesian neural networks to obtain the posterior of the LLM surrogate. Our extensive experiments with real-world chemistry problems show that LLMs can be useful for BO over molecules, but only if they have been pretrained or finetuned with domain-specific data.

Read more5/30/2024

🛸

0

Interactive and Automatic Generation of Primitive Custom Circuit Layout Using LLMs

Geunyoung You, Youjin Byun, Sojin Lim, Jaeduk Han

In this study, we investigate the use of Large Language Models (LLMs) for the interactive and automated production of customs circuit layouts described in natural language. Our proposed layout automation process leverages a template-and-grid-based layout generation framework to create process-portable layout generators tailored for various custom circuits, including standard cells and high-speed mixed-signal circuits. However, rather than directly describing the layout generators in traditional programming language, we utilize natural language using LLMs to make the layout generation process more intuitive and efficient. This approach also supports interactive modifications of the layout generator code, enhancing customization capabilities. We demonstrate the effectiveness of our LLM-based layout generation method across several custom circuit examples, such as logic standard cells, a serializer and a strong arm latch, including their completeness in terms of Design Rule Check (DRC), Layout Versus Schematic (LVS) test, and post-layout performance for high-speed circuits. Our experimental results indicate that LLMs can generate a diverse range of circuit layouts with substantial customization options.

Read more8/15/2024