Interactive and Automatic Generation of Primitive Custom Circuit Layout Using LLMs

0

🛸

Sign in to get full access

Overview

- Researchers investigate using Large Language Models (LLMs) to automate the production of custom circuit layouts based on natural language descriptions.

- They leverage a template-and-grid-based framework to create customizable layout generators for various circuits, including standard cells and high-speed mixed-signal circuits.

- Instead of directly programming the layout generators, they use natural language with LLMs to make the process more intuitive and interactive.

- The approach supports interactive modifications to the layout generator code, enhancing customization capabilities.

Plain English Explanation

The researchers in this study are exploring how to use Large Language Models (LLMs) to automate the creation of custom circuit layouts. Instead of having engineers write complex code to design the circuit layouts, the researchers want to let them use simple, natural language descriptions.

The process works by having a framework that can generate different circuit layouts based on templates and grids. Normally, engineers would have to program this framework directly, which can be challenging. But the researchers are using LLMs to allow the engineers to describe the circuit layouts in plain language. This makes the process more intuitive and efficient.

The approach also lets engineers interactively modify the layout generator code, giving them more flexibility to customize the circuits. The researchers demonstrate this technique across several custom circuit examples, showing that the LLM-based layout generation can produce complete, high-quality layouts that pass all the necessary design checks.

Technical Explanation

The researchers propose a template-and-grid-based layout generation framework that can create customized layout generators for various custom circuits, including standard cells and high-speed mixed-signal circuits. Instead of directly programming these layout generators in traditional code, the researchers leverage Large Language Models (LLMs) to allow users to describe the circuit layouts in natural language.

This LLM-based approach enables more intuitive and interactive layout generation, as users can provide high-level descriptions and interactively modify the layout generator code. The researchers demonstrate the effectiveness of their method across several custom circuit examples, including logic standard cells, a serializer, and a strong arm latch.

The researchers evaluate the completeness of the generated layouts in terms of Design Rule Check (DRC), Layout Versus Schematic (LVS) testing, and post-layout performance for high-speed circuits. Their experimental results indicate that LLMs can generate a diverse range of circuit layouts with substantial customization options.

Critical Analysis

The researchers provide a compelling approach to automating the layout generation process for custom circuits using LLMs. By leveraging natural language descriptions, they make the process more accessible and interactive for engineers, who can focus on high-level design concepts rather than low-level programming.

However, the paper does not address the potential limitations of this approach, such as the accuracy and reliability of the LLM-generated layouts, or the computational resources required to run the LLM models. Additionally, the researchers do not discuss the potential challenges in training the LLMs to understand and generate complex circuit layout specifications.

Further research could explore ways to fine-tune or adapt LLMs specifically for the task of circuit layout generation, as well as investigate the scalability and robustness of the approach for a wider range of circuit designs and complexity levels.

Conclusion

This study presents an innovative approach to leveraging Large Language Models (LLMs) for the interactive and automated production of custom circuit layouts. By using natural language descriptions instead of traditional programming, the researchers have created a more intuitive and customizable layout generation process.

The researchers demonstrate the effectiveness of their LLM-based method across several custom circuit examples, showing that the generated layouts are complete and meet the necessary design requirements. This work could potentially streamline the circuit design process and make it more accessible to a wider range of engineers, ultimately contributing to the advancement of custom circuit development.

This summary was produced with help from an AI and may contain inaccuracies - check out the links to read the original source documents!

Related Papers

🛸

0

Interactive and Automatic Generation of Primitive Custom Circuit Layout Using LLMs

Geunyoung You, Youjin Byun, Sojin Lim, Jaeduk Han

In this study, we investigate the use of Large Language Models (LLMs) for the interactive and automated production of customs circuit layouts described in natural language. Our proposed layout automation process leverages a template-and-grid-based layout generation framework to create process-portable layout generators tailored for various custom circuits, including standard cells and high-speed mixed-signal circuits. However, rather than directly describing the layout generators in traditional programming language, we utilize natural language using LLMs to make the layout generation process more intuitive and efficient. This approach also supports interactive modifications of the layout generator code, enhancing customization capabilities. We demonstrate the effectiveness of our LLM-based layout generation method across several custom circuit examples, such as logic standard cells, a serializer and a strong arm latch, including their completeness in terms of Design Rule Check (DRC), Layout Versus Schematic (LVS) test, and post-layout performance for high-speed circuits. Our experimental results indicate that LLMs can generate a diverse range of circuit layouts with substantial customization options.

Read more8/15/2024

0

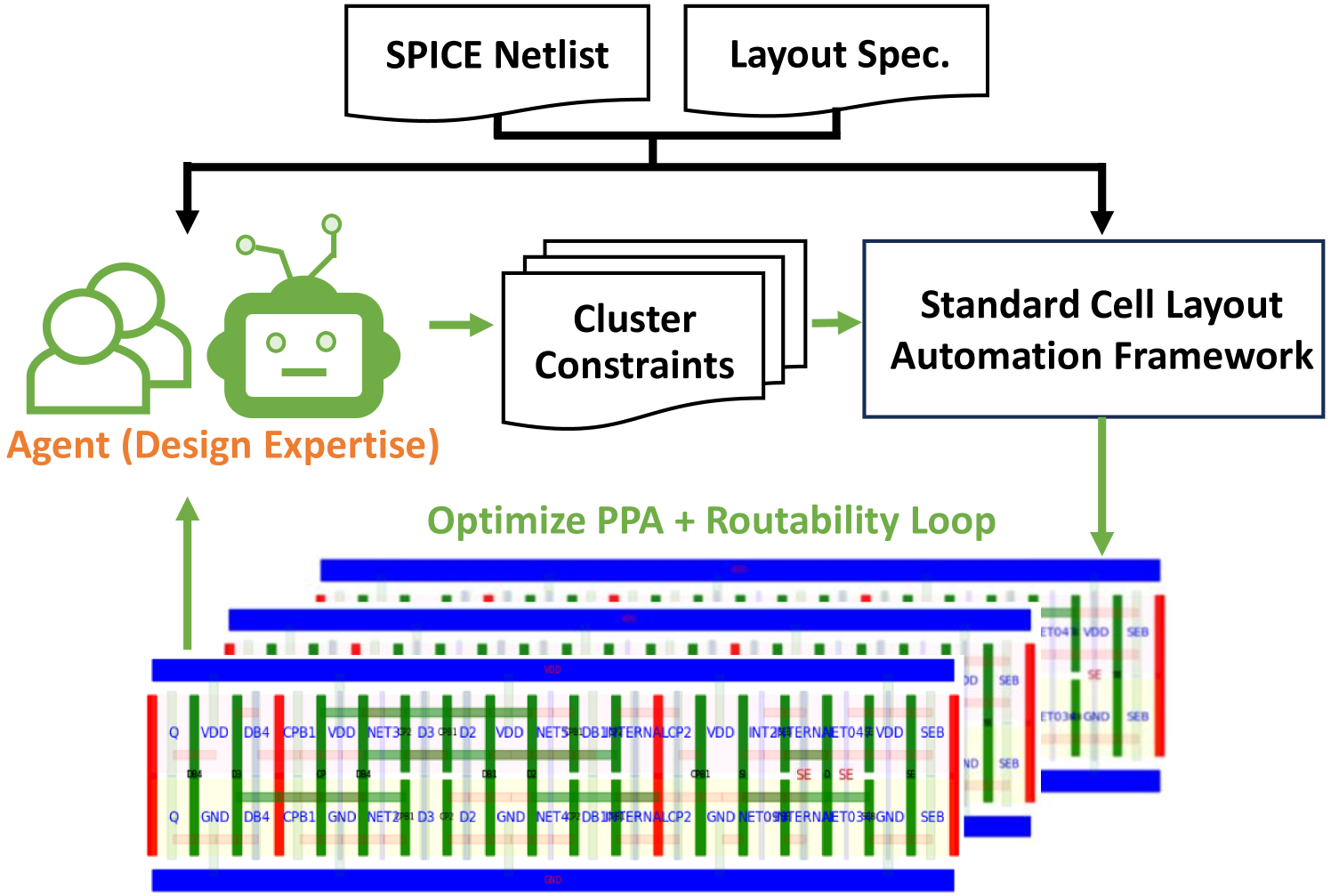

Large Language Model (LLM) for Standard Cell Layout Design Optimization

Chia-Tung Ho, Haoxing Ren

Standard cells are essential components of modern digital circuit designs. With process technologies advancing toward 2nm, more routability issues have arisen due to the decreasing number of routing tracks, increasing number and complexity of design rules, and strict patterning rules. The state-of-the-art standard cell design automation framework is able to automatically design standard cell layouts in advanced nodes, but it is still struggling to generate highly competitive Performance-Power-Area (PPA) and routable cell layouts for complex sequential cell designs. Consequently, a novel and efficient methodology incorporating the expertise of experienced human designers to incrementally optimize the PPA of cell layouts is highly necessary and essential. High-quality device clustering, with consideration of netlist topology, diffusion sharing/break and routability in the layouts, can reduce complexity and assist in finding highly competitive PPA, and routable layouts faster. In this paper, we leverage the natural language and reasoning ability of Large Language Model (LLM) to generate high-quality cluster constraints incrementally to optimize the cell layout PPA and debug the routability with ReAct prompting. On a benchmark of sequential standard cells in 2nm, we demonstrate that the proposed method not only achieves up to 19.4% smaller cell area, but also generates 23.5% more LVS/DRC clean cell layouts than previous work. In summary, the proposed method not only successfully reduces cell area by 4.65% on average, but also is able to fix routability in the cell layout designs.

Read more6/12/2024

🧪

0

Digital ASIC Design with Ongoing LLMs: Strategies and Prospects

Maoyang Xiang, Emil Goh, T. Hui Teo

The escalating complexity of modern digital systems has imposed significant challenges on integrated circuit (IC) design, necessitating tools that can simplify the IC design flow. The advent of Large Language Models (LLMs) has been seen as a promising development, with the potential to automate the generation of Hardware Description Language (HDL) code, thereby streamlining digital IC design. However, the practical application of LLMs in this area faces substantial hurdles. Notably, current LLMs often generate HDL code with small but critical syntax errors and struggle to accurately convey the high-level semantics of circuit designs. These issues significantly undermine the utility of LLMs for IC design, leading to misinterpretations and inefficiencies. In response to these challenges, this paper presents targeted strategies to harness the capabilities of LLMs for digital ASIC design. We outline approaches that improve the reliability and accuracy of HDL code generation by LLMs. As a practical demonstration of these strategies, we detail the development of a simple three-phase Pulse Width Modulation (PWM) generator. This project, part of the Efabless AI-Generated Open-Source Chip Design Challenge, successfully passed the Design Rule Check (DRC) and was fabricated, showcasing the potential of LLMs to enhance digital ASIC design. This work underscores the feasibility and benefits of integrating LLMs into the IC design process, offering a novel approach to overcoming the complexities of modern digital systems.

Read more5/7/2024

0

CIRCUITSYNTH: Leveraging Large Language Models for Circuit Topology Synthesis

Prashanth Vijayaraghavan, Luyao Shi, Ehsan Degan, Xin Zhang

Circuit topology generation plays a crucial role in the design of electronic circuits, influencing the fundamental functionality of the circuit. In this paper, we introduce CIRCUITSYNTH, a novel approach that harnesses LLMs to facilitate the automated synthesis of valid circuit topologies. With a dataset comprising both valid and invalid circuit configurations, CIRCUITSYNTH employs a sophisticated two-phase methodology, comprising Circuit Topology Generation and Circuit Topology Refinement. Experimental results demonstrate the effectiveness of CIRCUITSYNTH compared to various fine-tuned LLM variants. Our approach lays the foundation for future research aimed at enhancing circuit efficiency and specifying output voltage, thus enabling the automated generation of circuit topologies with improved performance and adherence to design requirements.

Read more7/17/2024