Large Language Model (LLM) for Standard Cell Layout Design Optimization

0

Sign in to get full access

Overview

- This paper explores the use of Large Language Models (LLMs) for optimizing the design of standard cell layouts in integrated circuit (IC) design.

- The researchers developed a framework that leverages the powerful text generation and understanding capabilities of LLMs to assist in the standard cell layout design process.

- The proposed approach aims to improve the efficiency and performance of standard cell layout design, which is a crucial step in the IC design workflow.

Plain English Explanation

Integrated circuits, or computer chips, are made up of tiny electronic components called standard cells. The arrangement and placement of these standard cells on the chip, known as the layout, is a crucial step in the design process. Efficient standard cell layout design can improve the performance and power efficiency of the final chip.

In this paper, the researchers investigated using large language models (LLMs) to assist in the standard cell layout design process. LLMs are AI systems that can understand and generate human-like text, and the researchers hypothesized that these models could be leveraged to streamline the standard cell layout design task.

The researchers developed a framework that allows the LLM to "read" the design specifications and constraints, and then generate optimized layout suggestions. This could potentially save designers a significant amount of time and effort compared to the traditional manual design process.

The key idea is that the LLM can learn from a large corpus of past successful layout designs, and then use that knowledge to propose new layout arrangements that meet the specific requirements of a given design. This approach is similar to how LLMs can be used to assist in other design tasks, such as 3D indoor scene layout generation and editing.

Overall, the researchers believe that integrating LLMs into the standard cell layout design workflow could lead to more efficient and high-performing integrated circuits, with potential applications in a wide range of electronic devices and systems.

Technical Explanation

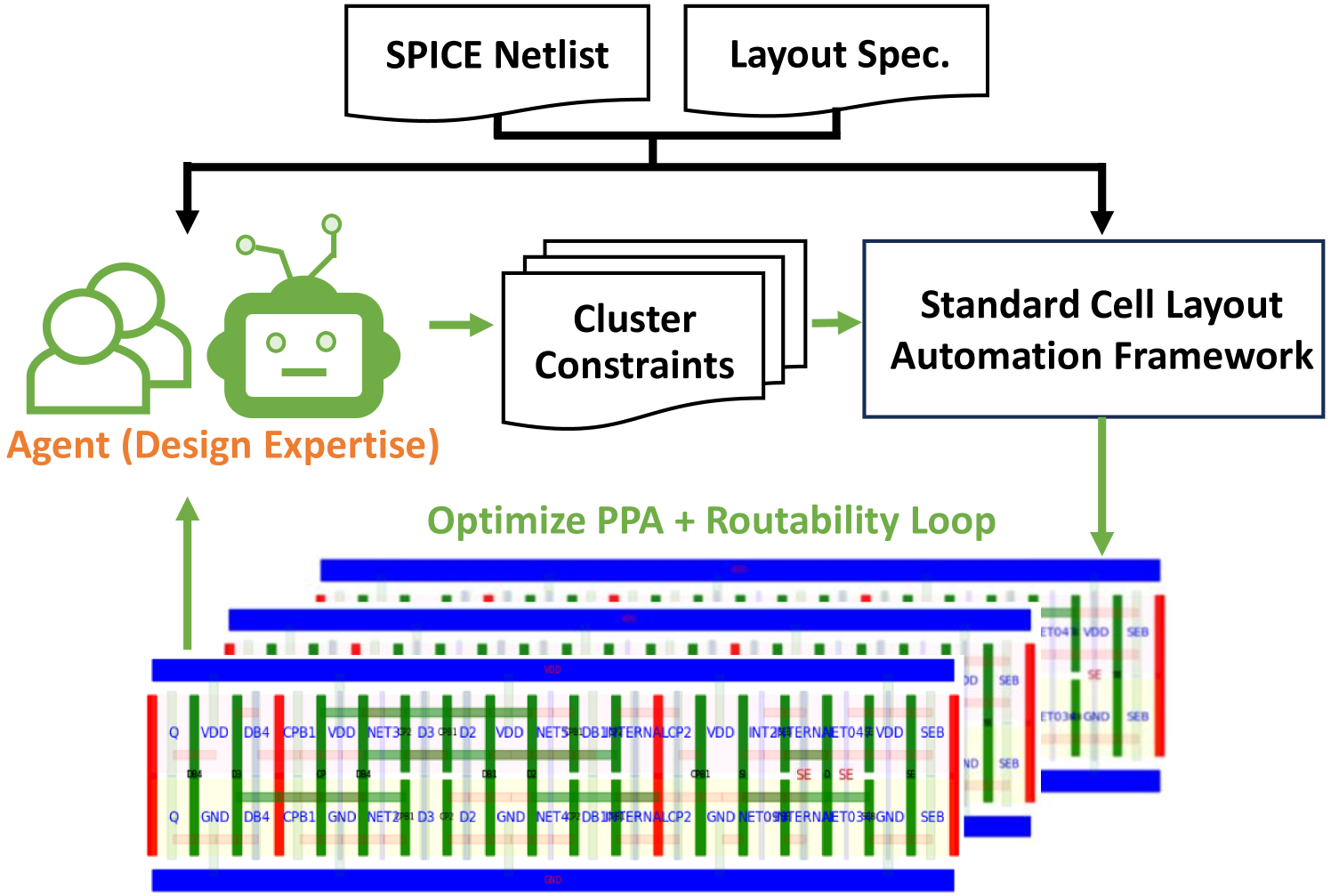

The researchers developed a framework that leverages the powerful text generation and understanding capabilities of large language models (LLMs) to assist in the standard cell layout design process.

The key components of the proposed approach include:

- Design Specification Encoding: The design specifications and constraints are encoded into a textual format that can be processed by the LLM.

- Layout Suggestion Generation: The LLM is fine-tuned on a large corpus of past successful layout designs, and then used to generate optimized layout suggestions based on the encoded design specifications.

- Layout Evaluation and Optimization: The generated layout suggestions are evaluated using metrics such as area, timing, and power, and an optimization process is used to refine the layout and meet the design requirements.

The researchers evaluated their framework on a set of standard cell layout design benchmarks, and demonstrated that the LLM-based approach can outperform traditional optimization methods in terms of layout quality and design time.

This work builds upon previous research on using LLMs for efficient analog layout design and for assisting in wireless network design, showing the versatility of LLMs in various engineering design domains.

Critical Analysis

The researchers have presented a promising approach for leveraging the capabilities of large language models to assist in the standard cell layout design process. However, there are a few potential limitations and areas for further research:

- Dataset and Fine-tuning Challenges: The success of the LLM-based approach relies on the availability of a large and diverse dataset of past successful layout designs. Obtaining and curating such a dataset may be a significant challenge, especially for newer or specialized design domains.

- Interpretability and Explainability: While the LLM-based approach can generate optimized layout suggestions, it may be difficult to understand the reasoning behind these suggestions. Improving the interpretability and explainability of the LLM's decision-making process could be an important area for future research.

- Integration with Existing Design Flows: Seamlessly integrating the LLM-based layout optimization framework into existing integrated circuit design workflows may require significant engineering effort and collaboration with industry partners.

Conclusion

This paper presents a novel framework that leverages the powerful text generation and understanding capabilities of large language models to assist in the standard cell layout design process. By encoding the design specifications and constraints into a format that can be processed by the LLM, the researchers were able to generate optimized layout suggestions that outperform traditional optimization methods.

The proposed approach has the potential to significantly improve the efficiency and performance of integrated circuit design, with applications across a wide range of electronic devices and systems. While there are some challenges to address, such as dataset curation and model interpretability, the use of LLMs for standard cell layout design optimization represents an exciting and promising direction for future research.

This summary was produced with help from an AI and may contain inaccuracies - check out the links to read the original source documents!

Related Papers

0

Large Language Model (LLM) for Standard Cell Layout Design Optimization

Chia-Tung Ho, Haoxing Ren

Standard cells are essential components of modern digital circuit designs. With process technologies advancing toward 2nm, more routability issues have arisen due to the decreasing number of routing tracks, increasing number and complexity of design rules, and strict patterning rules. The state-of-the-art standard cell design automation framework is able to automatically design standard cell layouts in advanced nodes, but it is still struggling to generate highly competitive Performance-Power-Area (PPA) and routable cell layouts for complex sequential cell designs. Consequently, a novel and efficient methodology incorporating the expertise of experienced human designers to incrementally optimize the PPA of cell layouts is highly necessary and essential. High-quality device clustering, with consideration of netlist topology, diffusion sharing/break and routability in the layouts, can reduce complexity and assist in finding highly competitive PPA, and routable layouts faster. In this paper, we leverage the natural language and reasoning ability of Large Language Model (LLM) to generate high-quality cluster constraints incrementally to optimize the cell layout PPA and debug the routability with ReAct prompting. On a benchmark of sequential standard cells in 2nm, we demonstrate that the proposed method not only achieves up to 19.4% smaller cell area, but also generates 23.5% more LVS/DRC clean cell layouts than previous work. In summary, the proposed method not only successfully reduces cell area by 4.65% on average, but also is able to fix routability in the cell layout designs.

Read more6/12/2024

🛸

0

Interactive and Automatic Generation of Primitive Custom Circuit Layout Using LLMs

Geunyoung You, Youjin Byun, Sojin Lim, Jaeduk Han

In this study, we investigate the use of Large Language Models (LLMs) for the interactive and automated production of customs circuit layouts described in natural language. Our proposed layout automation process leverages a template-and-grid-based layout generation framework to create process-portable layout generators tailored for various custom circuits, including standard cells and high-speed mixed-signal circuits. However, rather than directly describing the layout generators in traditional programming language, we utilize natural language using LLMs to make the layout generation process more intuitive and efficient. This approach also supports interactive modifications of the layout generator code, enhancing customization capabilities. We demonstrate the effectiveness of our LLM-based layout generation method across several custom circuit examples, such as logic standard cells, a serializer and a strong arm latch, including their completeness in terms of Design Rule Check (DRC), Layout Versus Schematic (LVS) test, and post-layout performance for high-speed circuits. Our experimental results indicate that LLMs can generate a diverse range of circuit layouts with substantial customization options.

Read more8/15/2024

💬

0

Large Language Models Understand Layouts

Weiming Li, Manni Duan, Dong An, Yan Shao

Large language models (LLMs) demonstrate extraordinary abilities in a wide range of natural language processing (NLP) tasks. In this paper, we show that, beyond text understanding capability, LLMs are capable of processing text layouts that are denoted by spatial markers. They are able to answer questions that require explicit spatial perceiving and reasoning, while a drastic performance drop is observed when the spatial markers from the original data are excluded. We perform a series of experiments with the GPT-3.5, Baichuan2, Llama2 and ChatGLM3 models on various types of layout-sensitive datasets for further analysis. The experimental results reveal that the layout understanding ability of LLMs is mainly introduced by the coding data for pretraining, which is further enhanced at the instruction-tuning stage. In addition, layout understanding can be enhanced by integrating low-cost, auto-generated data approached by a novel text game. Finally, we show that layout understanding ability is beneficial for building efficient visual question-answering (VQA) systems.

Read more8/29/2024

0

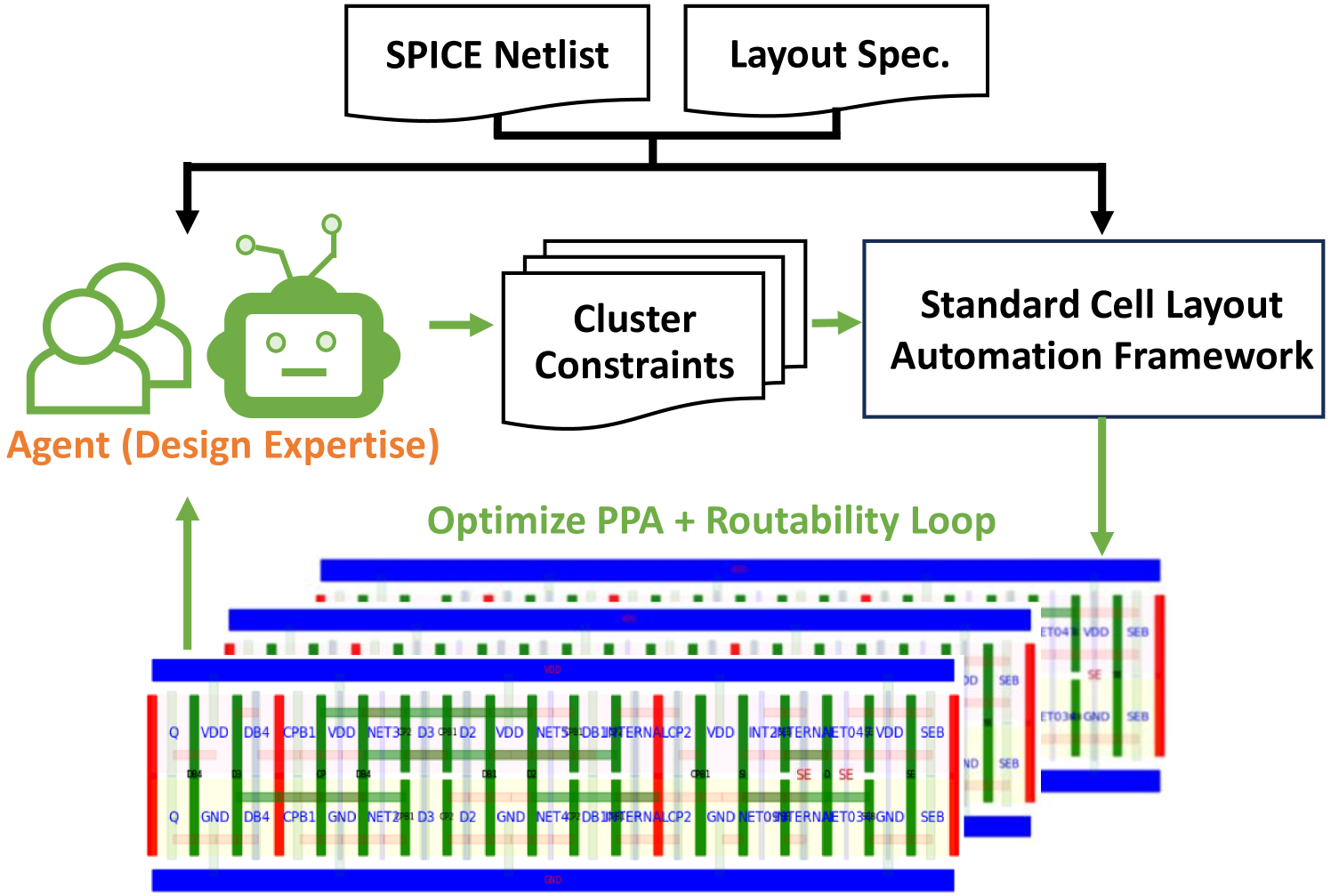

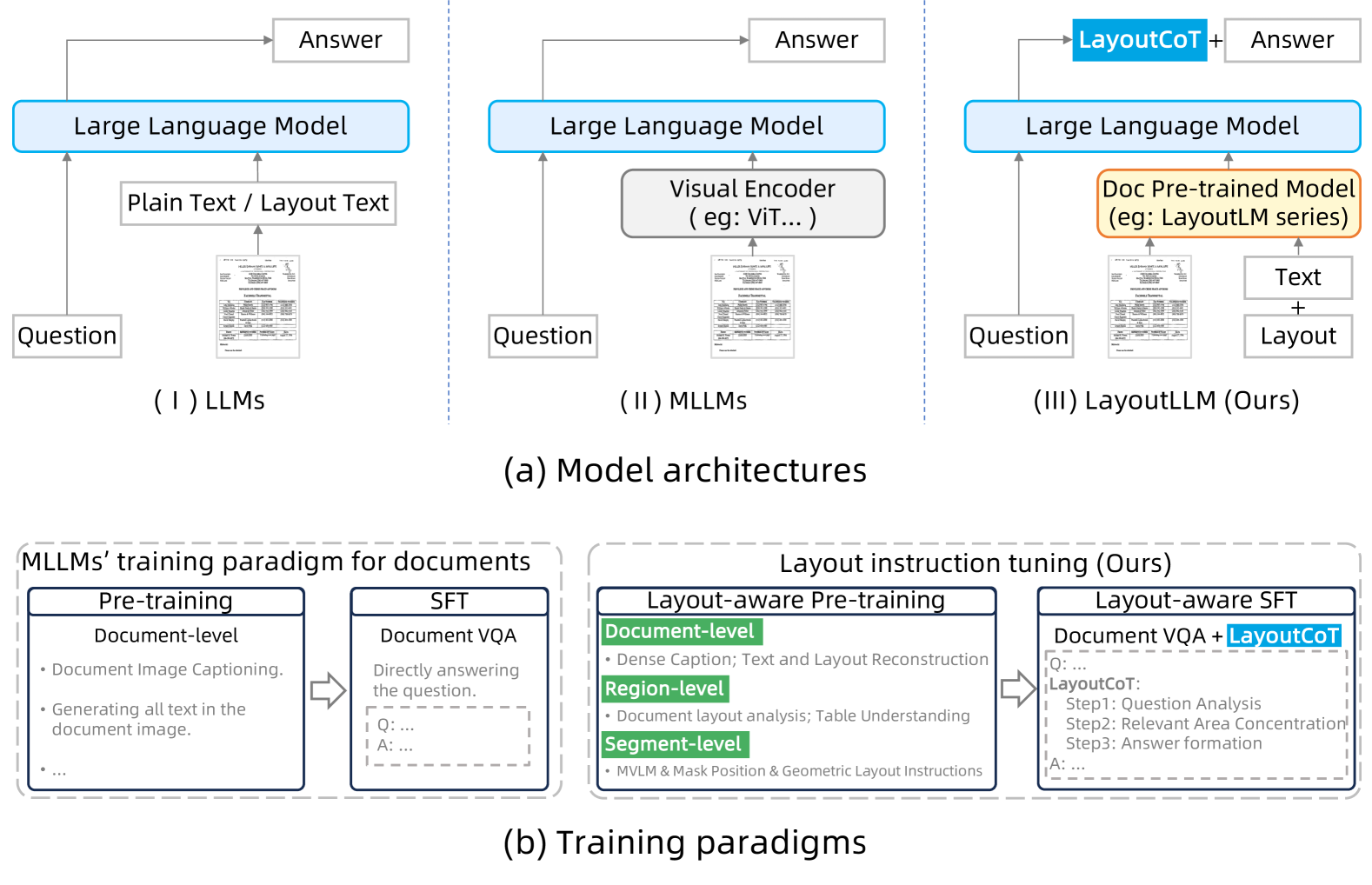

LayoutLLM: Layout Instruction Tuning with Large Language Models for Document Understanding

Chuwei Luo, Yufan Shen, Zhaoqing Zhu, Qi Zheng, Zhi Yu, Cong Yao

Recently, leveraging large language models (LLMs) or multimodal large language models (MLLMs) for document understanding has been proven very promising. However, previous works that employ LLMs/MLLMs for document understanding have not fully explored and utilized the document layout information, which is vital for precise document understanding. In this paper, we propose LayoutLLM, an LLM/MLLM based method for document understanding. The core of LayoutLLM is a layout instruction tuning strategy, which is specially designed to enhance the comprehension and utilization of document layouts. The proposed layout instruction tuning strategy consists of two components: Layout-aware Pre-training and Layout-aware Supervised Fine-tuning. To capture the characteristics of document layout in Layout-aware Pre-training, three groups of pre-training tasks, corresponding to document-level, region-level and segment-level information, are introduced. Furthermore, a novel module called layout chain-of-thought (LayoutCoT) is devised to enable LayoutLLM to focus on regions relevant to the question and generate accurate answers. LayoutCoT is effective for boosting the performance of document understanding. Meanwhile, it brings a certain degree of interpretability, which could facilitate manual inspection and correction. Experiments on standard benchmarks show that the proposed LayoutLLM significantly outperforms existing methods that adopt open-source 7B LLMs/MLLMs for document understanding. The training data of the LayoutLLM is publicly available at https://github.com/AlibabaResearch/AdvancedLiterateMachinery/tree/main/DocumentUnderstanding/LayoutLLM

Read more4/9/2024