MONAS: Efficient Zero-Shot Neural Architecture Search for MCUs

0

Sign in to get full access

Overview

- The paper presents MONAS, an efficient zero-shot neural architecture search (NAS) approach for microcontroller units (MCUs).

- MONAS leverages a custom performance prediction model to optimize neural network architectures for MCUs without the need for expensive hardware evaluations.

- The proposed method demonstrates state-of-the-art performance on multiple MCU-specific tasks while significantly reducing the computational cost of the NAS process.

Plain English Explanation

In the world of artificial intelligence (AI), designing efficient neural network architectures is crucial, especially when it comes to running AI models on small, low-power devices like microcontrollers (MCUs). MONAS: Efficient Zero-Shot Neural Architecture Search for MCUs introduces a new approach called MONAS that makes this process much more efficient.

Traditional neural architecture search (NAS) methods require extensive testing on real hardware, which can be time-consuming and expensive. MONAS, on the other hand, uses a custom performance prediction model to estimate how well a given neural network architecture will perform on an MCU, without the need for actual hardware testing. This "zero-shot" approach allows MONAS to explore a much larger space of potential architectures and find the most efficient ones for MCU deployment.

The researchers demonstrate that MONAS can outperform state-of-the-art models on several MCU-specific tasks, such as image classification and keyword spotting, while using a fraction of the computational resources required by traditional NAS methods. This means that developers can now create highly optimized AI models for low-power devices more quickly and cost-effectively.

Technical Explanation

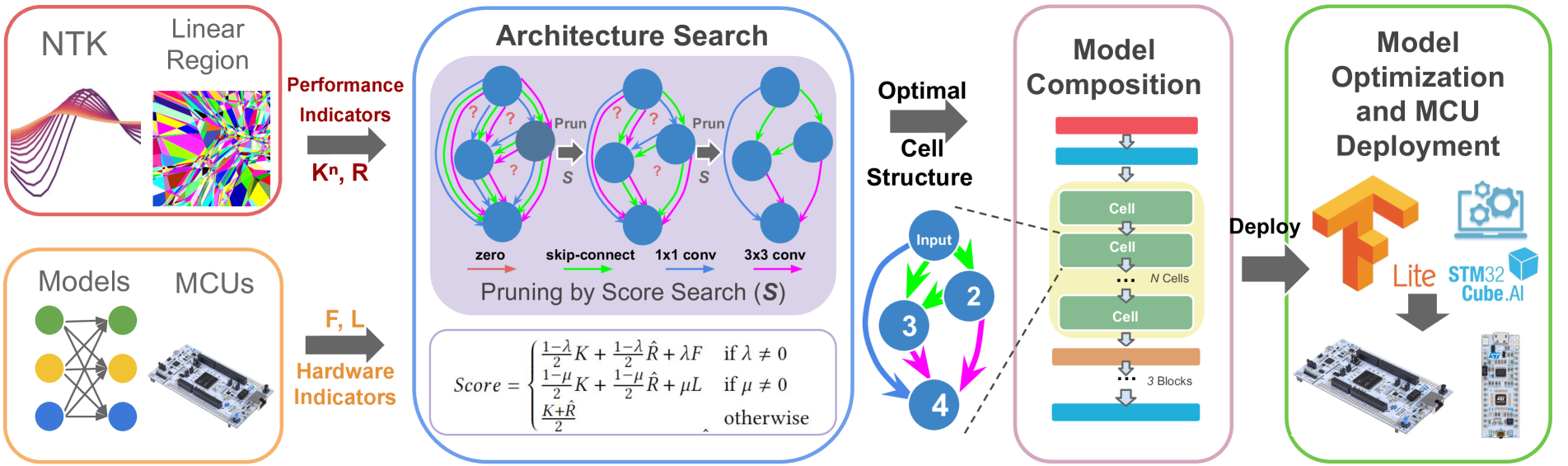

The key innovation in MONAS: Efficient Zero-Shot Neural Architecture Search for MCUs is the use of a custom performance prediction model to guide the neural architecture search process. This model, trained on a diverse dataset of neural network architectures and their corresponding MCU performance metrics, allows MONAS to estimate the expected latency, memory usage, and other relevant characteristics of a given architecture without the need for physical hardware testing.

The researchers first compile a comprehensive dataset of neural network architectures and their measured performance on a range of MCU platforms. They then train a multi-task prediction model to forecast these performance metrics based on the architectural features of the networks. This model serves as the core of the MONAS approach, enabling efficient exploration of the vast search space of possible neural network designs.

During the architecture search process, MONAS generates candidate neural network architectures and uses the performance prediction model to evaluate their suitability for MCU deployment. This allows the method to quickly identify promising designs and focus the search on the most efficient architectures, without the time and cost of physical hardware evaluation.

The researchers demonstrate the effectiveness of MONAS on several MCU-specific tasks, including image classification and keyword spotting. Their results show that MONAS can outperform state-of-the-art NAS methods while using significantly fewer computational resources, making it a valuable tool for developing optimized AI models for low-power embedded systems.

Critical Analysis

The MONAS: Efficient Zero-Shot Neural Architecture Search for MCUs paper presents a compelling approach to neural architecture search that addresses the challenges of designing efficient models for microcontroller units. The use of a performance prediction model to enable "zero-shot" evaluation of candidate architectures is a clever and effective solution to the high cost of hardware-based NAS.

However, the paper does acknowledge some limitations of the MONAS approach. The performance prediction model is trained on a finite dataset of neural network architectures and MCU performance measurements, which may not capture the full diversity of possible designs or hardware platforms. There is also the potential for discrepancies between the predicted and actual performance of the searched architectures, which could lead to suboptimal designs being selected.

Additionally, while MONAS demonstrates strong results on the specific tasks and MCU platforms evaluated in the paper, it would be valuable to see how the method performs on a wider range of applications and hardware targets. Expanding the evaluation to include more diverse workloads and real-world deployment scenarios would help validate the broader applicability of the MONAS approach.

Overall, the MONAS: Efficient Zero-Shot Neural Architecture Search for MCUs paper presents an innovative and promising solution to the challenge of efficient neural architecture search for microcontroller units. The researchers have made a significant contribution to the field, and their work opens up opportunities for further research and development in this important area of embedded AI.

Conclusion

MONAS: Efficient Zero-Shot Neural Architecture Search for MCUs introduces a novel approach to neural architecture search that addresses the unique challenges of designing efficient AI models for microcontroller units. By leveraging a custom performance prediction model, MONAS can explore a wide range of neural network architectures and identify the most optimal designs for MCU deployment, without the need for expensive hardware testing.

The researchers have demonstrated the effectiveness of MONAS on several MCU-specific tasks, showing that it can outperform state-of-the-art NAS methods while significantly reducing the computational cost of the search process. This has important implications for the development of embedded AI systems, as it allows developers to create highly optimized models for low-power devices more quickly and cost-effectively.

While the MONAS: Efficient Zero-Shot Neural Architecture Search for MCUs paper presents a compelling solution, there are still opportunities for further research and refinement, such as expanding the evaluation to a broader range of applications and hardware platforms. Nevertheless, the MONAS approach represents a significant step forward in the field of neural architecture search for microcontroller units, and it has the potential to have a lasting impact on the development of efficient, low-power AI systems.

This summary was produced with help from an AI and may contain inaccuracies - check out the links to read the original source documents!

Related Papers

0

MONAS: Efficient Zero-Shot Neural Architecture Search for MCUs

Ye Qiao, Haocheng Xu, Yifan Zhang, Sitao Huang

Neural Architecture Search (NAS) has proven effective in discovering new Convolutional Neural Network (CNN) architectures, particularly for scenarios with well-defined accuracy optimization goals. However, previous approaches often involve time-consuming training on super networks or intensive architecture sampling and evaluations. Although various zero-cost proxies correlated with CNN model accuracy have been proposed for efficient architecture search without training, their lack of hardware consideration makes it challenging to target highly resource-constrained edge devices such as microcontroller units (MCUs). To address these challenges, we introduce MONAS, a novel hardware-aware zero-shot NAS framework specifically designed for MCUs in edge computing. MONAS incorporates hardware optimality considerations into the search process through our proposed MCU hardware latency estimation model. By combining this with specialized performance indicators (proxies), MONAS identifies optimal neural architectures without incurring heavy training and evaluation costs, optimizing for both hardware latency and accuracy under resource constraints. MONAS achieves up to a 1104x improvement in search efficiency over previous work targeting MCUs and can discover CNN models with over 3.23x faster inference on MCUs while maintaining similar accuracy compared to more general NAS approaches.

Read more8/28/2024

0

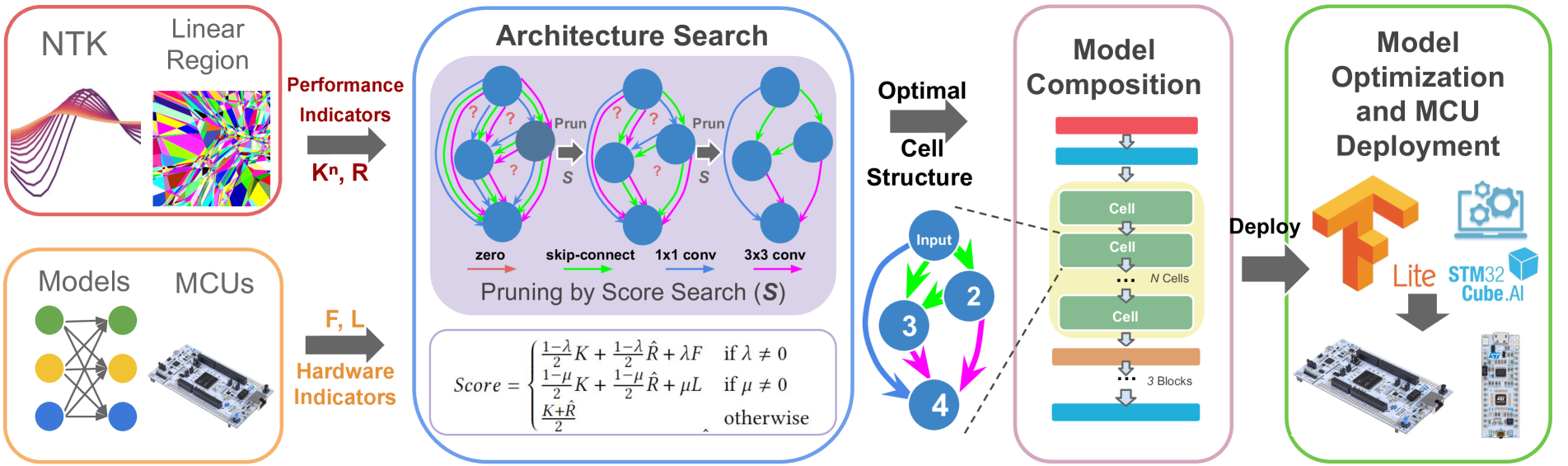

Zero-Shot Neural Architecture Search: Challenges, Solutions, and Opportunities

Guihong Li, Duc Hoang, Kartikeya Bhardwaj, Ming Lin, Zhangyang Wang, Radu Marculescu

Recently, zero-shot (or training-free) Neural Architecture Search (NAS) approaches have been proposed to liberate NAS from the expensive training process. The key idea behind zero-shot NAS approaches is to design proxies that can predict the accuracy of some given networks without training the network parameters. The proxies proposed so far are usually inspired by recent progress in theoretical understanding of deep learning and have shown great potential on several datasets and NAS benchmarks. This paper aims to comprehensively review and compare the state-of-the-art (SOTA) zero-shot NAS approaches, with an emphasis on their hardware awareness. To this end, we first review the mainstream zero-shot proxies and discuss their theoretical underpinnings. We then compare these zero-shot proxies through large-scale experiments and demonstrate their effectiveness in both hardware-aware and hardware-oblivious NAS scenarios. Finally, we point out several promising ideas to design better proxies. Our source code and the list of related papers are available on https://github.com/SLDGroup/survey-zero-shot-nas.

Read more6/19/2024

0

Multi-Objective Neural Architecture Search for In-Memory Computing

Md Hasibul Amin, Mohammadreza Mohammadi, Ramtin Zand

In this work, we employ neural architecture search (NAS) to enhance the efficiency of deploying diverse machine learning (ML) tasks on in-memory computing (IMC) architectures. Initially, we design three fundamental components inspired by the convolutional layers found in VGG and ResNet models. Subsequently, we utilize Bayesian optimization to construct a convolutional neural network (CNN) model with adaptable depths, employing these components. Through the Bayesian search algorithm, we explore a vast search space comprising over 640 million network configurations to identify the optimal solution, considering various multi-objective cost functions like accuracy/latency and accuracy/energy. Our evaluation of this NAS approach for IMC architecture deployment spans three distinct image classification datasets, demonstrating the effectiveness of our method in achieving a balanced solution characterized by high accuracy and reduced latency and energy consumption.

Read more6/12/2024

0

TinyTNAS: GPU-Free, Time-Bound, Hardware-Aware Neural Architecture Search for TinyML Time Series Classification

Bidyut Saha, Riya Samanta, Soumya K. Ghosh, Ram Babu Roy

In this work, we present TinyTNAS, a novel hardware-aware multi-objective Neural Architecture Search (NAS) tool specifically designed for TinyML time series classification. Unlike traditional NAS methods that rely on GPU capabilities, TinyTNAS operates efficiently on CPUs, making it accessible for a broader range of applications. Users can define constraints on RAM, FLASH, and MAC operations to discover optimal neural network architectures within these parameters. Additionally, the tool allows for time-bound searches, ensuring the best possible model is found within a user-specified duration. By experimenting with benchmark dataset UCI HAR, PAMAP2, WISDM, MIT BIH, and PTB Diagnostic ECG Databas TinyTNAS demonstrates state-of-the-art accuracy with significant reductions in RAM, FLASH, MAC usage, and latency. For example, on the UCI HAR dataset, TinyTNAS achieves a 12x reduction in RAM usage, a 144x reduction in MAC operations, and a 78x reduction in FLASH memory while maintaining superior accuracy and reducing latency by 149x. Similarly, on the PAMAP2 and WISDM datasets, it achieves a 6x reduction in RAM usage, a 40x reduction in MAC operations, an 83x reduction in FLASH, and a 67x reduction in latency, all while maintaining superior accuracy. Notably, the search process completes within 10 minutes in a CPU environment. These results highlight TinyTNAS's capability to optimize neural network architectures effectively for resource-constrained TinyML applications, ensuring both efficiency and high performance. The code for TinyTNAS is available at the GitHub repository and can be accessed at https://github.com/BidyutSaha/TinyTNAS.git.

Read more8/30/2024