Quality Scalable Quantization Methodology for Deep Learning on Edge

0

🤿

Sign in to get full access

Overview

- Reducing the energy consumption and size of Convolutional Neural Networks (CNNs) for edge computing

- Proposing a Systematic Quality Scalable Design Methodology

- Incorporating Quality Scalable Quantization and Quality Scalable Multipliers

Plain English Explanation

Deep learning models like CNNs require a lot of computational power, which is a problem for running them on small, low-power devices like smartphones or sensors. This paper presents a new approach to make deep learning models more efficient and suitable for edge computing.

The key idea is to reduce the size and energy use of CNN models in two ways:

-

Quality Scalable Quantization: The paper proposes encoding the filter values in the CNN model using just 3 bits instead of the usual 32 bits. This reduces the model size and the amount of data that needs to be sent to the edge device. A specialized hardware decoder on the edge device can then reconstruct the approximate filter values.

-

Quality Scalable Multipliers: The paper also introduces a new type of multiplier circuit that can perform multiplications more efficiently. It does this by representing numbers in a more compact format and approximating the least significant bits. This saves energy during the multiplication operations.

By combining these two techniques, the paper shows that the memory and power requirements of deep learning models can be greatly reduced, making it more practical to run them on small, low-power edge devices. The experiments demonstrate significant reductions in model size and energy use while maintaining the model's accuracy.

Technical Explanation

The paper proposes a Systematic Quality Scalable Design Methodology to address the high computational costs of deep learning models like CNNs. This methodology has two main components:

-

Quality Scalable Quantization: The first component is a parameter compression technique that approximates the representation of values in the CNN's filters using just 3 bits instead of the standard 32 bits. This is done by encoding the filter values and providing a specialized hardware decoder on the edge device to reconstruct the approximate filter values. This reduces the size of the CNN model and the amount of data that needs to be transmitted to the edge device.

-

Quality Scalable Multipliers: The second component is a new type of multiplier circuit that reduces the number of partial products by converting the numbers to a more compact representation called canonic sign digit. It further approximates the least significant bits to save energy during the multiplication operations.

The experiments were conducted on the LeNet and ConvNet architectures. The results show an increase of up to 6% in the number of zeros in the model and memory savings of up to 82.4919%, while maintaining near state-of-the-art accuracy. This demonstrates the effectiveness of the proposed methodology in reducing the memory and power requirements of deep learning models, making them more suitable for deployment on edge computing devices.

Critical Analysis

The paper presents a promising approach to making deep learning models more efficient for edge computing. The key strengths are the two-pronged strategy of model compression through quantization and energy-efficient multipliers. This combination enables significant reductions in model size and power consumption without major accuracy degradation.

However, the paper does not address the potential impact of the approximations on model performance in different domains or tasks. The experiments are limited to image classification, and it would be valuable to explore the generalization of the techniques to other types of deep learning models and applications.

Additionally, the paper does not provide much analysis on the trade-offs between the degree of quantization/approximation and the resulting accuracy. It would be helpful to understand the sensitivity of the models to these hyperparameters and how to best balance the efficiency gains and model quality.

Further research could also investigate the integration of these techniques with other model optimization approaches, such as pruning or mixed-precision training, to achieve even greater efficiency.

Conclusion

This paper presents a Systematic Quality Scalable Design Methodology that combines Quality Scalable Quantization and Quality Scalable Multipliers to significantly reduce the memory and power requirements of deep learning models, particularly CNNs. The experiments demonstrate impressive reductions in model size and energy consumption while maintaining near state-of-the-art accuracy, making this approach a promising step towards enabling the deployment of deep learning on edge computing devices. Further research is needed to explore the generalization of these techniques and their integration with other optimization methods.

This summary was produced with help from an AI and may contain inaccuracies - check out the links to read the original source documents!

Related Papers

🤿

0

Quality Scalable Quantization Methodology for Deep Learning on Edge

Salman Abdul Khaliq, Rehan Hafiz

Deep Learning Architectures employ heavy computations and bulk of the computational energy is taken up by the convolution operations in the Convolutional Neural Networks. The objective of our proposed work is to reduce the energy consumption and size of CNN for using machine learning techniques in edge computing on ubiquitous computing devices. We propose Systematic Quality Scalable Design Methodology consisting of Quality Scalable Quantization on a higher abstraction level and Quality Scalable Multipliers at lower abstraction level. The first component consists of parameter compression where we approximate representation of values in filters of deep learning models by encoding in 3 bits. A shift and scale based on-chip decoding hardware is proposed which can decode these 3-bit representations to recover approximate filter values. The size of the DNN model is reduced this way and can be sent over a communication channel to be decoded on the edge computing devices. This way power is reduced by limiting data bits by approximation. In the second component we propose a quality scalable multiplier which reduces the number of partial products by converting numbers in canonic sign digit representations and further approximating the number by reducing least significant bits. These quantized CNNs provide almost same ac-curacy as network with original weights with little or no fine-tuning. The hardware for the adaptive multipliers utilize gate clocking for reducing energy consumption during multiplications. The proposed methodology greatly reduces the memory and power requirements of DNN models making it a feasible approach to deploy Deep Learning on edge computing. The experiments done on LeNet and ConvNets show an increase upto 6% of zeros and memory savings upto 82.4919% while keeping the accuracy near the state of the art.

Read more7/17/2024

0

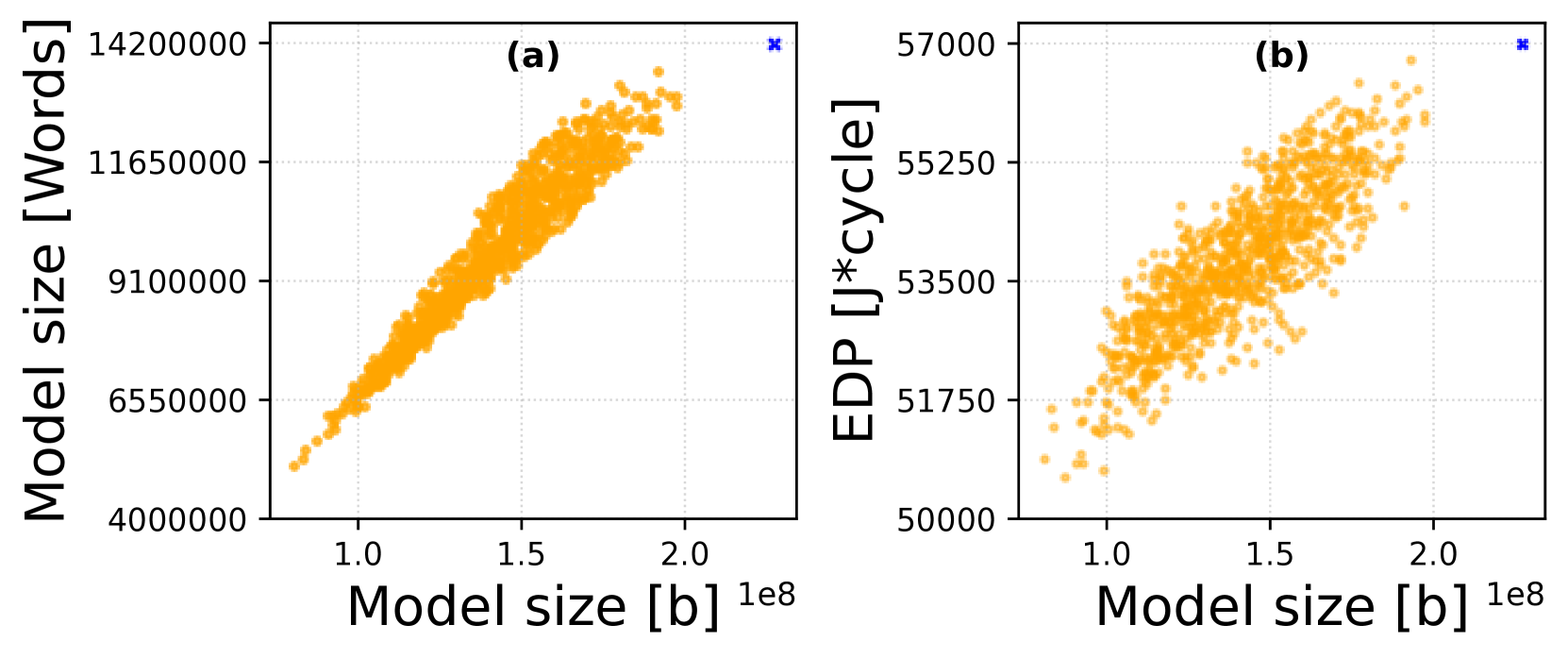

Exploring Quantization and Mapping Synergy in Hardware-Aware Deep Neural Network Accelerators

Jan Klhufek, Miroslav Safar, Vojtech Mrazek, Zdenek Vasicek, Lukas Sekanina

Energy efficiency and memory footprint of a convolutional neural network (CNN) implemented on a CNN inference accelerator depend on many factors, including a weight quantization strategy (i.e., data types and bit-widths) and mapping (i.e., placement and scheduling of DNN elementary operations on hardware units of the accelerator). We show that enabling rich mixed quantization schemes during the implementation can open a previously hidden space of mappings that utilize the hardware resources more effectively. CNNs utilizing quantized weights and activations and suitable mappings can significantly improve trade-offs among the accuracy, energy, and memory requirements compared to less carefully optimized CNN implementations. To find, analyze, and exploit these mappings, we: (i) extend a general-purpose state-of-the-art mapping tool (Timeloop) to support mixed quantization, which is not currently available; (ii) propose an efficient multi-objective optimization algorithm to find the most suitable bit-widths and mapping for each DNN layer executed on the accelerator; and (iii) conduct a detailed experimental evaluation to validate the proposed method. On two CNNs (MobileNetV1 and MobileNetV2) and two accelerators (Eyeriss and Simba) we show that for a given quality metric (such as the accuracy on ImageNet), energy savings are up to 37% without any accuracy drop.

Read more4/9/2024

0

Joint Pruning and Channel-wise Mixed-Precision Quantization for Efficient Deep Neural Networks

Beatrice Alessandra Motetti, Matteo Risso, Alessio Burrello, Enrico Macii, Massimo Poncino, Daniele Jahier Pagliari

The resource requirements of deep neural networks (DNNs) pose significant challenges to their deployment on edge devices. Common approaches to address this issue are pruning and mixed-precision quantization, which lead to latency and memory occupation improvements. These optimization techniques are usually applied independently. We propose a novel methodology to apply them jointly via a lightweight gradient-based search, and in a hardware-aware manner, greatly reducing the time required to generate Pareto-optimal DNNs in terms of accuracy versus cost (i.e., latency or memory). We test our approach on three edge-relevant benchmarks, namely CIFAR-10, Google Speech Commands, and Tiny ImageNet. When targeting the optimization of the memory footprint, we are able to achieve a size reduction of 47.50% and 69.54% at iso-accuracy with the baseline networks with all weights quantized at 8 and 2-bit, respectively. Our method surpasses a previous state-of-the-art approach with up to 56.17% size reduction at iso-accuracy. With respect to the sequential application of state-of-the-art pruning and mixed-precision optimizations, we obtain comparable or superior results, but with a significantly lowered training time. In addition, we show how well-tailored cost models can improve the cost versus accuracy trade-offs when targeting specific hardware for deployment.

Read more7/2/2024

🧠

0

On-Chip Hardware-Aware Quantization for Mixed Precision Neural Networks

Wei Huang, Haotong Qin, Yangdong Liu, Jingzhuo Liang, Yulun Zhang, Ying Li, Xianglong Liu

Low-bit quantization emerges as one of the most promising compression approaches for deploying deep neural networks on edge devices. Mixed-precision quantization leverages a mixture of bit-widths to unleash the accuracy and efficiency potential of quantized models. However, existing mixed-precision quantization methods rely on simulations in high-performance devices to achieve accuracy and efficiency trade-offs in immense search spaces. This leads to a non-negligible gap between the estimated efficiency metrics and the actual hardware that makes quantized models far away from the optimal accuracy and efficiency, and also causes the quantization process to rely on additional high-performance devices. In this paper, we propose an On-Chip Hardware-Aware Quantization (OHQ) framework, performing hardware-aware mixed-precision quantization on deployed edge devices to achieve accurate and efficient computing. Specifically, for efficiency metrics, we built an On-Chip Quantization Aware pipeline, which allows the quantization process to perceive the actual hardware efficiency of the quantization operator and avoid optimization errors caused by inaccurate simulation. For accuracy metrics, we propose Mask-Guided Quantization Estimation technology to effectively estimate the accuracy impact of operators in the on-chip scenario, getting rid of the dependence of the quantization process on high computing power. By synthesizing insights from quantized models and hardware through linear optimization, we can obtain optimized bit-width configurations to achieve outstanding performance on accuracy and efficiency. We evaluate inference accuracy and acceleration with quantization for various architectures and compression ratios on hardware. OHQ achieves 70% and 73% accuracy for ResNet-18 and MobileNetV3, respectively, and can reduce latency by 15~30% compared to INT8 on real deployment.

Read more5/24/2024