SPICED: Syntactical Bug and Trojan Pattern Identification in A/MS Circuits using LLM-Enhanced Detection

0

Sign in to get full access

Overview

- This paper presents SPICED, a method for identifying syntactical bugs and trojan patterns in analog/mixed-signal (A/MS) circuits using large language models (LLMs).

- SPICED leverages LLMs to enhance the detection of these issues, improving upon traditional approaches.

- The authors demonstrate the effectiveness of SPICED on various A/MS circuit designs, showcasing its ability to outperform existing techniques.

Plain English Explanation

The paper introduces a new technique called SPICED that uses powerful language models to help identify two common problems in analog and mixed-signal circuit designs: syntactical bugs and trojan patterns.

Syntactical bugs are errors in the way the circuit is constructed, similar to how a computer program might have a bug in its code. These can be hard to catch, especially in complex analog circuits.

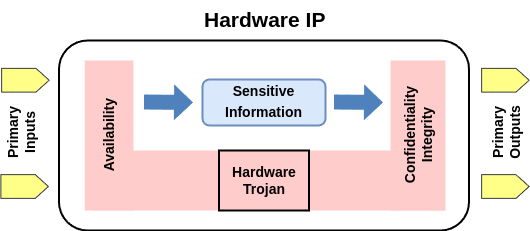

Trojan patterns are sneaky vulnerabilities that bad actors could try to hide in a circuit, kind of like a hidden backdoor. These can be even trickier to detect.

The researchers developed SPICED to address these challenges. SPICED leverages the impressive language understanding capabilities of large language models (LLMs) - the same type of AI models that power advanced chatbots and text generation. By training SPICED on lots of example circuits, the language model learns to recognize patterns that indicate bugs or trojan patterns.

The paper shows that SPICED is more effective at finding these issues compared to traditional approaches. This could help circuit designers build more robust and secure analog/mixed-signal systems, which are used in many critical applications like sensors, medical devices, and telecommunications.

Technical Explanation

The core idea behind SPICED is to use the powerful language modeling capabilities of LLMs to detect syntactical bugs and trojan patterns in A/MS circuits. The authors hypothesize that LLMs can learn the "syntax" of valid circuit designs and use this knowledge to identify anomalies.

The SPICED workflow involves three key steps:

-

Circuit Preprocessing: The A/MS circuit design is converted into a structured textual representation that can be processed by the LLM.

-

LLM-Enhanced Detection: A pre-trained LLM is fine-tuned on a dataset of preprocessed circuits, some of which contain known bugs or trojan patterns. This allows the LLM to learn the "grammar" of valid circuit designs.

-

Anomaly Identification: The fine-tuned LLM is used to evaluate new circuit designs, flagging any that deviate from the learned patterns as potential issues.

The authors evaluate SPICED on a range of A/MS circuit benchmarks, comparing its performance to traditional rule-based and machine learning approaches. The results demonstrate that SPICED can identify a higher percentage of bugs and trojan patterns while maintaining a lower false positive rate.

Critical Analysis

The SPICED approach represents a promising step forward in leveraging LLMs for circuit design verification. By focusing on the syntactical structure of circuits, the authors have identified a novel application of language modeling that complements existing techniques.

However, the paper does not address some potential limitations:

- The effectiveness of SPICED may be dependent on the quality and representativeness of the training data. Rare or novel bug/trojan patterns may not be well-captured by the LLM.

- The authors do not provide details on the computational cost and scalability of the SPICED workflow, which could be a concern for large, complex circuits.

- While SPICED can identify anomalies, further analysis may be required to determine whether a flagged issue is a genuine bug or trojan pattern.

Additional research could explore ways to address these limitations, such as incorporating active learning techniques to expand the training data or developing methods to explain the LLM's anomaly detection decisions.

Conclusion

The SPICED framework demonstrates the potential of leveraging LLMs for enhanced circuit design verification. By modeling the syntactical structure of A/MS circuits, SPICED can identify a broader range of bugs and trojan patterns compared to traditional approaches.

This work highlights the growing importance of AI-powered tools in the design and development of complex analog and mixed-signal systems, which are critical components in many cutting-edge technologies. As LLMs continue to advance, there may be further opportunities to apply their language understanding capabilities to other challenging problems in circuit design and beyond.

This summary was produced with help from an AI and may contain inaccuracies - check out the links to read the original source documents!

Related Papers

0

SPICED: Syntactical Bug and Trojan Pattern Identification in A/MS Circuits using LLM-Enhanced Detection

Jayeeta Chaudhuri, Dhruv Thapar, Arjun Chaudhuri, Farshad Firouzi, Krishnendu Chakrabarty

Analog and mixed-signal (A/MS) integrated circuits (ICs) are crucial in modern electronics, playing key roles in signal processing, amplification, sensing, and power management. Many IC companies outsource manufacturing to third-party foundries, creating security risks such as stealthy analog Trojans. Traditional detection methods, including embedding circuit watermarks or conducting hardware-based monitoring, often impose significant area and power overheads, and may not effectively identify all types of Trojans. To address these shortcomings, we propose SPICED, a Large Language Model (LLM)-based framework that operates within the software domain, eliminating the need for hardware modifications for Trojan detection and localization. This is the first work using LLM-aided techniques for detecting and localizing syntactical bugs and analog Trojans in circuit netlists, requiring no explicit training and incurring zero area overhead. Our framework employs chain-of-thought reasoning and few-shot examples to teach anomaly detection rules to LLMs. With the proposed method, we achieve an average Trojan coverage of 93.32% and an average true positive rate of 93.4% in identifying Trojan-impacted nodes for the evaluated analog benchmark circuits. These experimental results validate the effectiveness of LLMs in detecting and locating both syntactical bugs and Trojans within analog netlists.

Read more8/30/2024

0

LaMAGIC: Language-Model-based Topology Generation for Analog Integrated Circuits

Chen-Chia Chang, Yikang Shen, Shaoze Fan, Jing Li, Shun Zhang, Ningyuan Cao, Yiran Chen, Xin Zhang

In the realm of electronic and electrical engineering, automation of analog circuit is increasingly vital given the complexity and customized requirements of modern applications. However, existing methods only develop search-based algorithms that require many simulation iterations to design a custom circuit topology, which is usually a time-consuming process. To this end, we introduce LaMAGIC, a pioneering language model-based topology generation model that leverages supervised finetuning for automated analog circuit design. LaMAGIC can efficiently generate an optimized circuit design from the custom specification in a single pass. Our approach involves a meticulous development and analysis of various input and output formulations for circuit. These formulations can ensure canonical representations of circuits and align with the autoregressive nature of LMs to effectively addressing the challenges of representing analog circuits as graphs. The experimental results show that LaMAGIC achieves a success rate of up to 96% under a strict tolerance of 0.01. We also examine the scalability and adaptability of LaMAGIC, specifically testing its performance on more complex circuits. Our findings reveal the enhanced effectiveness of our adjacency matrix-based circuit formulation with floating-point input, suggesting its suitability for handling intricate circuit designs. This research not only demonstrates the potential of language models in graph generation, but also builds a foundational framework for future explorations in automated analog circuit design.

Read more8/30/2024

0

An AI Architecture with the Capability to Classify and Explain Hardware Trojans

Paul Whitten, Francis Wolff, Chris Papachristou

Hardware trojan detection methods, based on machine learning (ML) techniques, mainly identify suspected circuits but lack the ability to explain how the decision was arrived at. An explainable methodology and architecture is introduced based on the existing hardware trojan detection features. Results are provided for explaining digital hardware trojans within a netlist using trust-hub trojan benchmarks.

Read more7/8/2024

0

LLMPot: Automated LLM-based Industrial Protocol and Physical Process Emulation for ICS Honeypots

Christoforos Vasilatos, Dunia J. Mahboobeh, Hithem Lamri, Manaar Alam, Michail Maniatakos

Industrial Control Systems (ICS) are extensively used in critical infrastructures ensuring efficient, reliable, and continuous operations. However, their increasing connectivity and addition of advanced features make them vulnerable to cyber threats, potentially leading to severe disruptions in essential services. In this context, honeypots play a vital role by acting as decoy targets within ICS networks, or on the Internet, helping to detect, log, analyze, and develop mitigations for ICS-specific cyber threats. Deploying ICS honeypots, however, is challenging due to the necessity of accurately replicating industrial protocols and device characteristics, a crucial requirement for effectively mimicking the unique operational behavior of different industrial systems. Moreover, this challenge is compounded by the significant manual effort required in also mimicking the control logic the PLC would execute, in order to capture attacker traffic aiming to disrupt critical infrastructure operations. In this paper, we propose LLMPot, a novel approach for designing honeypots in ICS networks harnessing the potency of Large Language Models (LLMs). LLMPot aims to automate and optimize the creation of realistic honeypots with vendor-agnostic configurations, and for any control logic, aiming to eliminate the manual effort and specialized knowledge traditionally required in this domain. We conducted extensive experiments focusing on a wide array of parameters, demonstrating that our LLM-based approach can effectively create honeypot devices implementing different industrial protocols and diverse control logic.

Read more5/13/2024