TeraPool-SDR: An 1.89TOPS 1024 RV-Cores 4MiB Shared-L1 Cluster for Next-Generation Open-Source Software-Defined Radios

0

Sign in to get full access

Overview

- TeraPool-SDR: A high-performance, energy-efficient, and scalable hardware platform for next-generation open-source software-defined radios

- Features 1.89 TOPS of AI performance, 1024 RISC-V cores, and a 4 MiB shared L1 cache

- Designed to enable advanced wireless communication applications and Terahertz communication testbeds

Plain English Explanation

The TeraPool-SDR is a powerful hardware platform designed to power the next generation of open-source software-defined radios. It packs an impressive 1.89 TOPS of AI performance, achieved through a cluster of 1,024 RISC-V cores that share a 4 MiB L1 cache.

This high-performance, energy-efficient design is aimed at enabling advanced wireless communication applications, such as Terahertz communication testbeds. By leveraging the scalability and flexibility of the RISC-V architecture, the TeraPool-SDR can be tailored to the specific needs of different software-defined radio use cases.

The shared L1 cache is a key feature that helps improve overall system performance and efficiency. This energy-efficient last-level cache memory design allows the 1,024 cores to quickly access and share data, reducing the need for costly off-chip memory accesses.

Technical Explanation

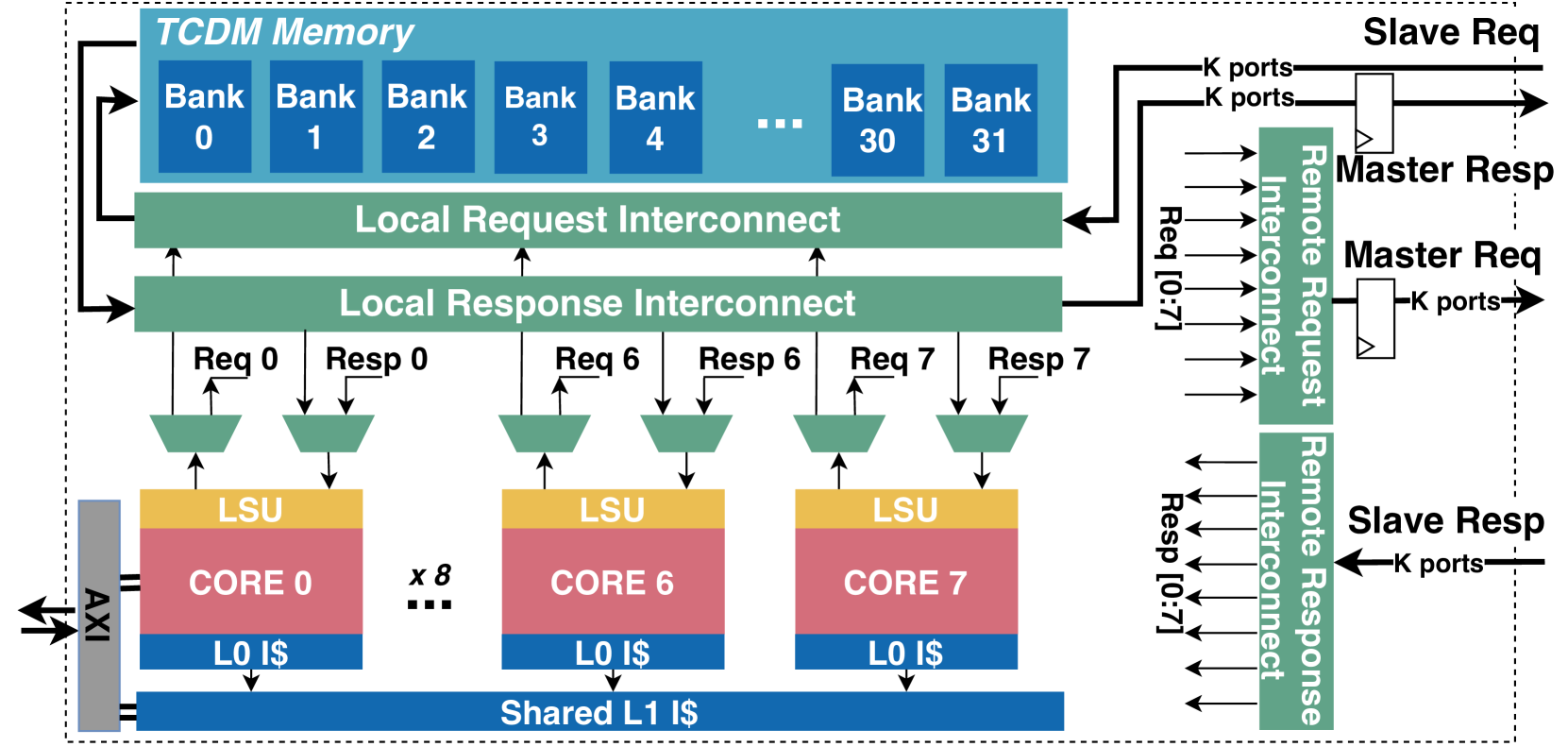

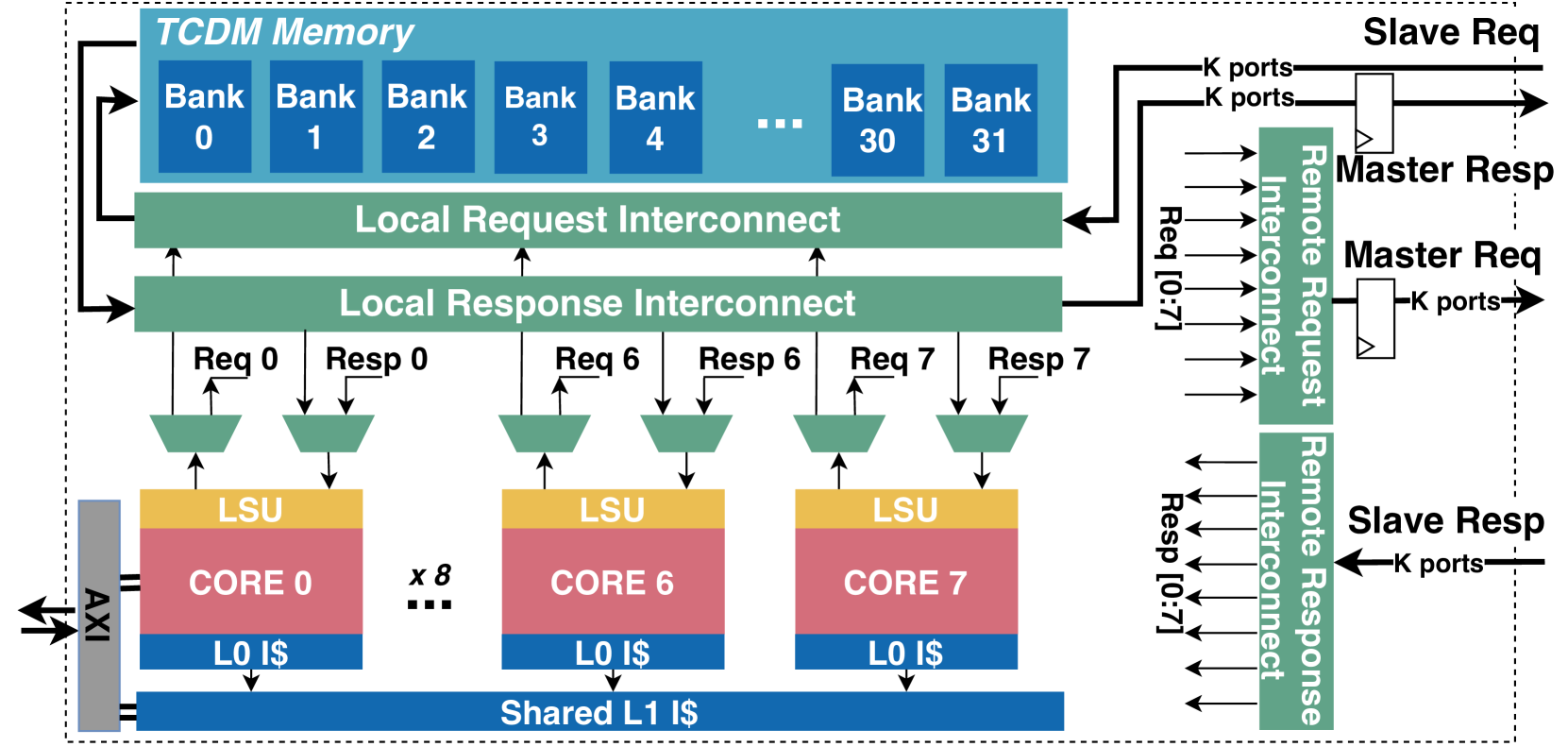

The TeraPool-SDR architecture is built around a cluster of 1,024 RISC-V cores, each with their own private instruction and data caches. These cores are connected to a 4 MiB shared L1 cache, which serves as a high-bandwidth, low-latency data repository for the entire system.

The shared L1 cache is designed to minimize off-chip memory accesses, which can be energy-intensive and impact overall system performance. By allowing the cores to efficiently share data, the TeraPool-SDR can achieve significant performance and energy-efficiency gains, especially for applications that exhibit high data reuse, such as traffic analysis and classification or hardware support for atomic-free asynchronous operations.

The RISC-V architecture provides the TeraPool-SDR with a high degree of flexibility and scalability. The modular design of the RISC-V instruction set allows the system to be tailored to specific software-defined radio applications, leveraging only the necessary hardware features and instructions.

Critical Analysis

The TeraPool-SDR represents a significant advancement in hardware platforms for open-source software-defined radios, but there are a few potential limitations and areas for further research:

-

Power Consumption: While the energy-efficient design of the shared L1 cache and RISC-V cores should help minimize power consumption, the overall power profile of the system with 1,024 cores under load may still be a concern for certain mobile or embedded applications.

-

Programmability and Toolchain: The success of the TeraPool-SDR will ultimately depend on the availability of a robust software ecosystem and development tools that can effectively leverage the RISC-V architecture and the system's unique hardware features.

-

Scalability and Testability: As the number of cores and the complexity of the hardware platform increases, challenges around system-level integration, testing, and verification may arise, which could impact the overall reliability and scalability of the TeraPool-SDR.

Despite these potential limitations, the TeraPool-SDR represents a promising step forward in the development of high-performance, energy-efficient hardware platforms for next-generation open-source software-defined radios and advanced wireless communication applications.

Conclusion

The TeraPool-SDR is a cutting-edge hardware platform that offers impressive performance and energy efficiency for open-source software-defined radio applications. By leveraging the scalability and flexibility of the RISC-V architecture, along with a innovative shared L1 cache design, the TeraPool-SDR has the potential to enable a new wave of advanced wireless communication technologies, including Terahertz communication testbeds and open RAN digital twins.

As the field of software-defined radios continues to evolve, the TeraPool-SDR represents a significant step forward in providing the high-performance, energy-efficient hardware needed to power the next generation of wireless communication systems.

This summary was produced with help from an AI and may contain inaccuracies - check out the links to read the original source documents!

Related Papers

0

TeraPool-SDR: An 1.89TOPS 1024 RV-Cores 4MiB Shared-L1 Cluster for Next-Generation Open-Source Software-Defined Radios

Yichao Zhang, Marco Bertuletti, Samuel Riedel, Matheus Cavalcante, Alessandro Vanelli-Coralli, Luca Benini

Radio Access Networks (RAN) workloads are rapidly scaling up in data processing intensity and throughput as the 5G (and beyond) standards grow in number of antennas and sub-carriers. Offering flexible Processing Elements (PEs), efficient memory access, and a productive parallel programming model, many-core clusters are a well-matched architecture for next-generation software-defined RANs, but staggering performance requirements demand a high number of PEs coupled with extreme Power, Performance and Area (PPA) efficiency. We present the architecture, design, and full physical implementation of Terapool-SDR, a cluster for Software Defined Radio (SDR) with 1024 latency-tolerant, compact RV32 PEs, sharing a global view of a 4MiB, 4096-banked, L1 memory. We report various feasible configurations of TeraPool-SDR featuring an ultra-high bandwidth PE-to-L1-memory interconnect, clocked at 730MHz, 880MHz, and 924MHz (TT/0.80 V/25 {deg}C) in 12nm FinFET technology. The TeraPool-SDR cluster achieves high energy efficiency on all SDR key kernels for 5G RANs: Fast Fourier Transform (93GOPS/W), Matrix-Multiplication (125GOPS/W), Channel Estimation (96GOPS/W), and Linear System Inversion (61GOPS/W). For all the kernels, it consumes less than 10W, in compliance with industry standards.

Read more5/9/2024

0

A 1024 RV-Cores Shared-L1 Cluster with High Bandwidth Memory Link for Low-Latency 6G-SDR

Yichao Zhang, Marco Bertuletti, Chi Zhang, Samuel Riedel, Alessandro Vanelli-Coralli, Luca Benini

We introduce an open-source architecture for next-generation Radio-Access Network baseband processing: 1024 latency-tolerant 32-bit RISC-V cores share 4 MiB of L1 memory via an ultra-low latency interconnect (7-11 cycles), a modular Direct Memory Access engine provides an efficient link to a high bandwidth memory, such as HBM2E (98% peak bandwidth at 910GBps). The system achieves leading-edge energy efficiency at sub-ms latency in key 6G baseband processing kernels: Fast Fourier Transform (93 GOPS/W), Beamforming (125 GOPS/W), Channel Estimation (96 GOPS/W), and Linear System Inversion (61 GOPS/W), with only 9% data movement overhead.

Read more8/20/2024

🏅

0

Terahertz Communication Testbeds: Challenges and Opportunities

Eray Guven, Gunes Karabulut Kurt

This study investigates an experimental software defined radio (SDR) implementation on 180 GHz. Rate scarcity and frequency sparsity are discussed as hardware bottlenecks. Experimental challenges are explained along with the derived system model of such a cascaded structure. Multiple error metrics for the terahertz (THz) signal are acquired, and various case scenarios are subsequently compared. The SDR-THz testbed reaches 3.2 Mbps with < 1 degree skew error. The use of a reflector plate can fine-tune the frequency error and gain imbalance in the expense of at least 14.91 dB signal-to-noise ratio. The results demonstrate the complete feasibility of SDR-based baseband signal generation in THz communication, revealing abundant opportunities to overcome hardware limitations in experimental research.

Read more4/1/2024

🤔

0

A Flexible Cryptographic Infrastructure for High-security SDR-based Systems

Peter Hillmann, Bjorn Stelte

Military software defined radio (SDR) systems are a major factor in future network-centric operations due to their flexibility and support for more capable radio communications systems. The inherent nature of software-based systems requires a more complex auxiliary infrastructure and multiple independent levels of security compared with typical systems: Secure booting of the SDR device, cryptographically signed software, real time operating platform software as well as radio applications. This technology raises new challenges with respect to the management. The largest impact on SDR deployments is due to the auxiliary cryptographic infrastructure for the security of the software life cycle and the cyclic update of the keys. Compared to conventional radio devices, the SDR system with the cryptographic infrastructure described in this paper reaches a higher security level and is more flexible. The advantage is the possibility to deploy trunked radio system and further waveforms, such as coalition wideband, which will be standardized in the future. Also it is possible to update cryptographic mechanisms. In this work, we analyze the requirements for a high secure SDR deployment and model the life cycle of the components of a deployed SDR node based on the Joint Program Executive Office (JPEO) Software Communication Architecture (SCA).

Read more6/26/2024