AMSNet: Netlist Dataset for AMS Circuits

0

Sign in to get full access

Overview

- This paper introduces AMSNet, a netlist dataset for analog and mixed-signal (AMS) circuits.

- The dataset is intended to support the development of machine learning models for AMS circuit design and optimization.

- The dataset includes circuit netlists, circuit parameters, and performance metrics for a variety of AMS circuit topologies.

Plain English Explanation

The paper presents a new dataset called AMSNet that contains information about different types of analog and mixed-signal (AMS) electronic circuits. These are circuits that combine analog and digital components, which are commonly used in a wide range of electronic devices.

The goal of creating this dataset is to help researchers and engineers develop new machine learning models that can be used to design and optimize AMS circuits more efficiently. The dataset includes the detailed technical specifications, or "netlists," for many different AMS circuit topologies, as well as the key parameters and performance metrics for each circuit.

By providing this comprehensive dataset, the authors hope to enable the broader adoption of machine learning techniques in the field of AMS circuit design, which has traditionally relied more on manual, experience-based approaches. This could lead to significant improvements in the speed and quality of AMS circuit design, benefiting the development of a wide range of electronic products.

Technical Explanation

The AMSNet dataset contains detailed information about the structure and performance of a variety of AMS circuit topologies, including amplifiers, filters, and oscillators. The dataset includes the circuit netlists, which define the interconnections between the electronic components, as well as the values of the component parameters and the measured circuit performance metrics.

To create the dataset, the authors used a combination of circuit simulation, measurement, and manual curation to gather data on over 10,000 unique AMS circuit instances. The circuits span a range of design complexities and performance characteristics, providing a diverse set of examples for machine learning models to learn from.

The authors envision AMSNet being used to train and evaluate new machine learning models for tasks such as circuit topology optimization, parameter estimation, and performance prediction. By providing a standardized, high-quality dataset, the authors hope to accelerate the adoption of machine learning techniques in the AMS circuit design domain, which has traditionally relied more on manual, experience-based approaches.

Critical Analysis

The AMSNet dataset represents a significant step forward in enabling the use of machine learning for AMS circuit design. By providing a large, diverse, and well-curated dataset, the authors have lowered a major barrier to entry for researchers and engineers looking to apply data-driven techniques in this field.

However, the authors acknowledge several limitations of the current dataset. For example, the circuits included in AMSNet are primarily academic or proof-of-concept designs, and may not fully capture the complexity and constraints of real-world industrial AMS circuits. Additionally, the dataset does not include information on the manufacturing processes or environmental conditions that can also significantly impact AMS circuit performance.

Future work could address these limitations by expanding the dataset to include more industrial-scale AMS circuits and incorporating additional sources of variability and uncertainty. Integrating AMSNet with other datasets, such as those focused on digital ASIC design or analog circuit optimization, could also unlock new opportunities for cross-domain learning and optimization.

Conclusion

The AMSNet dataset represents a valuable resource for advancing the state of the art in AMS circuit design through the use of machine learning. By providing a diverse and well-curated collection of AMS circuit data, the authors have laid the groundwork for researchers and engineers to develop more efficient and effective AMS design tools and methodologies.

As the field of AMS circuit design continues to evolve, the AMSNet dataset and the machine learning models trained on it could play a crucial role in enabling the design of more complex, high-performance, and reliable AMS systems, ultimately benefiting a wide range of electronic applications.

This summary was produced with help from an AI and may contain inaccuracies - check out the links to read the original source documents!

Related Papers

0

AMSNet: Netlist Dataset for AMS Circuits

Zhuofu Tao, Yichen Shi, Yiru Huo, Rui Ye, Zonghang Li, Li Huang, Chen Wu, Na Bai, Zhiping Yu, Ting-Jung Lin, Lei He

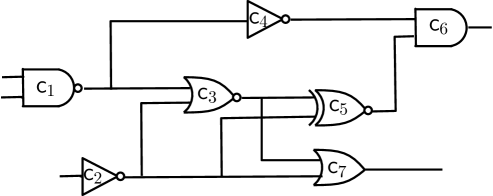

Today's analog/mixed-signal (AMS) integrated circuit (IC) designs demand substantial manual intervention. The advent of multimodal large language models (MLLMs) has unveiled significant potential across various fields, suggesting their applicability in streamlining large-scale AMS IC design as well. A bottleneck in employing MLLMs for automatic AMS circuit generation is the absence of a comprehensive dataset delineating the schematic-netlist relationship. We therefore design an automatic technique for converting schematics into netlists, and create dataset AMSNet, encompassing transistor-level schematics and corresponding SPICE format netlists. With a growing size, AMSNet can significantly facilitate exploration of MLLM applications in AMS circuit design. We have made an initial set of netlists public, and will make both our netlist generation tool and the full dataset available upon publishing of this paper.

Read more5/16/2024

👀

0

AICircuit: A Multi-Level Dataset and Benchmark for AI-Driven Analog Integrated Circuit Design

Asal Mehradfar, Xuzhe Zhao, Yue Niu, Sara Babakniya, Mahdi Alesheikh, Hamidreza Aghasi, Salman Avestimehr

Analog and radio-frequency circuit design requires extensive exploration of both circuit topology and parameters to meet specific design criteria like power consumption and bandwidth. Designers must review state-of-the-art topology configurations in the literature and sweep various circuit parameters within each configuration. This design process is highly specialized and time-intensive, particularly as the number of circuit parameters increases and the circuit becomes more complex. Prior research has explored the potential of machine learning to enhance circuit design procedures. However, these studies primarily focus on simple circuits, overlooking the more practical and complex analog and radio-frequency systems. A major obstacle for bearing the power of machine learning in circuit design is the availability of a generic and diverse dataset, along with robust metrics, which are essential for thoroughly evaluating and improving machine learning algorithms in the analog and radio-frequency circuit domain. We present AICircuit, a comprehensive multi-level dataset and benchmark for developing and evaluating ML algorithms in analog and radio-frequency circuit design. AICircuit comprises seven commonly used basic circuits and two complex wireless transceiver systems composed of multiple circuit blocks, encompassing a wide array of design scenarios encountered in real-world applications. We extensively evaluate various ML algorithms on the dataset, revealing the potential of ML algorithms in learning the mapping from the design specifications to the desired circuit parameters.

Read more7/29/2024

🛸

0

Interactive and Automatic Generation of Primitive Custom Circuit Layout Using LLMs

Geunyoung You, Youjin Byun, Sojin Lim, Jaeduk Han

In this study, we investigate the use of Large Language Models (LLMs) for the interactive and automated production of customs circuit layouts described in natural language. Our proposed layout automation process leverages a template-and-grid-based layout generation framework to create process-portable layout generators tailored for various custom circuits, including standard cells and high-speed mixed-signal circuits. However, rather than directly describing the layout generators in traditional programming language, we utilize natural language using LLMs to make the layout generation process more intuitive and efficient. This approach also supports interactive modifications of the layout generator code, enhancing customization capabilities. We demonstrate the effectiveness of our LLM-based layout generation method across several custom circuit examples, such as logic standard cells, a serializer and a strong arm latch, including their completeness in terms of Design Rule Check (DRC), Layout Versus Schematic (LVS) test, and post-layout performance for high-speed circuits. Our experimental results indicate that LLMs can generate a diverse range of circuit layouts with substantial customization options.

Read more8/15/2024

0

DE-HNN: An effective neural model for Circuit Netlist representation

Zhishang Luo, Truong Son Hy, Puoya Tabaghi, Donghyeon Koh, Michael Defferrard, Elahe Rezaei, Ryan Carey, Rhett Davis, Rajeev Jain, Yusu Wang

The run-time for optimization tools used in chip design has grown with the complexity of designs to the point where it can take several days to go through one design cycle which has become a bottleneck. Designers want fast tools that can quickly give feedback on a design. Using the input and output data of the tools from past designs, one can attempt to build a machine learning model that predicts the outcome of a design in significantly shorter time than running the tool. The accuracy of such models is affected by the representation of the design data, which is usually a netlist that describes the elements of the digital circuit and how they are connected. Graph representations for the netlist together with graph neural networks have been investigated for such models. However, the characteristics of netlists pose several challenges for existing graph learning frameworks, due to the large number of nodes and the importance of long-range interactions between nodes. To address these challenges, we represent the netlist as a directed hypergraph and propose a Directional Equivariant Hypergraph Neural Network (DE-HNN) for the effective learning of (directed) hypergraphs. Theoretically, we show that our DE-HNN can universally approximate any node or hyperedge based function that satisfies certain permutation equivariant and invariant properties natural for directed hypergraphs. We compare the proposed DE-HNN with several State-of-the-art (SOTA) machine learning models for (hyper)graphs and netlists, and show that the DE-HNN significantly outperforms them in predicting the outcome of optimized place-and-route tools directly from the input netlists. Our source code and the netlists data used are publicly available at https://github.com/YusuLab/chips.git

Read more4/17/2024