DE-HNN: An effective neural model for Circuit Netlist representation

2404.00477

0

0

Abstract

The run-time for optimization tools used in chip design has grown with the complexity of designs to the point where it can take several days to go through one design cycle which has become a bottleneck. Designers want fast tools that can quickly give feedback on a design. Using the input and output data of the tools from past designs, one can attempt to build a machine learning model that predicts the outcome of a design in significantly shorter time than running the tool. The accuracy of such models is affected by the representation of the design data, which is usually a netlist that describes the elements of the digital circuit and how they are connected. Graph representations for the netlist together with graph neural networks have been investigated for such models. However, the characteristics of netlists pose several challenges for existing graph learning frameworks, due to the large number of nodes and the importance of long-range interactions between nodes. To address these challenges, we represent the netlist as a directed hypergraph and propose a Directional Equivariant Hypergraph Neural Network (DE-HNN) for the effective learning of (directed) hypergraphs. Theoretically, we show that our DE-HNN can universally approximate any node or hyperedge based function that satisfies certain permutation equivariant and invariant properties natural for directed hypergraphs. We compare the proposed DE-HNN with several State-of-the-art (SOTA) machine learning models for (hyper)graphs and netlists, and show that the DE-HNN significantly outperforms them in predicting the outcome of optimized place-and-route tools directly from the input netlists. Our source code and the netlists data used are publicly available at https://github.com/YusuLab/chips.git

Get summaries of the top AI research delivered straight to your inbox:

Overview

- This paper proposes a neural network called DE-HNN (Directed Hypergraph Neural Network) for modeling and analyzing circuit netlists represented as directed hypergraphs.

- DE-HNN aims to capture the complex relationships between circuit components and their interactions, which can be challenging to represent using traditional graph neural networks.

- The paper demonstrates the effectiveness of DE-HNN on various circuit analysis tasks, including power grid analysis, analog circuit design, and mesh-based geometry processing.

Plain English Explanation

Electrical circuits are often represented as netlists, which are like a list of all the components and how they are connected. However, traditional graph-based approaches may not be able to fully capture the complex relationships between these components.

The researchers developed a new type of neural network called DE-HNN that can better model these circuit netlists. DE-HNN: a neural network for modeling circuit netlists as directed hypergraphs

DE-HNN treats the circuit netlist like a special kind of graph, called a directed hypergraph. In a regular graph, you have nodes (like circuit components) and edges (like wires) connecting them. But in a hypergraph, a single "hyperedge" can connect multiple nodes at once, which is a better way to represent the complicated connections in a circuit.

By using this hypergraph representation and a specialized neural network, DE-HNN can capture the complex interactions between different parts of the circuit. This allows it to be useful for a variety of circuit analysis tasks, like power grid analysis, analog circuit design, and even mesh-based geometry processing.

Overall, DE-HNN provides a new way to model and analyze the intricate connections in electrical circuits, which could lead to improvements in circuit design, optimization, and analysis.

Technical Explanation

The key idea behind DE-HNN is to represent circuit netlists as directed hypergraphs, which can more faithfully capture the complex relationships between circuit components compared to traditional graph-based approaches. Modeling netlists as directed hypergraphs

In a directed hypergraph, a "hyperedge" can connect multiple nodes (circuit components) at once, unlike a regular graph where edges only connect two nodes. This allows DE-HNN to model the intricate connections and interactions between different parts of the circuit.

The DE-HNN architecture consists of several key components:

- A hypergraph encoder that learns representations of the nodes and hyperedges in the circuit netlist.

- A hyperedge interaction module that models the interactions between different hyperedges, capturing the higher-order dependencies in the circuit.

- A task-specific decoder that uses the learned representations to perform various circuit analysis tasks, such as power grid analysis, analog circuit design, and mesh-based geometry processing.

The researchers evaluate DE-HNN on a range of benchmark datasets and show that it outperforms traditional graph neural networks and other hypergraph neural network models across multiple circuit analysis tasks. This demonstrates the effectiveness of the directed hypergraph representation and the DE-HNN architecture in capturing the complex relationships in circuit netlists.

Critical Analysis

The paper provides a compelling approach for modeling and analyzing circuit netlists using DE-HNN, a directed hypergraph neural network. The key strengths of this work include:

- The ability to capture the complex, higher-order dependencies in circuit netlists through the use of directed hypergraphs, which traditional graph-based methods may struggle with.

- The versatility of the DE-HNN architecture, which can be applied to a variety of circuit analysis tasks, as demonstrated by the experiments.

- The strong empirical performance of DE-HNN compared to other state-of-the-art methods, showcasing the practical benefits of this approach.

However, the paper also acknowledges some limitations and areas for further research:

- The computational complexity of the hypergraph encoding and interaction modules, which could limit the scalability of DE-HNN to very large circuits.

- The dependence on the quality of the initial node and hyperedge features, which may require careful feature engineering or preprocessing.

- The potential need for further investigation into the interpretability and explainability of the DE-HNN model, to better understand the learned representations and their connection to the underlying circuit structure.

Overall, the DE-HNN approach represents an important step forward in the field of circuit analysis and modeling, and the authors have identified relevant areas for future work to address the current limitations and further enhance the capabilities of this neural network model.

Conclusion

The DE-HNN paper presents a novel neural network architecture for modeling and analyzing circuit netlists represented as directed hypergraphs. By capturing the complex, higher-order relationships between circuit components, DE-HNN demonstrates superior performance on a range of circuit analysis tasks compared to traditional graph-based methods.

The ability to effectively model circuit netlists using DE-HNN has far-reaching implications for the design, optimization, and understanding of electrical circuits and systems. This work could potentially lead to advancements in power grid analysis, analog circuit design, and even broader applications in mesh-based geometry processing.

While the paper acknowledges some computational and interpretability challenges that warrant further research, the overall contribution of DE-HNN represents a significant step forward in the field of circuit analysis and provides a promising foundation for future developments in this area.

This summary was produced with help from an AI and may contain inaccuracies - check out the links to read the original source documents!

Related Papers

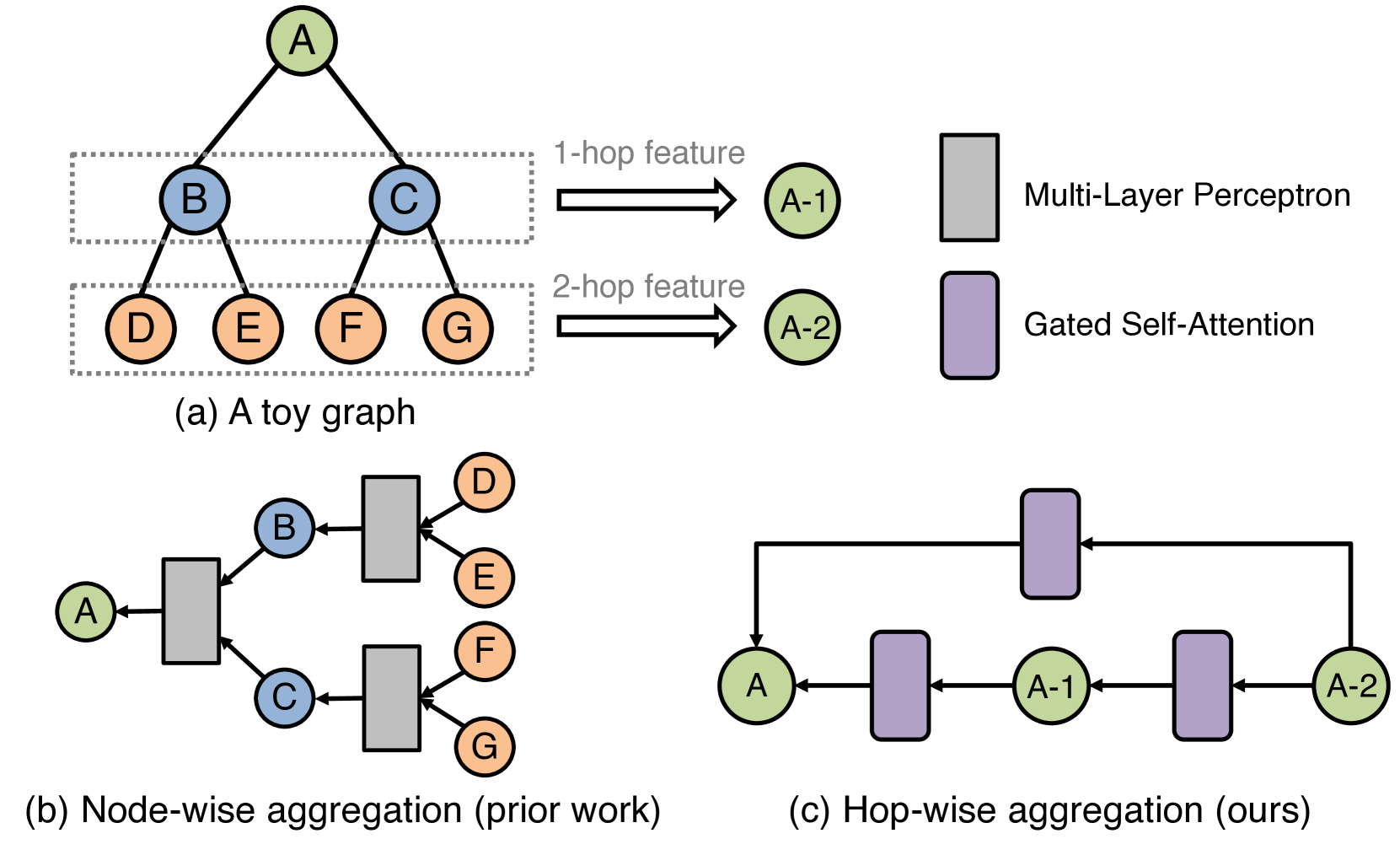

Less is More: Hop-Wise Graph Attention for Scalable and Generalizable Learning on Circuits

Chenhui Deng, Zichao Yue, Cunxi Yu, Gokce Sarar, Ryan Carey, Rajeev Jain, Zhiru Zhang

0

0

While graph neural networks (GNNs) have gained popularity for learning circuit representations in various electronic design automation (EDA) tasks, they face challenges in scalability when applied to large graphs and exhibit limited generalizability to new designs. These limitations make them less practical for addressing large-scale, complex circuit problems. In this work we propose HOGA, a novel attention-based model for learning circuit representations in a scalable and generalizable manner. HOGA first computes hop-wise features per node prior to model training. Subsequently, the hop-wise features are solely used to produce node representations through a gated self-attention module, which adaptively learns important features among different hops without involving the graph topology. As a result, HOGA is adaptive to various structures across different circuits and can be efficiently trained in a distributed manner. To demonstrate the efficacy of HOGA, we consider two representative EDA tasks: quality of results (QoR) prediction and functional reasoning. Our experimental results indicate that (1) HOGA reduces estimation error over conventional GNNs by 46.76% for predicting QoR after logic synthesis; (2) HOGA improves 10.0% reasoning accuracy over GNNs for identifying functional blocks on unseen gate-level netlists after complex technology mapping; (3) The training time for HOGA almost linearly decreases with an increase in computing resources.

4/12/2024

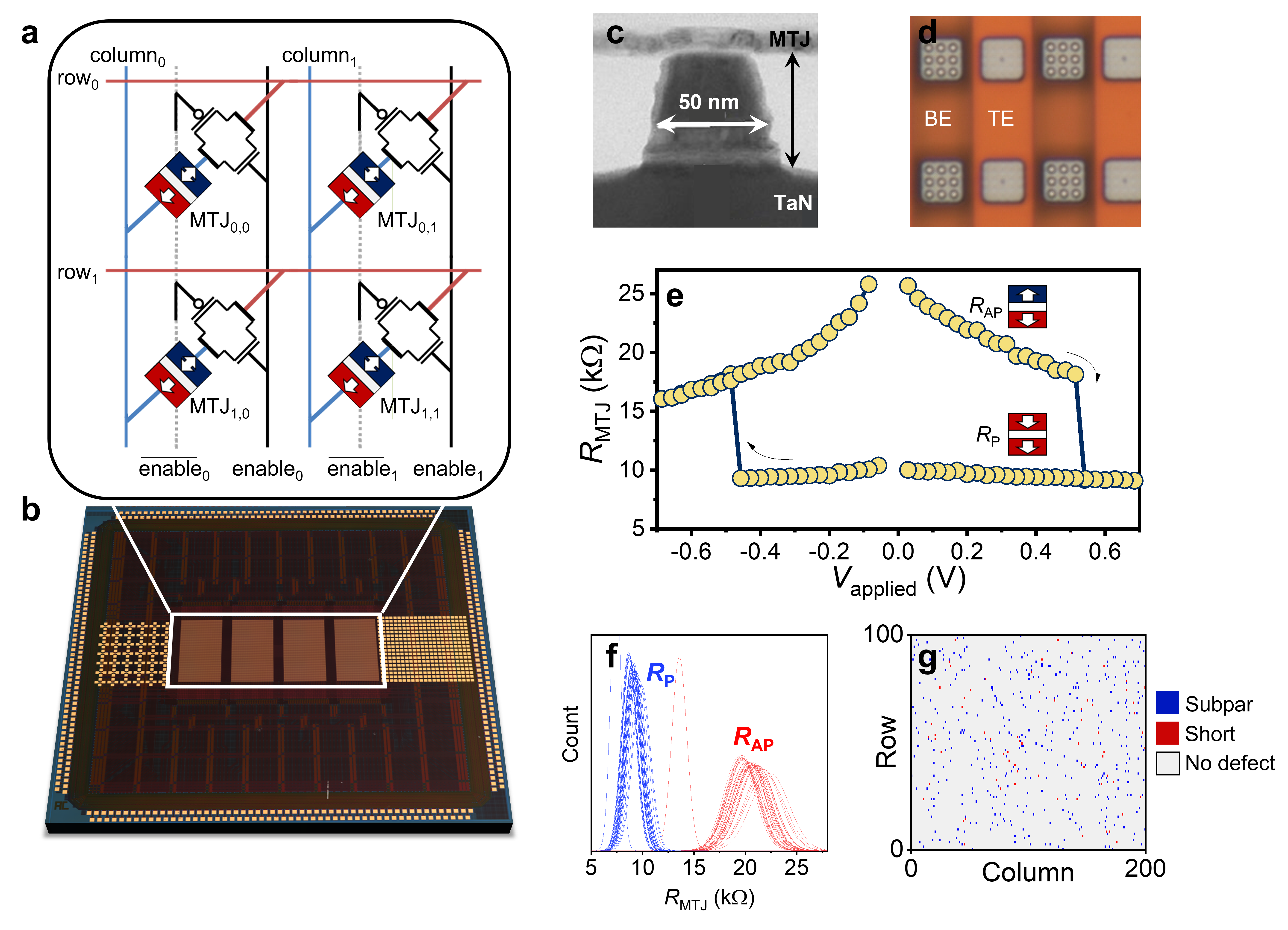

Measurement-driven neural-network training for integrated magnetic tunnel junction arrays

William A. Borders, Advait Madhavan, Matthew W. Daniels, Vasileia Georgiou, Martin Lueker-Boden, Tiffany S. Santos, Patrick M. Braganca, Mark D. Stiles, Jabez J. McClelland, Brian D. Hoskins

0

0

The increasing scale of neural networks needed to support more complex applications has led to an increasing requirement for area- and energy-efficient hardware. One route to meeting the budget for these applications is to circumvent the von Neumann bottleneck by performing computation in or near memory. An inevitability of transferring neural networks onto hardware is that non-idealities such as device-to-device variations or poor device yield impact performance. Methods such as hardware-aware training, where substrate non-idealities are incorporated during network training, are one way to recover performance at the cost of solution generality. In this work, we demonstrate inference on hardware neural networks consisting of 20,000 magnetic tunnel junction arrays integrated on a complementary metal-oxide-semiconductor chips that closely resembles market-ready spin transfer-torque magnetoresistive random access memory technology. Using 36 dies, each containing a crossbar array with its own non-idealities, we show that even a small number of defects in physically mapped networks significantly degrades the performance of networks trained without defects and show that, at the cost of generality, hardware-aware training accounting for specific defects on each die can recover to comparable performance with ideal networks. We then demonstrate a robust training method that extends hardware-aware training to statistics-aware training, producing network weights that perform well on most defective dies regardless of their specific defect locations. When evaluated on the 36 physical dies, statistics-aware trained solutions can achieve a mean misclassification error on the MNIST dataset that differs from the software-baseline by only 2 %. This statistics-aware training method could be generalized to networks with many layers that are mapped to hardware suited for industry-ready applications.

5/15/2024

🧠

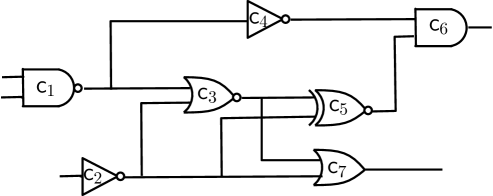

Nearest Neighbor Representations of Neural Circuits

Kordag Mehmet Kilic, Jin Sima, Jehoshua Bruck

0

0

Neural networks successfully capture the computational power of the human brain for many tasks. Similarly inspired by the brain architecture, Nearest Neighbor (NN) representations is a novel approach of computation. We establish a firmer correspondence between NN representations and neural networks. Although it was known how to represent a single neuron using NN representations, there were no results even for small depth neural networks. Specifically, for depth-2 threshold circuits, we provide explicit constructions for their NN representation with an explicit bound on the number of bits to represent it. Example functions include NN representations of convex polytopes (AND of threshold gates), IP2, OR of threshold gates, and linear or exact decision lists.

5/13/2024

🧠

Hyperedge Interaction-aware Hypergraph Neural Network

Rongping Ye, Xiaobing Pei, Haoran Yang, Ruiqi Wang

0

0

Hypergraphs provide an effective modeling approach for modeling high-order relationships in many real-world datasets. To capture such complex relationships, several hypergraph neural networks have been proposed for learning hypergraph structure, which propagate information from nodes to hyperedges and then from hyperedges back to nodes. However, most existing methods focus on information propagation between hyperedges and nodes, neglecting the interactions among hyperedges themselves. In this paper, we propose HeIHNN, a hyperedge interaction-aware hypergraph neural network, which captures the interactions among hyperedges during the convolution process and introduce a novel mechanism to enhance information flow between hyperedges and nodes. Specifically, HeIHNN integrates the interactions between hyperedges into the hypergraph convolution by constructing a three-stage information propagation process. After propagating information from nodes to hyperedges, we introduce a hyperedge-level convolution to update the hyperedge embeddings. Finally, the embeddings that capture rich information from the interaction among hyperedges will be utilized to update the node embeddings. Additionally, we introduce a hyperedge outlier removal mechanism in the information propagation stages between nodes and hyperedges, which dynamically adjusts the hypergraph structure using the learned embeddings, effectively removing outliers. Extensive experiments conducted on real-world datasets show the competitive performance of HeIHNN compared with state-of-the-art methods.

4/8/2024