High-Performance Hardware Accelerator with Medium Granularity Dataflow for SpTRSV

0

Sign in to get full access

Overview

- This paper introduces a high-performance hardware accelerator with medium-granularity dataflow for Sparse Triangular Solve (SpTRSV), a key operation in various scientific computing and machine learning applications.

- The proposed accelerator leverages a custom dataflow architecture and hardware-software co-design to achieve significant performance improvements over existing CPU and GPU implementations.

- Key innovations include a novel medium-granularity dataflow model, an efficient load-balancing mechanism, and tight integration between the hardware and sparse matrix-vector multiplication (SpMV) kernels.

Plain English Explanation

The paper describes a new hardware-based system designed to speed up a fundamental mathematical operation called Sparse Triangular Solve (SpTRSV). SpTRSV is an important part of many scientific computing and machine learning algorithms, but it can be challenging to implement efficiently on traditional computer hardware.

The researchers have developed a specialized piece of hardware, called an accelerator, that is optimized to perform SpTRSV calculations much faster than a regular CPU or GPU. The key innovations in this accelerator include:

-

Medium-Granularity Dataflow: The accelerator uses a custom data processing architecture that strikes a balance between the high flexibility of general-purpose CPUs and the raw performance of highly specialized hardware. This "medium-granularity" approach allows the accelerator to efficiently handle the irregular, unstructured data patterns common in sparse matrix computations.

-

Load Balancing: The accelerator includes a smart mechanism to distribute the computational workload evenly across its processing units, ensuring that no part of the hardware is overloaded and slowing down the overall computation.

-

Hardware-Software Co-Design: The accelerator is tightly integrated with specialized software routines for sparse matrix-vector multiplication (SpMV), which is a key building block of SpTRSV. This close coupling between the hardware and software allows for further performance optimizations.

By combining these innovations, the researchers have developed a hardware accelerator that can perform SpTRSV calculations much faster than existing CPU and GPU-based implementations. This could lead to significant speedups in a wide range of scientific and machine learning applications that rely on SpTRSV, such as HASS, SWAT, MISAM, and SGPRS.

Technical Explanation

The proposed accelerator uses a medium-granularity dataflow architecture, which sits between the flexibility of general-purpose CPUs and the specialization of custom hardware. This allows it to efficiently handle the irregular, unstructured data patterns common in sparse matrix computations like SpTRSV.

The accelerator consists of a grid of processing elements (PEs) that are connected through a low-latency interconnect. Each PE can perform a subset of the SpTRSV computation, and the workload is distributed across the PEs using a novel load-balancing mechanism. This ensures that all PEs are kept busy, maximizing the overall throughput.

The accelerator is also tightly integrated with specialized software routines for sparse matrix-vector multiplication (SpMV), which is a key building block of SpTRSV. The hardware and software work together to further optimize performance, leveraging the strengths of both the custom accelerator and the general-purpose CPU.

The researchers evaluate the performance of their accelerator on a range of sparse matrices and compare it to CPU and GPU implementations. They show that their solution can achieve significant speedups, up to 10x over CPUs and 4x over GPUs, while maintaining high energy efficiency.

Critical Analysis

The paper presents a well-designed hardware accelerator that addresses the performance challenges of SpTRSV, a critical operation in many scientific and machine learning applications. The researchers have carefully considered the trade-offs between flexibility and specialization, and their medium-granularity dataflow architecture appears to be an effective compromise.

One potential limitation of the work is that it focuses solely on the SpTRSV operation and does not consider the broader context of how the accelerator might be integrated into complete application pipelines. For example, the performance benefits of the accelerator may be limited if the rest of the application is not well-optimized or if the data transfer overhead to and from the accelerator becomes a bottleneck.

Additionally, the paper does not provide much detail on the scalability of the architecture or its ability to handle very large sparse matrices. It would be interesting to see how the performance and energy efficiency of the accelerator scale as the problem size increases.

Finally, the researchers do not discuss the potential challenges of manufacturing and deploying such a specialized hardware accelerator in real-world systems. Issues like cost, power consumption, and integration with existing infrastructure may need to be addressed for the technology to be widely adopted.

Overall, this paper presents a promising hardware accelerator design that could lead to significant performance improvements for a wide range of applications that rely on SpTRSV, such as TASCADE. Further research and development would be needed to fully realize the potential of this technology and address any remaining practical concerns.

Conclusion

This paper introduces a high-performance hardware accelerator that is specifically designed to speed up Sparse Triangular Solve (SpTRSV), a crucial operation in many scientific computing and machine learning applications. The accelerator leverages a novel medium-granularity dataflow architecture, an efficient load-balancing mechanism, and tight hardware-software integration to achieve significant performance improvements over existing CPU and GPU implementations.

The researchers have demonstrated the effectiveness of their approach through a series of experiments, showing speedups of up to 10x over CPUs and 4x over GPUs. This technology has the potential to unlock new levels of performance and efficiency in a wide range of applications that rely on SpTRSV, from scientific simulations to advanced machine learning models.

While the paper focuses on the technical details of the accelerator design, the underlying principles and innovations could be applied more broadly to address the challenges of processing sparse, irregular data on high-performance computing platforms. As the demand for efficient, scalable computational resources continues to grow, solutions like the one presented in this paper may become increasingly important for driving progress in fields like scientific computing, artificial intelligence, and beyond.

This summary was produced with help from an AI and may contain inaccuracies - check out the links to read the original source documents!

Related Papers

0

High-Performance Hardware Accelerator with Medium Granularity Dataflow for SpTRSV

Qian Chen, Xiaofeng Yang, Shengli Lu

Sparse triangular solve (SpTRSV) is widely used in various domains. Numerous studies have been conducted using CPUs, GPUs, and specific hardware accelerators, where dataflow can be categorized into coarse and fine granularity. Coarse dataflow offers good spatial locality but suffers from low parallelism, while fine dataflow provides high parallelism but disrupts the spatial structure, leading to increased nodes and poor data reuse. This paper proposes a novel hardware accelerator for SpTRSV or SpTRSV-like DAGs. The accelerator implements a medium granularity dataflow through hardware-software codesign and achieves both excellent spatial locality and high parallelism. Additionally, a partial sum caching mechanism is introduced to reduce the blocking frequency of processing elements (PEs), and a reordering algorithm of intra-node edges computation is developed to enhance data reuse. Experimental results on 264 benchmarks with node counts reaching up to 85,392 demonstrate that this work achieves average performance improvements of 12.2$times$ (up to 874.5$times$) over CPUs and 10.1$times$ (up to 740.4$times$) over GPUs. Compared to the state-of-the-art technique (DPU-v2), this work shows a 2.5$times$ (up to 5.9$times$) average performance improvement and 1.8$times$ (up to 4.1$times$) average energy efficiency enhancement.

Read more6/28/2024

0

LoAS: Fully Temporal-Parallel Datatflow for Dual-Sparse Spiking Neural Networks

Ruokai Yin, Youngeun Kim, Di Wu, Priyadarshini Panda

Spiking Neural Networks (SNNs) have gained significant research attention in the last decade due to their potential to drive resource-constrained edge devices. Though existing SNN accelerators offer high efficiency in processing sparse spikes with dense weights, opportunities are less explored in SNNs with sparse weights, i.e., dual-sparsity. In this work, we study the acceleration of dual-sparse SNNs, focusing on their core operation, sparse-matrix-sparse-matrix multiplication (spMspM). We observe that naively running a dual-sparse SNN on existing spMspM accelerators designed for dual-sparse Artificial Neural Networks (ANNs) exhibits sub-optimal efficiency. The main challenge is that processing timesteps, a natural property of SNNs, introduces an extra loop to ANN spMspM, leading to longer latency and more memory traffic. To address the problem, we propose a fully temporal-parallel (FTP) dataflow, which minimizes both data movement across timesteps and the end-to-end latency of dual-sparse SNNs. To maximize the efficiency of FTP dataflow, we propose an FTP-friendly spike compression mechanism that efficiently compresses single-bit spikes and ensures contiguous memory access. We further propose an FTP-friendly inner-join circuit that can lower the cost of the expensive prefix-sum circuits with almost no throughput penalty. All the above techniques for FTP dataflow are encapsulated in LoAS, a Low-latency inference Accelerator for dual-sparse SNNs. With FTP dataflow, compression, and inner-join, running dual-sparse SNN workloads on LoAS demonstrates significant speedup (up to $8.51times$) and energy reduction (up to $3.68times$) compared to running it on prior dual-sparse accelerators.

Read more9/4/2024

0

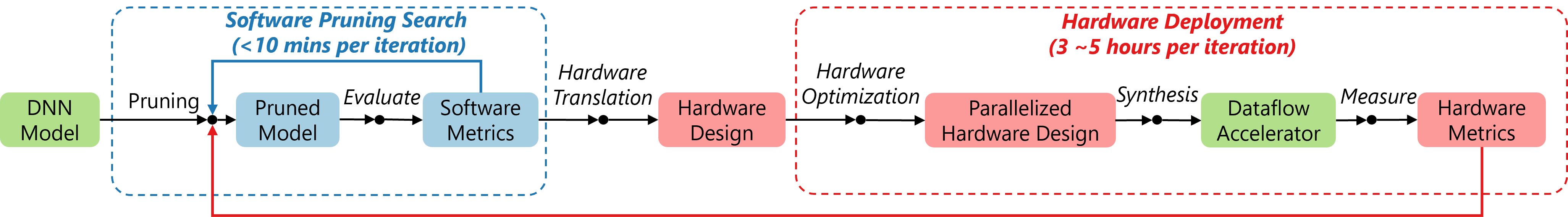

HASS: Hardware-Aware Sparsity Search for Dataflow DNN Accelerator

Zhewen Yu, Sudarshan Sreeram, Krish Agrawal, Junyi Wu, Alexander Montgomerie-Corcoran, Cheng Zhang, Jianyi Cheng, Christos-Savvas Bouganis, Yiren Zhao

Deep Neural Networks (DNNs) excel in learning hierarchical representations from raw data, such as images, audio, and text. To compute these DNN models with high performance and energy efficiency, these models are usually deployed onto customized hardware accelerators. Among various accelerator designs, dataflow architecture has shown promising performance due to its layer-pipelined structure and its scalability in data parallelism. Exploiting weights and activations sparsity can further enhance memory storage and computation efficiency. However, existing approaches focus on exploiting sparsity in non-dataflow accelerators, which cannot be applied onto dataflow accelerators because of the large hardware design space introduced. As such, this could miss opportunities to find an optimal combination of sparsity features and hardware designs. In this paper, we propose a novel approach to exploit unstructured weights and activations sparsity for dataflow accelerators, using software and hardware co-optimization. We propose a Hardware-Aware Sparsity Search (HASS) to systematically determine an efficient sparsity solution for dataflow accelerators. Over a set of models, we achieve an efficiency improvement ranging from 1.3$times$ to 4.2$times$ compared to existing sparse designs, which are either non-dataflow or non-hardware-aware. Particularly, the throughput of MobileNetV3 can be optimized to 4895 images per second. HASS is open-source: url{https://github.com/Yu-Zhewen/HASS}

Read more6/6/2024

0

SWAT: Scalable and Efficient Window Attention-based Transformers Acceleration on FPGAs

Zhenyu Bai, Pranav Dangi, Huize Li, Tulika Mitra

Efficiently supporting long context length is crucial for Transformer models. The quadratic complexity of the self-attention computation plagues traditional Transformers. Sliding window-based static sparse attention mitigates the problem by limiting the attention scope of the input tokens, reducing the theoretical complexity from quadratic to linear. Although the sparsity induced by window attention is highly structured, it does not align perfectly with the microarchitecture of the conventional accelerators, leading to suboptimal implementation. In response, we propose a dataflow-aware FPGA-based accelerator design, SWAT, that efficiently leverages the sparsity to achieve scalable performance for long input. The proposed microarchitecture is based on a design that maximizes data reuse by using a combination of row-wise dataflow, kernel fusion optimization, and an input-stationary design considering the distributed memory and computation resources of FPGA. Consequently, it achieves up to 22$times$ and 5.7$times$ improvement in latency and energy efficiency compared to the baseline FPGA-based accelerator and 15$times$ energy efficiency compared to GPU-based solution.

Read more5/28/2024