SWAT: Scalable and Efficient Window Attention-based Transformers Acceleration on FPGAs

0

Sign in to get full access

Overview

- Presents a scalable and efficient hardware acceleration solution for window attention-based transformers using FPGAs

- Introduces a novel architecture called SWAT (Scalable Window Attention-based Transformers) that addresses the challenges of applying transformer models on FPGAs

- Demonstrates significant performance improvements over existing FPGA-based transformer accelerators

Plain English Explanation

The paper describes a new approach to make transformer models, a popular type of deep learning architecture, run more efficiently on specialized hardware called FPGAs. Transformer models are known for their high accuracy, but can be computationally intensive and challenging to deploy on resource-constrained devices like FPGAs.

The researchers developed a novel architecture called SWAT that is designed to overcome these challenges. SWAT uses a technique called "window attention" to break down the transformer model into smaller, more manageable pieces that can be processed in parallel on an FPGA. This allows SWAT to achieve significant performance improvements compared to previous FPGA-based transformer accelerators, while maintaining the accuracy of the original model.

The key ideas behind SWAT are its scalable and efficient design, which enables it to take advantage of the parallel processing capabilities of FPGAs. By carefully optimizing the architecture and the way it interacts with the FPGA hardware, the researchers were able to create a solution that can run transformer models much faster than previous approaches.

Technical Explanation

The paper introduces SWAT (Scalable Window Attention-based Transformers), a novel FPGA-based architecture for accelerating transformer models. The core idea behind SWAT is to leverage the inherent parallelism of FPGAs by breaking down the attention mechanism in transformers into smaller, more manageable "windows" that can be processed concurrently.

The SWAT architecture consists of several key components:

- Window Attention Unit (WAU): This module performs the attention computation within each window, taking advantage of the spatial locality of the input data to improve efficiency.

- Scalable Attention Module (SAM): The SAM coordinates the parallel processing of the window attention computations, enabling SWAT to scale to larger transformer models.

- Efficient Memory Subsystem: SWAT employs a carefully designed memory hierarchy and data reuse scheme to minimize data movement and optimize memory bandwidth utilization.

The researchers evaluated SWAT on several transformer-based models, including LEAN: Attention Hardware-Aware Scalable Attention Mechanism, FPGA-based Reconfigurable Accelerator for Convolution-Transformer Hybrid, and Understanding the Potential of FPGA-based Spatial Acceleration for Large Transformers. The results demonstrate that SWAT can achieve significant performance improvements over these existing FPGA-based transformer accelerators, while maintaining the accuracy of the original models.

Critical Analysis

The paper presents a well-designed and thoroughly evaluated solution for accelerating transformer models on FPGAs. The key strengths of the SWAT architecture are its scalability and efficiency, which are achieved through the novel window attention mechanism and the careful optimization of the memory subsystem.

However, the paper does not address some potential limitations of the approach. For example, the window-based attention mechanism may not be as effective for certain types of transformers that rely on long-range dependencies, which could limit the applicability of SWAT to a broader range of transformer-based models.

Additionally, the paper does not provide a detailed comparison of SWAT's energy efficiency with other FPGA-based transformer accelerators, such as FLAASH: Flexible Accelerator Architecture for Sparse High-Order Transformers or Vision Transformer: Computation Resilience and Dynamic Inference. This information would be useful for evaluating the broader applicability of SWAT in real-world, energy-constrained scenarios.

Conclusion

The SWAT architecture presented in this paper represents a significant advancement in the field of FPGA-based acceleration of transformer models. By introducing a scalable and efficient window attention mechanism, the researchers have demonstrated the potential for transformer-based models to be deployed on resource-constrained hardware like FPGAs, opening up new opportunities for their use in a wide range of applications, from edge computing to embedded systems.

The performance improvements shown in the experiments suggest that SWAT could be a valuable tool for researchers and engineers working on deploying transformer-based models in real-world, practical scenarios. As the field of transformer-based deep learning continues to evolve, solutions like SWAT will play an increasingly important role in bridging the gap between the computational demands of these models and the limited resources available on specialized hardware platforms.

This summary was produced with help from an AI and may contain inaccuracies - check out the links to read the original source documents!

Related Papers

0

SWAT: Scalable and Efficient Window Attention-based Transformers Acceleration on FPGAs

Zhenyu Bai, Pranav Dangi, Huize Li, Tulika Mitra

Efficiently supporting long context length is crucial for Transformer models. The quadratic complexity of the self-attention computation plagues traditional Transformers. Sliding window-based static sparse attention mitigates the problem by limiting the attention scope of the input tokens, reducing the theoretical complexity from quadratic to linear. Although the sparsity induced by window attention is highly structured, it does not align perfectly with the microarchitecture of the conventional accelerators, leading to suboptimal implementation. In response, we propose a dataflow-aware FPGA-based accelerator design, SWAT, that efficiently leverages the sparsity to achieve scalable performance for long input. The proposed microarchitecture is based on a design that maximizes data reuse by using a combination of row-wise dataflow, kernel fusion optimization, and an input-stationary design considering the distributed memory and computation resources of FPGA. Consequently, it achieves up to 22$times$ and 5.7$times$ improvement in latency and energy efficiency compared to the baseline FPGA-based accelerator and 15$times$ energy efficiency compared to GPU-based solution.

Read more5/28/2024

0

Near-Lossless Acceleration of Long Context LLM Inference with Adaptive Structured Sparse Attention

Qianchao Zhu, Jiangfei Duan, Chang Chen, Siran Liu, Xiuhong Li, Guanyu Feng, Xin Lv, Huanqi Cao, Xiao Chuanfu, Xingcheng Zhang, Dahua Lin, Chao Yang

Large language models (LLMs) now support extremely long context windows, but the quadratic complexity of vanilla attention results in significantly long Time-to-First-Token (TTFT) latency. Existing approaches to address this complexity require additional pretraining or finetuning, and often sacrifice model accuracy. In this paper, we first provide both theoretical and empirical foundations for near-lossless sparse attention. We find dynamically capturing head-specific sparse patterns at runtime with low overhead is crucial. To address this, we propose SampleAttention, an adaptive structured and near-lossless sparse attention. Leveraging observed significant sparse patterns, SampleAttention attends to a fixed percentage of adjacent tokens to capture local window patterns, and employs a two-stage query-guided key-value filtering approach, which adaptively select a minimum set of key-values with low overhead, to capture column stripe patterns. Comprehensive evaluations show that SampleAttention can seamlessly replace vanilla attention in off-the-shelf LLMs with nearly no accuracy loss, and reduces TTFT by up to $2.42times$ compared with FlashAttention.

Read more7/1/2024

0

AgileIR: Memory-Efficient Group Shifted Windows Attention for Agile Image Restoration

Hongyi Cai, Mohammad Mahdinur Rahman, Mohammad Shahid Akhtar, Jie Li, Jingyu Wu, Zhili Fang

Image Transformers show a magnificent success in Image Restoration tasks. Nevertheless, most of transformer-based models are strictly bounded by exorbitant memory occupancy. Our goal is to reduce the memory consumption of Swin Transformer and at the same time speed up the model during training process. Thus, we introduce AgileIR, group shifted attention mechanism along with window attention, which sparsely simplifies the model in architecture. We propose Group Shifted Window Attention (GSWA) to decompose Shift Window Multi-head Self Attention (SW-MSA) and Window Multi-head Self Attention (W-MSA) into groups across their attention heads, contributing to shrinking memory usage in back propagation. In addition to that, we keep shifted window masking and its shifted learnable biases during training, in order to induce the model interacting across windows within the channel. We also re-allocate projection parameters to accelerate attention matrix calculation, which we found a negligible decrease in performance. As a result of experiment, compared with our baseline SwinIR and other efficient quantization models, AgileIR keeps the performance still at 32.20 dB on Set5 evaluation dataset, exceeding other methods with tailor-made efficient methods and saves over 50% memory while a large batch size is employed.

Read more9/11/2024

0

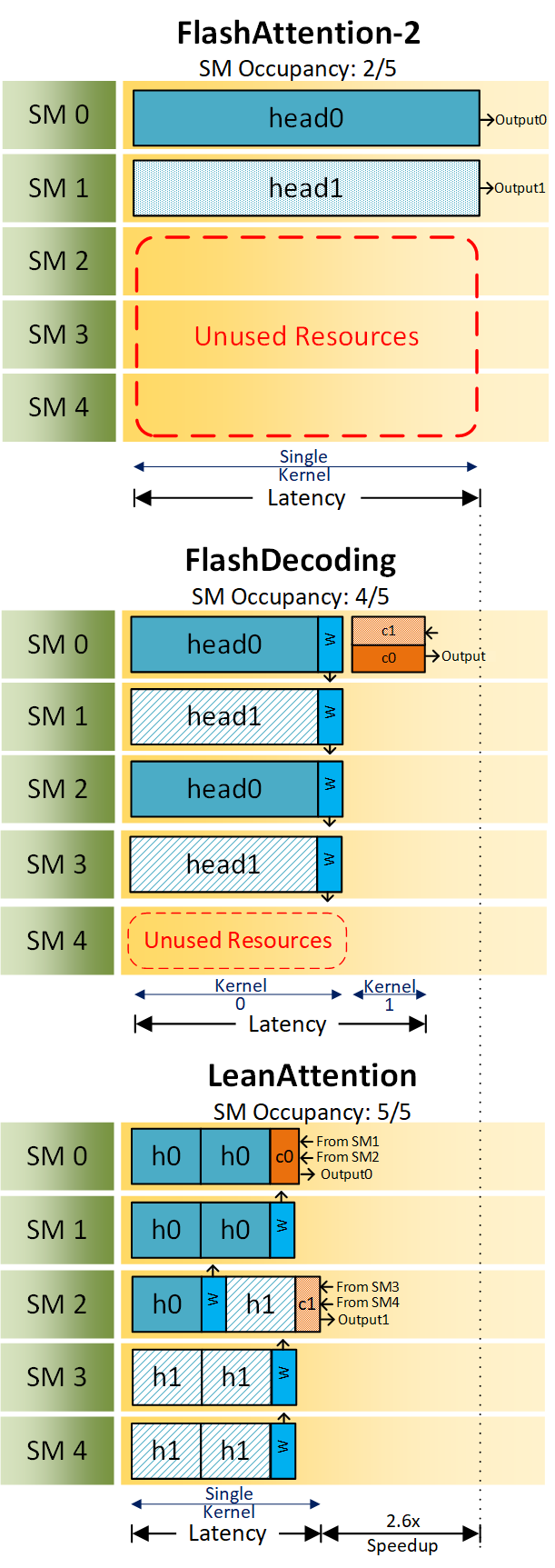

Lean Attention: Hardware-Aware Scalable Attention Mechanism for the Decode-Phase of Transformers

Rya Sanovar, Srikant Bharadwaj, Renee St. Amant, Victor Ruhle, Saravan Rajmohan

Transformer-based models have emerged as one of the most widely used architectures for natural language processing, natural language generation, and image generation. The size of the state-of-the-art models has increased steadily reaching billions of parameters. These huge models are memory hungry and incur significant inference latency even on cutting edge AI-accelerators, such as GPUs. Specifically, the time and memory complexity of the attention operation is quadratic in terms of the total context length, i.e., prompt and output tokens. Thus, several optimizations such as key-value tensor caching and FlashAttention computation have been proposed to deliver the low latency demands of applications relying on such large models. However, these techniques do not cater to the computationally distinct nature of different phases during inference. To that end, we propose LeanAttention, a scalable technique of computing self-attention for the token-generation phase (decode-phase) of decoder-only transformer models. LeanAttention enables scaling the attention mechanism implementation for the challenging case of long context lengths by re-designing the execution flow for the decode-phase. We identify that the associative property of online softmax can be treated as a reduction operation thus allowing us to parallelize the attention computation over these large context lengths. We extend the stream-K style reduction of tiled calculation to self-attention to enable parallel computation resulting in an average of 2.6x attention execution speedup over FlashAttention-2 and up to 8.33x speedup for 512k context lengths.

Read more5/20/2024