ElasticAI: Creating and Deploying Energy-Efficient Deep Learning Accelerator for Pervasive Computing

0

Sign in to get full access

Overview

- The paper "ElasticAI: Creating and Deploying Energy-Efficient Deep Learning Accelerator for Pervasive Computing" explores the development of a deep learning accelerator that is energy-efficient and suitable for deployment in pervasive computing environments.

- The researchers designed and implemented a hardware accelerator called ElasticAI that aims to achieve high energy efficiency while maintaining performance for deep learning workloads.

- ElasticAI is evaluated on various deep learning models and benchmarks, demonstrating its ability to outperform existing solutions in terms of energy efficiency and performance.

Plain English Explanation

The paper focuses on creating a specialized hardware device, called a "deep learning accelerator," that can run deep learning models efficiently. Deep learning is a powerful AI technique that has become increasingly important in a wide range of applications, from image recognition to language processing. However, running deep learning models can be computationally intensive and energy-hungry, which can be a challenge for devices with limited power and resources, such as smartphones or sensors in the Internet of Things (IoT).

The researchers developed a deep learning accelerator called ElasticAI that is designed to be highly energy-efficient while still maintaining good performance. This means it can run deep learning models without draining the battery too quickly, making it well-suited for use in pervasive computing environments like IoT devices, where power consumption is a critical concern.

The key innovation of ElasticAI is its ability to adapt its internal architecture to the specific deep learning model being run, optimizing the hardware to match the model's computational needs. This "elasticity" helps ElasticAI achieve high energy efficiency without sacrificing too much performance.

The researchers evaluated ElasticAI on a variety of deep learning models and benchmarks, and found that it outperformed existing energy-efficient deep learning accelerators in terms of both energy efficiency and performance. This suggests that ElasticAI could be a valuable tool for deploying deep learning in power-constrained environments, such as IoT devices or mobile applications.

Technical Explanation

The paper presents the design and implementation of ElasticAI, a deep learning accelerator that aims to achieve high energy efficiency while maintaining good performance. The key elements of the research are as follows:

-

Architecture Design: ElasticAI is designed with a reconfigurable architecture that can adapt to the specific computational requirements of the deep learning model being executed. This includes dynamic resource allocation, data reuse, and efficient data movement.

-

Hardware-Software Co-design: The researchers developed a hardware-software co-design approach to optimize the ElasticAI accelerator for different deep learning models. This involves automatically generating performance models and hardware configurations to match the model's characteristics.

-

Evaluation: The researchers evaluated ElasticAI on a range of deep learning models and benchmarks, including image classification, object detection, and natural language processing tasks. They compared its performance and energy efficiency to state-of-the-art energy-efficient deep learning accelerators.

The results show that ElasticAI outperforms existing solutions in terms of energy efficiency and performance, making it a promising approach for deploying deep learning in power-constrained environments like IoT devices and mobile applications.

Critical Analysis

The paper presents a compelling approach to developing an energy-efficient deep learning accelerator, but there are a few potential limitations and areas for further research:

-

Scope of Evaluation: While the researchers evaluated ElasticAI on a range of deep learning models, the benchmarks may not fully represent the diversity of real-world deep learning workloads. Further evaluation on a broader set of models and applications would help better understand the accelerator's capabilities and limitations.

-

Hardware Implementation: The paper focuses on the architectural design and performance modeling of ElasticAI, but does not provide detailed information about the hardware implementation or the actual power consumption of the accelerator. More information on the physical realization of ElasticAI would be helpful to fully assess its energy efficiency.

-

Comparison to Software-based Approaches: While the paper compares ElasticAI to other hardware accelerators, it would be valuable to also compare its performance and energy efficiency to software-based deep learning inference on general-purpose processors. This could help determine the specific advantages of the hardware-based approach.

-

Integration with Existing Systems: The paper does not discuss how ElasticAI would be integrated and deployed in real-world pervasive computing systems. Addressing the practical challenges of integrating the accelerator with existing hardware and software stacks would be an important next step.

Overall, the ElasticAI approach is a promising step towards energy-efficient deep learning acceleration, but further research and development is needed to fully realize its potential for real-world deployments.

Conclusion

The "ElasticAI: Creating and Deploying Energy-Efficient Deep Learning Accelerator for Pervasive Computing" paper presents a novel deep learning accelerator design that aims to achieve high energy efficiency while maintaining good performance. The key innovation is the accelerator's reconfigurable architecture that can adapt to the computational needs of different deep learning models, optimizing the hardware for energy efficiency.

The researchers' evaluation of ElasticAI on various deep learning benchmarks shows that it outperforms existing energy-efficient deep learning accelerators in both energy efficiency and performance. This suggests that ElasticAI could be a valuable tool for deploying deep learning in power-constrained environments, such as IoT devices and mobile applications, where energy efficiency is critical.

While the paper presents a compelling approach, there are still some areas for further research and development, such as broader evaluation, hardware implementation details, and integration with existing systems. Addressing these challenges could help unlock the full potential of ElasticAI and similar energy-efficient deep learning accelerators for pervasive computing applications.

This summary was produced with help from an AI and may contain inaccuracies - check out the links to read the original source documents!

Related Papers

0

ElasticAI: Creating and Deploying Energy-Efficient Deep Learning Accelerator for Pervasive Computing

Chao Qian, Tianheng Ling, Gregor Schiele

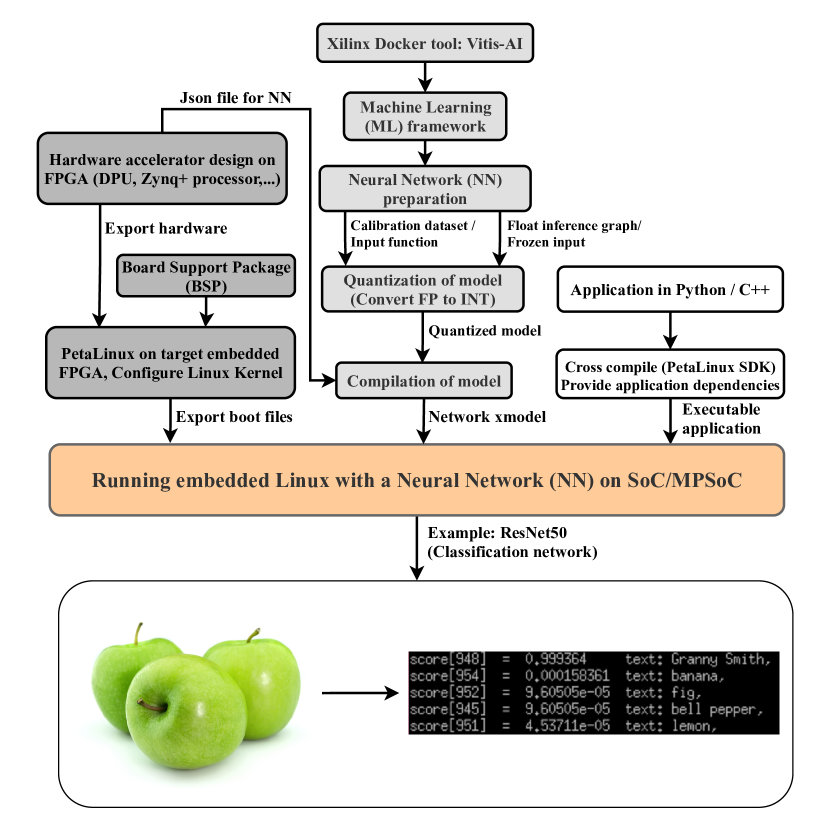

Deploying Deep Learning (DL) on embedded end devices is a scorching trend in pervasive computing. Since most Microcontrollers on embedded devices have limited computing power, it is necessary to add a DL accelerator. Embedded Field Programmable Gate Arrays (FPGAs) are suitable for deploying DL accelerators for embedded devices, but developing an energy-efficient DL accelerator on an FPGA is not easy. Therefore, we propose the ElasticAI-Workflow that aims to help DL developers to create and deploy DL models as hardware accelerators on embedded FPGAs. This workflow consists of two key components: the ElasticAI-Creator and the Elastic Node. The former is a toolchain for automatically generating DL accelerators on FPGAs. The latter is a hardware platform for verifying the performance of the generated accelerators. With this combination, the performance of the accelerator can be sufficiently guaranteed. We will demonstrate the potential of our approach through a case study.

Read more9/17/2024

🧠

0

Efficient Edge AI: Deploying Convolutional Neural Networks on FPGA with the Gemmini Accelerator

Federico Nicolas Peccia, Svetlana Pavlitska, Tobias Fleck, Oliver Bringmann

The growing concerns regarding energy consumption and privacy have prompted the development of AI solutions deployable on the edge, circumventing the substantial CO2 emissions associated with cloud servers and mitigating risks related to sharing sensitive data. But deploying Convolutional Neural Networks (CNNs) on non-off-the-shelf edge devices remains a complex and labor-intensive task. In this paper, we present and end-to-end workflow for deployment of CNNs on Field Programmable Gate Arrays (FPGAs) using the Gemmini accelerator, which we modified for efficient implementation on FPGAs. We describe how we leverage the use of open source software on each optimization step of the deployment process, the customizations we added to them and its impact on the final system's performance. We were able to achieve real-time performance by deploying a YOLOv7 model on a Xilinx ZCU102 FPGA with an energy efficiency of 36.5 GOP/s/W. Our FPGA-based solution demonstrates superior power efficiency compared with other embedded hardware devices, and even outperforms other FPGA reference implementations. Finally, we present how this kind of solution can be integrated into a wider system, by testing our proposed platform in a traffic monitoring scenario.

Read more8/15/2024

0

Latency optimized Deep Neural Networks (DNNs): An Artificial Intelligence approach at the Edge using Multiprocessor System on Chip (MPSoC)

Seyed Nima Omidsajedi, Rekha Reddy, Jianming Yi, Jan Herbst, Christoph Lipps, Hans Dieter Schotten

Almost in every heavily computation-dependent application, from 6G communication systems to autonomous driving platforms, a large portion of computing should be near to the client side. Edge computing (AI at Edge) in mobile devices is one of the optimized approaches for addressing this requirement. Therefore, in this work, the possibilities and challenges of implementing a low-latency and power-optimized smart mobile system are examined. Utilizing Field Programmable Gate Array (FPGA) based solutions at the edge will lead to bandwidth-optimized designs and as a consequence can boost the computational effectiveness at a system-level deadline. Moreover, various performance aspects and implementation feasibilities of Neural Networks (NNs) on both embedded FPGA edge devices (using Xilinx Multiprocessor System on Chip (MPSoC)) and Cloud are discussed throughout this research. The main goal of this work is to demonstrate a hybrid system that uses the deep learning programmable engine developed by Xilinx Inc. as the main component of the hardware accelerator. Then based on this design, an efficient system for mobile edge computing is represented by utilizing an embedded solution.

Read more7/29/2024

0

Embedded FPGA Developments in 130nm and 28nm CMOS for Machine Learning in Particle Detector Readout

Julia Gonski, Aseem Gupta, Haoyi Jia, Hyunjoon Kim, Lorenzo Rota, Larry Ruckman, Angelo Dragone, Ryan Herbst

Embedded field programmable gate array (eFPGA) technology allows the implementation of reconfigurable logic within the design of an application-specific integrated circuit (ASIC). This approach offers the low power and efficiency of an ASIC along with the ease of FPGA configuration, particularly beneficial for the use case of machine learning in the data pipeline of next-generation collider experiments. An open-source framework called FABulous was used to design eFPGAs using 130 nm and 28 nm CMOS technology nodes, which were subsequently fabricated and verified through testing. The capability of an eFPGA to act as a front-end readout chip was assessed using simulation of high energy particles passing through a silicon pixel sensor. A machine learning-based classifier, designed for reduction of sensor data at the source, was synthesized and configured onto the eFPGA. A successful proof-of-concept was demonstrated through reproduction of the expected algorithm result on the eFPGA with perfect accuracy. Further development of the eFPGA technology and its application to collider detector readout is discussed.

Read more8/29/2024