An Evaluation of Continual Learning for Advanced Node Semiconductor Defect Inspection

0

Sign in to get full access

Overview

- This paper evaluates the use of continual learning techniques for advanced node semiconductor defect inspection.

- Continual learning refers to the ability of machine learning models to continuously learn and adapt to new data without forgetting previously learned information.

- The researchers investigate the effectiveness of continual learning approaches in the context of semiconductor defect detection, a critical task for maintaining high product quality.

Plain English Explanation

Semiconductor chips are the building blocks of modern electronics, powering everything from smartphones to laptops. During the manufacturing process, these chips can develop tiny defects that can negatively impact their performance and reliability. Detecting and addressing these defects is crucial for ensuring high-quality semiconductor products.

The researchers in this paper explore the use of a machine learning technique called "continual learning" to improve semiconductor defect detection. Continual learning allows AI models to continuously learn and adapt to new data without forgetting what they've learned before. This could be particularly useful in the semiconductor industry, where the types of defects can change over time as the manufacturing process evolves.

By evaluating different continual learning approaches, the researchers aim to determine the most effective way to deploy these techniques for advanced node semiconductor defect inspection. Their findings could help semiconductor manufacturers improve their quality control processes and deliver more reliable products to consumers.

Technical Explanation

The paper starts by reviewing the relevant research on semiconductor defect detection and continual learning. The researchers then describe their methodology, which involves training a neural network model using various continual learning strategies and evaluating its performance on a semiconductor defect dataset.

Key aspects of the experimental setup include:

- The use of a dataset of semiconductor defect images to train and evaluate the models

- The implementation of different continual learning approaches, such as rehearsal-based, regularization-based, and parameter isolation-based methods

- Metrics used to assess the models' performance, including accuracy, forgetting, and forward transfer

The results demonstrate the potential benefits of continual learning for semiconductor defect inspection, with some approaches outperforming traditional fine-tuning techniques. The researchers also discuss the limitations of their study and provide recommendations for future research in this area.

Critical Analysis

The researchers present a thorough evaluation of continual learning techniques for semiconductor defect inspection, which is a valuable contribution to the field. However, the paper does not address some potential limitations of the study:

- The dataset used may not be representative of the full range of defects encountered in advanced node semiconductor manufacturing, potentially limiting the generalizability of the findings.

- The comparison to fine-tuning could be expanded to include other baseline approaches, such as transfer learning or meta-learning, to provide a more comprehensive understanding of the relative strengths and weaknesses of continual learning.

- The paper does not explore the computational and memory overhead associated with the different continual learning strategies, which could be an important consideration for real-world deployment.

Overall, the research presented in this paper represents a valuable step forward in understanding the potential of continual learning for semiconductor defect inspection. However, further studies are needed to fully validate the findings and address the potential limitations.

Conclusion

This paper evaluates the use of continual learning techniques for advanced node semiconductor defect inspection, a critical task for maintaining high product quality in the semiconductor industry. The researchers demonstrate the potential benefits of continual learning approaches compared to traditional fine-tuning, highlighting the importance of the ability to continuously adapt and learn from new data.

The findings of this study could have significant implications for semiconductor manufacturers, as they work to improve their quality control processes and deliver more reliable products to consumers. By leveraging continual learning, they may be able to more effectively detect and address emerging defects, leading to higher-quality and more cost-effective semiconductor devices.

As the semiconductor industry continues to evolve, the need for advanced defect detection and inspection techniques will only become more pressing. The insights gained from this research represent an important step forward in addressing this challenge and could inspire further advancements in the field.

This summary was produced with help from an AI and may contain inaccuracies - check out the links to read the original source documents!

Related Papers

0

An Evaluation of Continual Learning for Advanced Node Semiconductor Defect Inspection

Amit Prasad, Bappaditya Dey, Victor Blanco, Sandip Halder

Deep learning-based semiconductor defect inspection has gained traction in recent years, offering a powerful and versatile approach that provides high accuracy, adaptability, and efficiency in detecting and classifying nano-scale defects. However, semiconductor manufacturing processes are continually evolving, leading to the emergence of new types of defects over time. This presents a significant challenge for conventional supervised defect detectors, as they may suffer from catastrophic forgetting when trained on new defect datasets, potentially compromising performance on previously learned tasks. An alternative approach involves the constant storage of previously trained datasets alongside pre-trained model versions, which can be utilized for (re-)training from scratch or fine-tuning whenever encountering a new defect dataset. However, adhering to such a storage template is impractical in terms of size, particularly when considering High-Volume Manufacturing (HVM). Additionally, semiconductor defect datasets, especially those encompassing stochastic defects, are often limited and expensive to obtain, thus lacking sufficient representation of the entire universal set of defectivity. This work introduces a task-agnostic, meta-learning approach aimed at addressing this challenge, which enables the incremental addition of new defect classes and scales to create a more robust and generalized model for semiconductor defect inspection. We have benchmarked our approach using real resist-wafer SEM (Scanning Electron Microscopy) datasets for two process steps, ADI and AEI, demonstrating its superior performance compared to conventional supervised training methods.

Read more7/18/2024

0

Addressing Class Imbalance and Data Limitations in Advanced Node Semiconductor Defect Inspection: A Generative Approach for SEM Images

Bappaditya Dey, Vic De Ridder, Victor Blanco, Sandip Halder, Bartel Van Waeyenberge

Precision in identifying nanometer-scale device-killer defects is crucial in both semiconductor research and development as well as in production processes. The effectiveness of existing ML-based approaches in this context is largely limited by the scarcity of data, as the production of real semiconductor wafer data for training these models involves high financial and time costs. Moreover, the existing simulation methods fall short of replicating images with identical noise characteristics, surface roughness and stochastic variations at advanced nodes. We propose a method for generating synthetic semiconductor SEM images using a diffusion model within a limited data regime. In contrast to images generated through conventional simulation methods, SEM images generated through our proposed DL method closely resemble real SEM images, replicating their noise characteristics and surface roughness adaptively. Our main contributions, which are validated on three different real semiconductor datasets, are: i) proposing a patch-based generative framework utilizing DDPM to create SEM images with intended defect classes, addressing challenges related to class-imbalance and data insufficiency, ii) demonstrating generated synthetic images closely resemble real SEM images acquired from the tool, preserving all imaging conditions and metrology characteristics without any metadata supervision, iii) demonstrating a defect detector trained on generated defect dataset, either independently or combined with a limited real dataset, can achieve similar or improved performance on real wafer SEM images during validation/testing compared to exclusive training on a real defect dataset, iv) demonstrating the ability of the proposed approach to transfer defect types, critical dimensions, and imaging conditions from one specified CD/Pitch and metrology specifications to another, thereby highlighting its versatility.

Read more7/16/2024

0

Towards Improved Semiconductor Defect Inspection for high-NA EUVL based on SEMI-SuperYOLO-NAS

Ying-Lin Chen, Jacob Deforce, Vic De Ridder, Bappaditya Dey, Victor Blanco, Sandip Halder, Philippe Leray

Due to potential pitch reduction, the semiconductor industry is adopting High-NA EUVL technology. However, its low depth of focus presents challenges for High Volume Manufacturing. To address this, suppliers are exploring thinner photoresists and new underlayers/hardmasks. These may suffer from poor SNR, complicating defect detection. Vision-based ML algorithms offer a promising solution for semiconductor defect inspection. However, developing a robust ML model across various image resolutions without explicit training remains a challenge for nano-scale defect inspection. This research's goal is to propose a scale-invariant ADCD framework capable to upscale images, addressing this issue. We propose an improvised ADCD framework as SEMI-SuperYOLO-NAS, which builds upon the baseline YOLO-NAS architecture. This framework integrates a SR assisted branch to aid in learning HR features by the defect detection backbone, particularly for detecting nano-scale defect instances from LR images. Additionally, the SR-assisted branch can recursively generate upscaled images from their corresponding downscaled counterparts, enabling defect detection inference across various image resolutions without requiring explicit training. Moreover, we investigate improved data augmentation strategy aimed at generating diverse and realistic training datasets to enhance model performance. We have evaluated our proposed approach using two original FAB datasets obtained from two distinct processes and captured using two different imaging tools. Finally, we demonstrate zero-shot inference for our model on a new, originating from a process condition distinct from the training dataset and possessing different Pitch characteristics. Experimental validation demonstrates that our proposed ADCD framework aids in increasing the throughput of imaging tools for defect inspection by reducing the required image pixel resolutions.

Read more4/10/2024

0

Advancing SEM Based Nano-Scale Defect Analysis in Semiconductor Manufacturing for Advanced IC Nodes

Bappaditya Dey, Matthias Monden, Victor Blanco, Sandip Halder, Stefan De Gendt

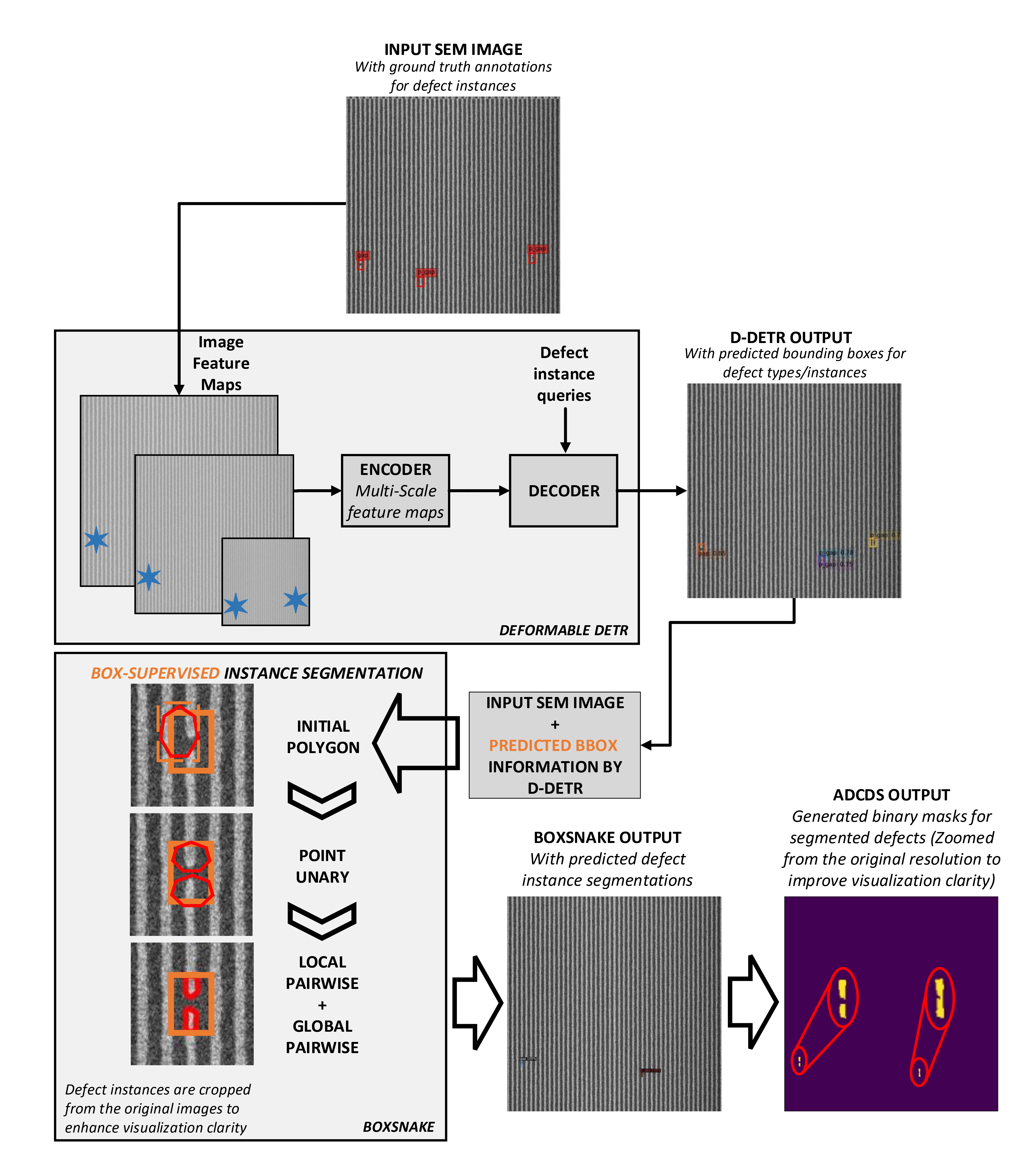

In this research, we introduce a unified end-to-end Automated Defect Classification-Detection-Segmentation (ADCDS) framework for classifying, detecting, and segmenting multiple instances of semiconductor defects for advanced nodes. This framework consists of two modules: (a) a defect detection module, followed by (b) a defect segmentation module. The defect detection module employs Deformable DETR to aid in the classification and detection of nano-scale defects, while the segmentation module utilizes BoxSnake. BoxSnake facilitates box-supervised instance segmentation of nano-scale defects, supported by the former module. This simplifies the process by eliminating the laborious requirement for ground-truth pixel-wise mask annotation by human experts, which is typically associated with training conventional segmentation models. We have evaluated the performance of our ADCDS framework using two distinct process datasets from real wafers, as ADI and AEI, specifically focusing on Line-space patterns. We have demonstrated the applicability and significance of our proposed methodology, particularly in the nano-scale segmentation and generation of binary defect masks, using the challenging ADI SEM dataset where ground-truth pixelwise segmentation annotations were unavailable. Furthermore, we have presented a comparative analysis of our proposed framework against previous approaches to demonstrate its effectiveness. Our proposed framework achieved an overall [email protected] of 72.19 for detection and 78.86 for segmentation on the ADI dataset. Similarly, for the AEI dataset, these metrics were 90.38 for detection and 95.48 for segmentation. Thus, our proposed framework effectively fulfils the requirements of advanced defect analysis while addressing significant constraints.

Read more9/9/2024