LLM in a flash: Efficient Large Language Model Inference with Limited Memory

13

Sign in to get full access

Overview

- Researchers propose an efficient method for running large language models (LLMs) on resource-constrained devices with limited memory.

- The method leverages flash memory to cache model parameters and activations, enabling fast inference without the need for large on-chip memory.

- Experiments demonstrate significant improvements in inference speed and energy efficiency compared to traditional approaches.

Plain English Explanation

Large language models (LLMs) have become incredibly powerful, but they also require a lot of memory to run. This makes it challenging to use them on devices with limited resources, like smartphones or edge devices.

The researchers in this paper have developed a new technique to run LLMs more efficiently on these resource-constrained devices. The key idea is to use flash memory to store the model parameters and intermediate computations, rather than relying entirely on the device's main memory.

Flash memory is a type of non-volatile storage that can be accessed quickly, like the memory in a USB drive. By caching the LLM's data in flash memory, the researchers were able to significantly reduce the memory requirements and improve the inference speed and energy efficiency.

This is an important advancement, as it could enable the deployment of powerful LLMs on a wider range of devices, including those with limited compute and memory resources. This could open up new applications for LLMs in areas like mobile, edge, and embedded computing.

Technical Explanation

The researchers propose a technique called "LLM in a Flash" that leverages flash memory to enable efficient LLM inference on resource-constrained devices. The key components of their approach include:

-

Flash Memory Caching: The model parameters and intermediate activations are stored in flash memory, which can be accessed quickly and without the need for large on-chip SRAM.

-

Activation Spilling: During inference, activations that do not fit in SRAM are spilled to flash memory, reducing the overall memory footprint.

-

Selective Caching: The researchers use a caching strategy to selectively store the most important model parameters and activations in flash, balancing performance and memory usage.

Experiments on various LLM architectures and datasets demonstrate significant improvements in inference latency and energy efficiency compared to traditional approaches that rely solely on SRAM. The researchers also provide models for predicting the performance and energy consumption of their approach, which can inform the design of future LLM systems.

Critical Analysis

The "LLM in a Flash" approach presents a promising solution for running large language models on resource-constrained devices. However, there are a few potential limitations and areas for further research:

-

Generalization to Diverse LLM Architectures: The experiments focus on a specific set of LLM models and tasks. Further research is needed to evaluate the approach's generalizability to a wider range of LLM architectures and application scenarios.

-

Endurance Concerns: Frequent writes to flash memory may raise concerns about its endurance and long-term reliability. Strategies to mitigate this issue should be explored.

-

Integration with Hardware Acceleration: The current work focuses on software-level optimizations. Combining this approach with specialized hardware acceleration for LLM inference could lead to even greater performance and energy efficiency gains.

Overall, the "LLM in a Flash" technique represents an important step towards making large language models more accessible on resource-constrained devices. Further research and development in this area could have significant implications for the deployment of powerful AI models in real-world applications.

Conclusion

The "LLM in a Flash" approach proposed in this paper offers an efficient solution for running large language models on devices with limited memory. By leveraging flash memory to cache model parameters and activations, the researchers demonstrate significant improvements in inference speed and energy efficiency compared to traditional approaches.

This work has important implications for the deployment of LLMs in a wide range of applications, from mobile devices to edge computing systems. As the demand for powerful AI models continues to grow, techniques like "LLM in a Flash" will be crucial for bridging the gap between the computational requirements of LLMs and the constraints of resource-limited hardware.

Further research and development in this area, including exploring new solutions for LLM acceleration and optimization and investigating the compressibility of quantized LLMs, could lead to even more efficient and accessible large language models in the years to come.

This summary was produced with help from an AI and may contain inaccuracies - check out the links to read the original source documents!

Related Papers

13

LLM in a flash: Efficient Large Language Model Inference with Limited Memory

Keivan Alizadeh, Iman Mirzadeh, Dmitry Belenko, Karen Khatamifard, Minsik Cho, Carlo C Del Mundo, Mohammad Rastegari, Mehrdad Farajtabar

Large language models (LLMs) are central to modern natural language processing, delivering exceptional performance in various tasks. However, their substantial computational and memory requirements present challenges, especially for devices with limited DRAM capacity. This paper tackles the challenge of efficiently running LLMs that exceed the available DRAM capacity by storing the model parameters in flash memory, but bringing them on demand to DRAM. Our method involves constructing an inference cost model that takes into account the characteristics of flash memory, guiding us to optimize in two critical areas: reducing the volume of data transferred from flash and reading data in larger, more contiguous chunks. Within this hardware-informed framework, we introduce two principal techniques. First, windowing strategically reduces data transfer by reusing previously activated neurons, and second, row-column bundling, tailored to the sequential data access strengths of flash memory, increases the size of data chunks read from flash memory. These methods collectively enable running models up to twice the size of the available DRAM, with a 4-5x and 20-25x increase in inference speed compared to naive loading approaches in CPU and GPU, respectively. Our integration of sparsity awareness, context-adaptive loading, and a hardware-oriented design paves the way for effective inference of LLMs on devices with limited memory.

Read more8/1/2024

0

A Survey on Efficient Inference for Large Language Models

Zixuan Zhou, Xuefei Ning, Ke Hong, Tianyu Fu, Jiaming Xu, Shiyao Li, Yuming Lou, Luning Wang, Zhihang Yuan, Xiuhong Li, Shengen Yan, Guohao Dai, Xiao-Ping Zhang, Yuhan Dong, Yu Wang

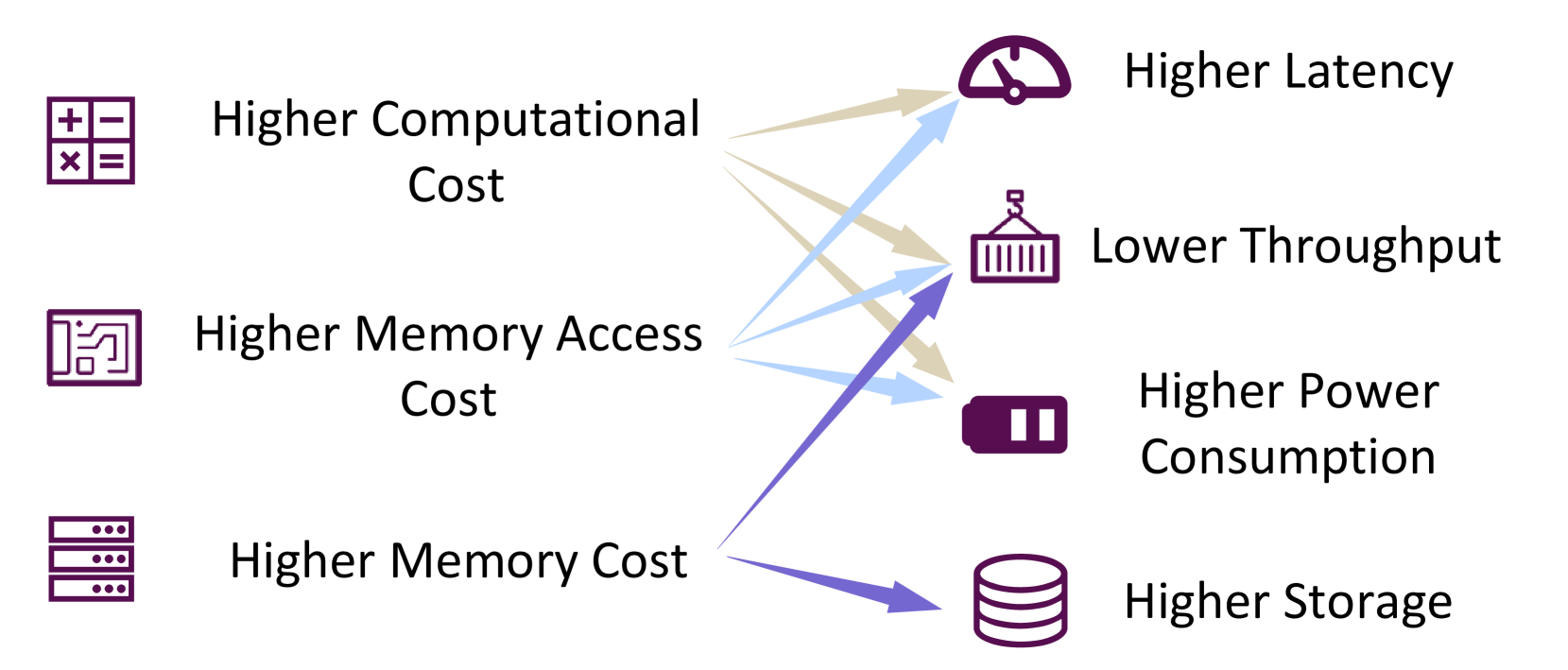

Large Language Models (LLMs) have attracted extensive attention due to their remarkable performance across various tasks. However, the substantial computational and memory requirements of LLM inference pose challenges for deployment in resource-constrained scenarios. Efforts within the field have been directed towards developing techniques aimed at enhancing the efficiency of LLM inference. This paper presents a comprehensive survey of the existing literature on efficient LLM inference. We start by analyzing the primary causes of the inefficient LLM inference, i.e., the large model size, the quadratic-complexity attention operation, and the auto-regressive decoding approach. Then, we introduce a comprehensive taxonomy that organizes the current literature into data-level, model-level, and system-level optimization. Moreover, the paper includes comparative experiments on representative methods within critical sub-fields to provide quantitative insights. Last but not least, we provide some knowledge summary and discuss future research directions.

Read more7/22/2024

0

New Solutions on LLM Acceleration, Optimization, and Application

Yingbing Huang, Lily Jiaxin Wan, Hanchen Ye, Manvi Jha, Jinghua Wang, Yuhong Li, Xiaofan Zhang, Deming Chen

Large Language Models (LLMs) have become extremely potent instruments with exceptional capacities for comprehending and producing human-like text in a wide range of applications. However, the increasing size and complexity of LLMs present significant challenges in both training and deployment, leading to substantial computational and storage costs as well as heightened energy consumption. In this paper, we provide a review of recent advancements and research directions aimed at addressing these challenges and enhancing the efficiency of LLM-based systems. We begin by discussing algorithm-level acceleration techniques focused on optimizing LLM inference speed and resource utilization. We also explore LLM-hardware co-design strategies with a vision to improve system efficiency by tailoring hardware architectures to LLM requirements. Further, we delve into LLM-to-accelerator compilation approaches, which involve customizing hardware accelerators for efficient LLM deployment. Finally, as a case study to leverage LLMs for assisting circuit design, we examine LLM-aided design methodologies for an important task: High-Level Synthesis (HLS) functional verification, by creating a new dataset that contains a large number of buggy and bug-free codes, which can be essential for training LLMs to specialize on HLS verification and debugging. For each aspect mentioned above, we begin with a detailed background study, followed by the presentation of several novel solutions proposed to overcome specific challenges. We then outline future research directions to drive further advancements. Through these efforts, we aim to pave the way for more efficient and scalable deployment of LLMs across a diverse range of applications.

Read more6/18/2024

0

Memory Is All You Need: An Overview of Compute-in-Memory Architectures for Accelerating Large Language Model Inference

Christopher Wolters, Xiaoxuan Yang, Ulf Schlichtmann, Toyotaro Suzumura

Large language models (LLMs) have recently transformed natural language processing, enabling machines to generate human-like text and engage in meaningful conversations. This development necessitates speed, efficiency, and accessibility in LLM inference as the computational and memory requirements of these systems grow exponentially. Meanwhile, advancements in computing and memory capabilities are lagging behind, exacerbated by the discontinuation of Moore's law. With LLMs exceeding the capacity of single GPUs, they require complex, expert-level configurations for parallel processing. Memory accesses become significantly more expensive than computation, posing a challenge for efficient scaling, known as the memory wall. Here, compute-in-memory (CIM) technologies offer a promising solution for accelerating AI inference by directly performing analog computations in memory, potentially reducing latency and power consumption. By closely integrating memory and compute elements, CIM eliminates the von Neumann bottleneck, reducing data movement and improving energy efficiency. This survey paper provides an overview and analysis of transformer-based models, reviewing various CIM architectures and exploring how they can address the imminent challenges of modern AI computing systems. We discuss transformer-related operators and their hardware acceleration schemes and highlight challenges, trends, and insights in corresponding CIM designs.

Read more6/13/2024