SySMOL: Co-designing Algorithms and Hardware for Neural Networks with Heterogeneous Precisions

0

Sign in to get full access

Overview

- This paper introduces SySMOL, a hardware-software co-design framework for building ultra-low and fine-grained mixed-precision neural networks.

- The goal is to enable highly efficient neural network inference on resource-constrained devices by leveraging mixed-precision computation and customized hardware.

- The framework encompasses neural network model design, mixed-precision quantization, and hardware acceleration.

Plain English Explanation

The researchers behind this paper have developed a tool called SySMOL that helps create neural network models that are extremely efficient and can run on devices with limited computing power, like smartphones or embedded systems.

The key idea is to use a mix of different data precisions (e.g. some parts of the model use 8-bit numbers, others use 4-bit numbers) to reduce the overall computational and memory requirements of the model. This "mixed-precision" approach allows the model to maintain high accuracy while being much more compact and faster to run.

SySMOL automates the process of designing these mixed-precision neural networks. It takes a standard neural network model as input, and then intelligently decides which parts of the model should use lower precision data types based on the model's structure and the hardware constraints. The framework also includes custom hardware designs that can efficiently execute the mixed-precision computations.

The end result is neural network models that are significantly smaller and more power-efficient, making them well-suited for deployment on resource-constrained devices like phones, IoT sensors, or edge computing hardware. This unlocks new possibilities for deploying advanced AI capabilities on a wide range of devices.

Technical Explanation

The paper first provides background on CPU SIMD (single instruction, multiple data) architectures and how they can be leveraged for efficient neural network inference. It also discusses prior work on mixed-precision neural networks and hardware-aware quantization techniques.

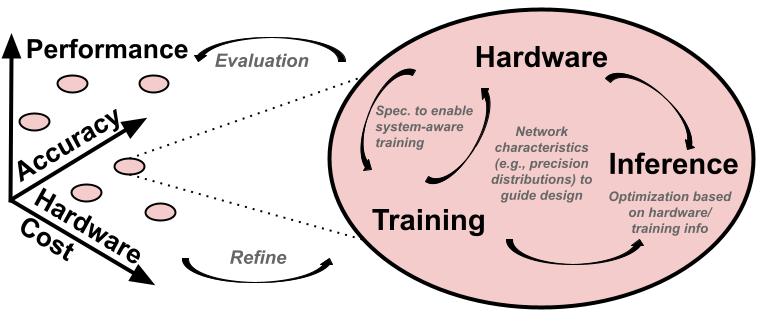

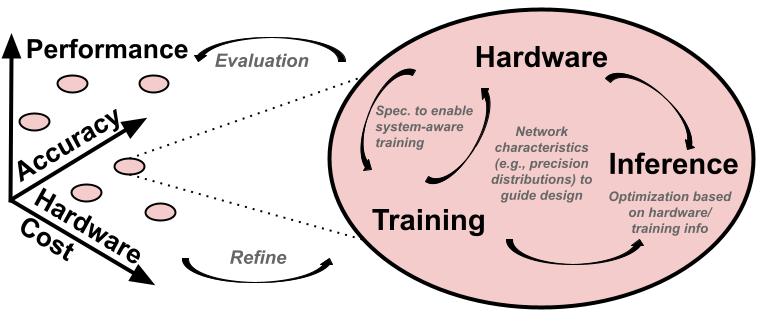

The core of the SySMOL framework comprises three main components:

-

Mixed-Precision Neural Network Design: SySMOL employs a quantization-aware training approach to determine the optimal bit-widths for different layers and parameters of the neural network. This allows for fine-grained control over the precision used throughout the model.

-

Hardware Acceleration: SySMOL includes a custom hardware accelerator design that can efficiently execute the mixed-precision computations. It leverages CPU SIMD instructions and other hardware-specific optimizations to maximize performance and energy efficiency.

-

Hardware-Software Co-Design: The framework tightly integrates the neural network design and the hardware accelerator, enabling end-to-end optimization. This hardware-software co-design approach ensures that the neural network model is well-suited for the target hardware platform.

The paper evaluates SySMOL on several computer vision tasks and demonstrates significant improvements in model size, inference latency, and energy consumption compared to baseline approaches. For example, on the ImageNet classification task, SySMOL achieves a 4.1× reduction in model size and a 4.3× improvement in energy efficiency over a full-precision baseline.

Critical Analysis

The paper provides a comprehensive solution for building highly efficient neural networks tailored for resource-constrained devices. The mixed-precision approach and hardware-software co-design are well-justified and the experimental results are compelling.

However, the paper does not explore the generalization of the SySMOL framework to other domains beyond computer vision, such as natural language processing or speech recognition. It would be interesting to see how the framework performs on a wider range of tasks and datasets.

Additionally, the paper does not provide much insight into the tradeoffs involved in the mixed-precision design process. For example, it would be useful to understand the sensitivity of the model's accuracy to the choice of bit-widths for different layers, or the computational overhead of the co-design process.

Overall, the SySMOL framework presents a promising approach for enabling advanced AI capabilities on edge devices, and the paper lays a solid foundation for further research and development in this area.

Conclusion

The SySMOL framework introduced in this paper offers a compelling solution for building ultra-low and fine-grained mixed-precision neural networks that can run efficiently on resource-constrained hardware. By tightly integrating neural network design, quantization, and custom hardware acceleration, the framework enables significant improvements in model size, latency, and energy consumption.

This work has the potential to unlock new opportunities for deploying advanced AI models on a wide range of edge devices, from smartphones to IoT sensors. As mobile and embedded computing continues to play an increasingly important role in our daily lives, efficient AI solutions like SySMOL will become increasingly crucial for unlocking the full potential of ubiquitous computing.

This summary was produced with help from an AI and may contain inaccuracies - check out the links to read the original source documents!

Related Papers

0

SySMOL: Co-designing Algorithms and Hardware for Neural Networks with Heterogeneous Precisions

Cyrus Zhou, Pedro Savarese, Vaughn Richard, Zack Hassman, Xin Yuan, Michael Maire, Michael DiBrino, Yanjing Li

Recent quantization techniques have enabled heterogeneous precisions at very fine granularity, e.g., each parameter/activation can take on a different precision, resulting in compact neural networks without sacrificing accuracy. However, there is a lack of efficient architectural support for such networks, which require additional hardware to decode the precision settings for individual variables, align the variables, and provide fine-grained mixed-precision compute capabilities. The complexity of these operations introduces high overheads. Thus, the improvements in inference latency/energy of these networks are not commensurate with the compression ratio, and may be inferior to larger quantized networks with uniform precisions. We present an end-to-end co-design approach encompassing computer architecture, training algorithm, and inference optimization to efficiently execute networks with fine-grained heterogeneous precisions. The key to our approach is a novel training algorithm designed to accommodate hardware constraints and inference operation requirements, outputting networks with input-channel-wise heterogeneous precisions and at most three precision levels. Combined with inference optimization techniques, existing architectures with low-cost enhancements can support such networks efficiently, yielding optimized tradeoffs between accuracy, compression ratio and inference latency/energy. We demonstrate the efficacy of our approach across CPU and GPU architectures. For various representative neural networks, our approach achieves >10x improvements in both compression ratio and inference latency, with negligible degradation in accuracy compared to full-precision networks.

Read more5/8/2024

🧠

0

On-Chip Hardware-Aware Quantization for Mixed Precision Neural Networks

Wei Huang, Haotong Qin, Yangdong Liu, Jingzhuo Liang, Yulun Zhang, Ying Li, Xianglong Liu

Low-bit quantization emerges as one of the most promising compression approaches for deploying deep neural networks on edge devices. Mixed-precision quantization leverages a mixture of bit-widths to unleash the accuracy and efficiency potential of quantized models. However, existing mixed-precision quantization methods rely on simulations in high-performance devices to achieve accuracy and efficiency trade-offs in immense search spaces. This leads to a non-negligible gap between the estimated efficiency metrics and the actual hardware that makes quantized models far away from the optimal accuracy and efficiency, and also causes the quantization process to rely on additional high-performance devices. In this paper, we propose an On-Chip Hardware-Aware Quantization (OHQ) framework, performing hardware-aware mixed-precision quantization on deployed edge devices to achieve accurate and efficient computing. Specifically, for efficiency metrics, we built an On-Chip Quantization Aware pipeline, which allows the quantization process to perceive the actual hardware efficiency of the quantization operator and avoid optimization errors caused by inaccurate simulation. For accuracy metrics, we propose Mask-Guided Quantization Estimation technology to effectively estimate the accuracy impact of operators in the on-chip scenario, getting rid of the dependence of the quantization process on high computing power. By synthesizing insights from quantized models and hardware through linear optimization, we can obtain optimized bit-width configurations to achieve outstanding performance on accuracy and efficiency. We evaluate inference accuracy and acceleration with quantization for various architectures and compression ratios on hardware. OHQ achieves 70% and 73% accuracy for ResNet-18 and MobileNetV3, respectively, and can reduce latency by 15~30% compared to INT8 on real deployment.

Read more5/24/2024

0

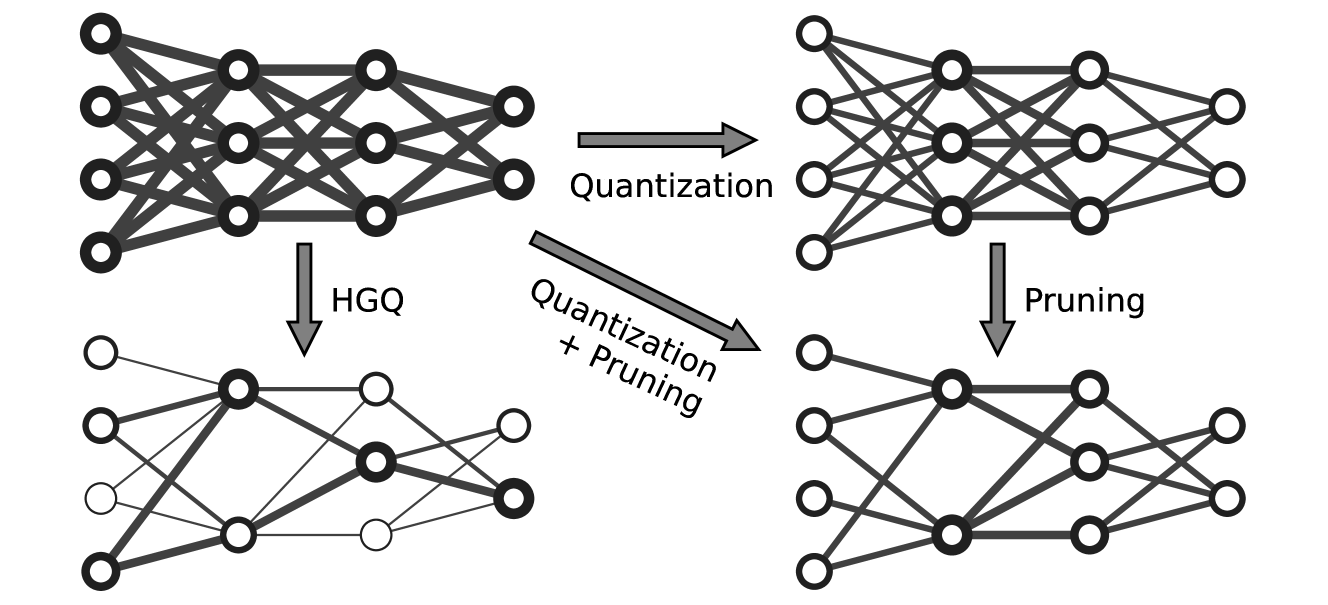

Gradient-based Automatic Per-Weight Mixed Precision Quantization for Neural Networks On-Chip

Chang Sun, Thea K. {AA}rrestad, Vladimir Loncar, Jennifer Ngadiuba, Maria Spiropulu

Model size and inference speed at deployment time, are major challenges in many deep learning applications. A promising strategy to overcome these challenges is quantization. However, a straightforward uniform quantization to very low precision can result in significant accuracy loss. Mixed-precision quantization, based on the idea that certain parts of the network can accommodate lower precision without compromising performance compared to other parts, offers a potential solution. In this work, we present High Granularity Quantization (HGQ), an innovative quantization-aware training method that could fine-tune the per-weight and per-activation precision by making them optimizable through gradient descent. This approach enables ultra-low latency and low power neural networks on hardware capable of performing arithmetic operations with an arbitrary number of bits, such as FPGAs and ASICs. We demonstrate that HGQ can outperform existing methods by a substantial margin, achieving resource reduction by up to a factor of 20 and latency improvement by a factor of 5 while preserving accuracy.

Read more8/12/2024

0

Joint Pruning and Channel-wise Mixed-Precision Quantization for Efficient Deep Neural Networks

Beatrice Alessandra Motetti, Matteo Risso, Alessio Burrello, Enrico Macii, Massimo Poncino, Daniele Jahier Pagliari

The resource requirements of deep neural networks (DNNs) pose significant challenges to their deployment on edge devices. Common approaches to address this issue are pruning and mixed-precision quantization, which lead to latency and memory occupation improvements. These optimization techniques are usually applied independently. We propose a novel methodology to apply them jointly via a lightweight gradient-based search, and in a hardware-aware manner, greatly reducing the time required to generate Pareto-optimal DNNs in terms of accuracy versus cost (i.e., latency or memory). We test our approach on three edge-relevant benchmarks, namely CIFAR-10, Google Speech Commands, and Tiny ImageNet. When targeting the optimization of the memory footprint, we are able to achieve a size reduction of 47.50% and 69.54% at iso-accuracy with the baseline networks with all weights quantized at 8 and 2-bit, respectively. Our method surpasses a previous state-of-the-art approach with up to 56.17% size reduction at iso-accuracy. With respect to the sequential application of state-of-the-art pruning and mixed-precision optimizations, we obtain comparable or superior results, but with a significantly lowered training time. In addition, we show how well-tailored cost models can improve the cost versus accuracy trade-offs when targeting specific hardware for deployment.

Read more7/2/2024