Towards A Flexible Accuracy-Oriented Deep Learning Module Inference Latency Prediction Framework for Adaptive Optimization Algorithms

0

Sign in to get full access

Overview

- This paper presents a framework for predicting the inference latency of deep learning modules, which can be used to adaptively optimize algorithms for deep learning inference.

- The proposed framework leverages machine learning models to predict the inference latency of different deep learning modules, allowing for more efficient deployment and optimization of deep learning systems.

- The framework is designed to be flexible and accurate, enabling it to be applied to a variety of deep learning models and deployment scenarios.

Plain English Explanation

The paper describes a new way to predict how long it will take for a deep learning model to make a prediction, which is called the "inference latency." This is important because deep learning models are used in many applications, and the speed of these predictions can be critical. For example, in self-driving cars, fast predictions are needed to respond quickly to changing road conditions.

The authors of this paper have developed a framework that uses machine learning to predict the inference latency of different deep learning models. This allows the system to adaptively optimize the deep learning algorithms to ensure they run as quickly as possible, while still maintaining high accuracy. For example, the framework could be used to dynamically adjust the deployment of deep neural networks based on the available compute resources.

The key innovation of this framework is that it is designed to be flexible and accurate, meaning it can be applied to a wide range of deep learning models and scenarios. This allows it to be used in a variety of applications, from edge computing to large language models.

Technical Explanation

The proposed framework consists of two main components: a latency prediction model and an adaptive optimization algorithm.

The latency prediction model is a machine learning model that takes in characteristics of a deep learning module, such as its architecture and input size, and outputs a prediction of its inference latency. This model is trained on a dataset of deep learning modules and their observed latency measurements.

The adaptive optimization algorithm then uses the latency predictions to dynamically adjust the deployment of the deep learning modules. For example, it could allocate more computational resources to modules with longer predicted latency, or modify the module architecture to reduce latency.

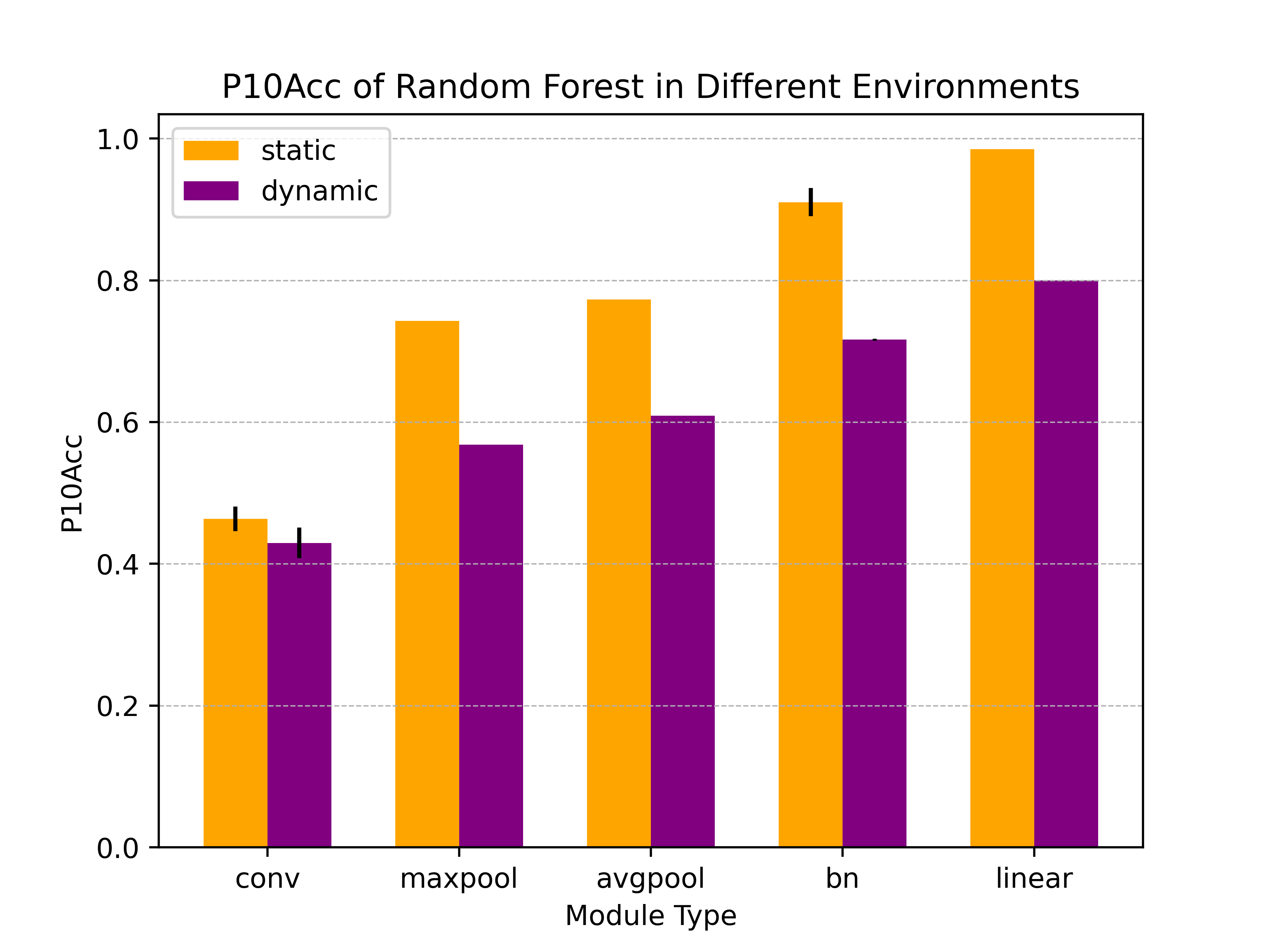

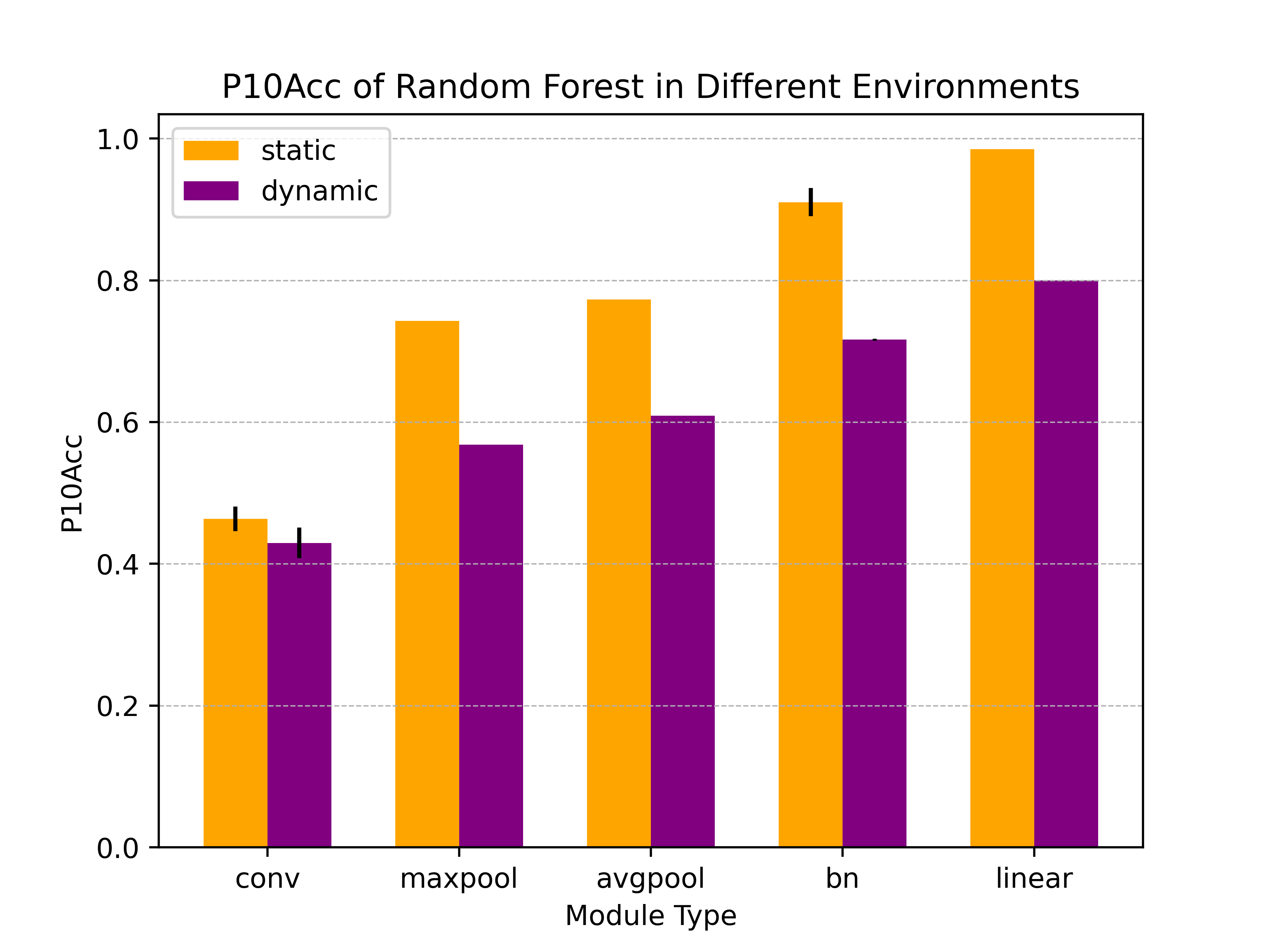

The authors evaluate their framework on several deep learning models and deployment scenarios, including image classification, object detection, and language modeling tasks. They show that the latency prediction model can achieve high accuracy, with low mean absolute error in the latency predictions.

Furthermore, the authors demonstrate that the adaptive optimization algorithm can significantly improve the overall inference latency of the deep learning system, without sacrificing accuracy, when compared to static deployment strategies.

Critical Analysis

One limitation of the proposed framework is that it relies on having a representative dataset of deep learning modules and their observed latency measurements. In practice, collecting such a dataset may be challenging, especially for emerging deep learning architectures or deployment scenarios.

Additionally, the latency prediction model may not generalize well to novel deep learning modules or hardware platforms that are not well-represented in the training data. Further research is needed to explore techniques for improving the robustness and generalization of the latency prediction model.

Another potential issue is the computational overhead of running the latency prediction model and adaptive optimization algorithm. These components add additional processing time and may not be suitable for real-time, low-latency applications where every millisecond counts. The authors could explore ways to optimize the efficiency of these components or investigate alternative approaches that can provide low-latency predictions.

Despite these limitations, the overall concept of the proposed framework is promising and could have significant implications for the deployment and optimization of deep learning systems, especially in resource-constrained environments.

Conclusion

This paper presents a flexible and accurate framework for predicting the inference latency of deep learning modules, which can be used to adaptively optimize deep learning algorithms for improved performance. The framework's ability to accurately predict latency and dynamically adjust deployment strategies has the potential to enhance the efficiency and real-world applicability of deep learning systems, particularly in scenarios where low-latency inference is critical.

While the framework has some limitations, the authors' work represents an important step forward in the ongoing research to optimize the deployment of deep learning models across a wide range of applications and deployment scenarios.

This summary was produced with help from an AI and may contain inaccuracies - check out the links to read the original source documents!

Related Papers

0

Towards A Flexible Accuracy-Oriented Deep Learning Module Inference Latency Prediction Framework for Adaptive Optimization Algorithms

Jingran Shen, Nikos Tziritas, Georgios Theodoropoulos

With the rapid development of Deep Learning, more and more applications on the cloud and edge tend to utilize large DNN (Deep Neural Network) models for improved task execution efficiency as well as decision-making quality. Due to memory constraints, models are commonly optimized using compression, pruning, and partitioning algorithms to become deployable onto resource-constrained devices. As the conditions in the computational platform change dynamically, the deployed optimization algorithms should accordingly adapt their solutions. To perform frequent evaluations of these solutions in a timely fashion, RMs (Regression Models) are commonly trained to predict the relevant solution quality metrics, such as the resulted DNN module inference latency, which is the focus of this paper. Existing prediction frameworks specify different RM training workflows, but none of them allow flexible configurations of the input parameters (e.g., batch size, device utilization rate) and of the selected RMs for different modules. In this paper, a deep learning module inference latency prediction framework is proposed, which i) hosts a set of customizable input parameters to train multiple different RMs per DNN module (e.g., convolutional layer) with self-generated datasets, and ii) automatically selects a set of trained RMs leading to the highest possible overall prediction accuracy, while keeping the prediction time / space consumption as low as possible. Furthermore, a new RM, namely MEDN (Multi-task Encoder-Decoder Network), is proposed as an alternative solution. Comprehensive experiment results show that MEDN is fast and lightweight, and capable of achieving the highest overall prediction accuracy and R-squared value. The Time/Space-efficient Auto-selection algorithm also manages to improve the overall accuracy by 2.5% and R-squared by 0.39%, compared to the MEDN single-selection scheme.

Read more7/2/2024

🤿

0

Automated Deep Neural Network Inference Partitioning for Distributed Embedded Systems

Fabian Kress, El Mahdi El Annabi, Tim Hotfilter, Julian Hoefer, Tanja Harbaum, Juergen Becker

Distributed systems can be found in various applications, e.g., in robotics or autonomous driving, to achieve higher flexibility and robustness. Thereby, data flow centric applications such as Deep Neural Network (DNN) inference benefit from partitioning the workload over multiple compute nodes in terms of performance and energy-efficiency. However, mapping large models on distributed embedded systems is a complex task, due to low latency and high throughput requirements combined with strict energy and memory constraints. In this paper, we present a novel approach for hardware-aware layer scheduling of DNN inference in distributed embedded systems. Therefore, our proposed framework uses a graph-based algorithm to automatically find beneficial partitioning points in a given DNN. Each of these is evaluated based on several essential system metrics such as accuracy and memory utilization, while considering the respective system constraints. We demonstrate our approach in terms of the impact of inference partitioning on various performance metrics of six different DNNs. As an example, we can achieve a 47.5 % throughput increase for EfficientNet-B0 inference partitioned onto two platforms while observing high energy-efficiency.

Read more7/1/2024

0

New!Automatic Generation of Fast and Accurate Performance Models for Deep Neural Network Accelerators

Konstantin Lubeck, Alexander Louis-Ferdinand Jung, Felix Wedlich, Mika Markus Muller, Federico Nicol'as Peccia, Felix Thommes, Jannik Steinmetz, Valentin Biermaier, Adrian Frischknecht, Paul Palomero Bernardo, Oliver Bringmann

Implementing Deep Neural Networks (DNNs) on resource-constrained edge devices is a challenging task that requires tailored hardware accelerator architectures and a clear understanding of their performance characteristics when executing the intended AI workload. To facilitate this, we present an automated generation approach for fast performance models to accurately estimate the latency of a DNN mapped onto systematically modeled and concisely described accelerator architectures. Using our accelerator architecture description method, we modeled representative DNN accelerators such as Gemmini, UltraTrail, Plasticine-derived, and a parameterizable systolic array. Together with DNN mappings for those modeled architectures, we perform a combined DNN/hardware dependency graph analysis, which enables us, in the best case, to evaluate only 154 loop kernel iterations to estimate the performance for 4.19 billion instructions achieving a significant speedup. We outperform regression and analytical models in terms of mean absolute percentage error (MAPE) compared to simulation results, while being several magnitudes faster than an RTL simulation.

Read more9/16/2024

0

Accelerate Intermittent Deep Inference

Ziliang Zhang

Emerging research in edge devices and micro-controller units (MCU) enables on-device computation of Deep Learning Training and Inferencing tasks. More recently, contemporary trends focus on making the Deep Neural Net (DNN) Models runnable on battery-less intermittent devices. One of the approaches is to shrink the DNN models by enabling weight sharing, pruning, and conducted Neural Architecture Search (NAS) with optimized search space to target specific edge devices cite{Cai2019OnceFA} cite{Lin2020MCUNetTD} cite{Lin2021MCUNetV2MP} cite{Lin2022OnDeviceTU}. Another approach analyzes the intermittent execution and designs the corresponding system by performing NAS that is aware of intermittent execution cycles and resource constraints cite{iNAS} cite{HW-NAS} cite{iLearn}. However, the optimized NAS was only considering consecutive execution with no power loss, and intermittent execution designs only focused on balancing data reuse and costs related to intermittent inference and often with low accuracy. We proposed Accelerated Intermittent Deep Inference to harness the power of optimized inferencing DNN models specifically targeting SRAM under 256KB and make it schedulable and runnable within intermittent power. Our main contribution is: (1) Schedule tasks performed by on-device inferencing into intermittent execution cycles and optimize for latency; (2) Develop a system that can satisfy the end-to-end latency while achieving a much higher accuracy compared to baseline cite{iNAS} cite{HW-NAS}

Read more7/23/2024