Towards Scalable Multi-Chip Wireless Networks with Near-Field Time Reversal

0

Sign in to get full access

Overview

- Explores the use of near-field time reversal to enable scalable multi-chip wireless networks

- Proposes a system that leverages near-field electromagnetic coupling between chips to enable high-bandwidth, low-power wireless interconnects

- Demonstrates the feasibility of this approach through simulations and prototype experiments

Plain English Explanation

This paper investigates a technology called near-field time reversal to build scalable wireless networks between computer chips. Typically, chips are connected using wires, which can be inefficient and limit the speed of data transfer. The researchers' idea is to use the natural electromagnetic fields around the chips to wirelessly transmit data between them instead.

The key innovation is the use of "time reversal," a technique that focuses the wireless signals very precisely on the receiving chip. This allows the wireless links to be highly directional and efficient, avoiding interference between different chip-to-chip connections. The near-field nature of the communications also helps to reduce power consumption compared to traditional wireless approaches.

By enabling these high-performance wireless interconnects, the researchers believe their approach could lead to more scalable and flexible computer architectures that are not constrained by the physical wiring between chips. This could unlock new possibilities for [advanced computing systems and Internet of Things devices.

Technical Explanation

The paper proposes a system for enabling scalable multi-chip wireless networks using near-field time reversal. Time reversal is a technique that focuses wireless signals by reversing the time evolution of the electromagnetic field. When applied in the near-field around chips, this allows for highly directional wireless links with low power consumption.

The key components of the system include:

- Transmitter and receiver circuits integrated directly on the chip to enable short-range near-field communication

- Algorithms for performing the time reversal signal processing to focus the wireless links

- Antenna designs optimized for the near-field coupling between chips

The researchers demonstrate the feasibility of their approach through a combination of electromagnetic simulations and prototype hardware experiments. They show that the near-field time reversal links can achieve Gbps data rates over millimeter-scale distances with only milliwatts of transmit power.

The authors also discuss the potential to integrate reconfigurable intelligent surfaces to dynamically steer and focus the wireless beams, further enhancing the scalability and flexibility of the multi-chip network.

Critical Analysis

The paper presents a promising approach for enabling scalable wireless interconnects between computer chips, addressing a significant challenge in modern computing architectures. The near-field time reversal technique appears to be an effective way to achieve high-performance wireless links with low power consumption.

However, the researchers acknowledge several practical challenges that would need to be addressed for real-world deployment. These include:

- Interference and crosstalk between the many wireless links in a dense multi-chip system

- Integrating the specialized transmitter and receiver circuits onto the chips without significantly increasing chip area or complexity

- Maintaining robust wireless connections in the presence of manufacturing variations, chip misalignment, and environmental changes

Overall, the research represents an important step towards more scalable and flexible computer architectures, but further development and testing would be needed to fully realize the potential of this approach.

Conclusion

This paper explores the use of near-field time reversal to enable high-performance wireless interconnects between computer chips, addressing a key challenge in modern computing systems. The proposed approach leverages the natural electromagnetic coupling between chips to achieve Gbps data rates with low power consumption.

The demonstrated feasibility of this technology through simulations and prototypes suggests it could unlock new possibilities for scalable and flexible multi-chip architectures, with applications ranging from advanced computing to pervasive Internet of Things devices. However, significant engineering challenges remain before real-world deployment, including managing interference, chip integration, and security considerations.

Overall, this research represents an important step towards more efficient and capable computing systems, with the potential to drive progress in a wide range of technology domains.

This summary was produced with help from an AI and may contain inaccuracies - check out the links to read the original source documents!

Related Papers

0

Towards Scalable Multi-Chip Wireless Networks with Near-Field Time Reversal

Ama Bandara, F'atima Rodr'iguez-Gal'an, Pau Talarn, Elana Pereira de Santana, Peter Haring Bol'ivar, Eduard Alarc'on, Sergi Abadal

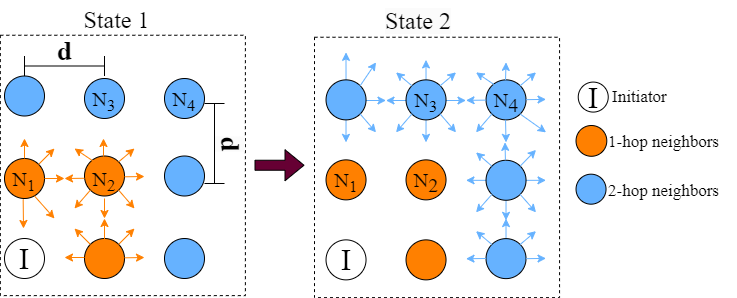

The concept of Wireless Network-on-Chip (WNoC) has emerged as a potential solution to address the escalating communication demands of modern computing systems due to their low-latency, versatility, and reconfigurability. However, for WNoC to fulfill its potential, it is essential to establish multiple high-speed wireless links across chips. Unfortunately, the compact and enclosed nature of computing packages introduces significant challenges in the form of Co-Channel Interference (CCI) and Inter-Symbol Interference (ISI), which not only hinder the deployment of multiple spatial channels but also severely restrict the symbol rate of each individual channel. In this paper, we posit that Time Reversal (TR) could be effective in addressing both impairments in this static scenario thanks to its spatiotemporal focusing capabilities even in the near field. Through comprehensive full-wave simulations and bit error rate analysis in multiple scenarios and at multiple frequency bands, we provide evidence that TR can increase the symbol rate by an order of magnitude, enabling the deployment of multiple concurrent links and achieving aggregate speeds exceeding 100 Gb/s. Finally, we evaluate the impact of reducing the sampling rate of the TR filter on the achievable speeds, paving the way to practical TR-based wireless communications at the chip scale.

Read more4/29/2024

0

A MAC Protocol with Time Reversal for Wireless Networks within Computing Packages

Ama Bandara, Abhijit Das, F'atima Rodr'iguez-Gal'an, Eduard Alarc'on, Sergi Abadal

Wireless Network-on-Chip (WNoC) is a promising concept which provides a solution to overcome the scalability issues in prevailing networks-in-package for many-core processors. However, the electromagnetic propagation inside the chip package leads to energy reverberation, resulting in Inter-Symbol Interference (ISI) with high delay spreads. Time Reversal (TR) is a technique that benefits the unique time-invariant channel with rich multipath effects to focus the energy to the desired transceiver. TR mitigates both ISI and co-channel interference, hence providing parallel communications in both space and time. Thus, TR is a versatile candidate to improve the aggregate bandwidth of wireless on-chip networks provided that a Medium Access Control (MAC) is used to efficiently share the wireless medium. In this paper, we explore a simple yet resilient TR-based MAC protocol (TR-MAC) design for WNoC. We propose to manage multiple parallel transmissions with simultaneous spatial channels in the same time slot with TR precoding and focused energy detection at the transceiver. Our results show that TR-MAC can be employed in massive computing architectures with improved latency and throughput while matching with the stringent requirements of the physical layer.

Read more9/17/2024

0

Low-latency Symbol-Synchronous Communication for Multi-hop Sensor Networks

Xinlei Liu, Andrey Belogaev, Jonathan Oostvogels, Bingwu Fang, Danny Hughes, Maarten Weyn, Jeroen Famaey

Wireless sensor networks (WSNs) have received great interest due to their scalability, energy efficiency, and low-cost deployment. By utilizing multi-hop communication, WSNs can cover a wide area using low transmission power without the need for any communication infrastructure. Traditionally, WSNs rely on store-and-forward routing protocols and Time Division Multiple Access (TDMA)-based schedules that avoid interference between different wireless nodes. However, emerging challenging scenarios, such as the industrial Internet of Things (IoT) and robotic swarms, impose strict latency and reliability requirements, which traditional approaches cannot fulfill. In this paper, we propose a novel symbol-synchronous transmission design that provides reliable low-latency communication with a reasonable data rate on classical sub-6GHz RF frequency bands (e.g., the 2.4GHz ISM band). Instead of avoiding overlapping transmissions, the proposed scheme benefits from concurrent transmissions. Using simulation in MATLAB, we prove that the proposed design allows achieving a wire-like delay of 5ms for a 512-bit packet over multiple hops with only a 0.3% latency increase per extra hop and a low bit error rate (BER) of 0.04%. Compared to similar state-of-the-art approaches it can achieve a significantly higher data rate of 100kbps, which is expected to increase further with future improvements of the system.

Read more5/17/2024

🤿

0

Waveform Design for Over-the-Air Computing

Nikos G. Evgenidis, Nikos A. Mitsiou, Sotiris A. Tegos, Panagiotis D. Diamantoulakis, Panagiotis Sarigiannidis, Ioannis T. Rekanos, George K. Karagiannidis

In response to the increasing number of devices anticipated in next-generation networks, a shift toward over-the-air (OTA) computing has been proposed. Leveraging the superposition of multiple access channels, OTA computing enables efficient resource management by supporting simultaneous uncoded transmission in the time and the frequency domain. Thus, to advance the integration of OTA computing, our study presents a theoretical analysis addressing practical issues encountered in current digital communication transceivers, such as time sampling error and intersymbol interference (ISI). To this end, we examine the theoretical mean squared error (MSE) for OTA transmission under time sampling error and ISI, while also exploring methods for minimizing the MSE in the OTA transmission. Utilizing alternating optimization, we also derive optimal power policies for both the devices and the base station. Additionally, we propose a novel deep neural network (DNN)-based approach to design waveforms enhancing OTA transmission performance under time sampling error and ISI. To ensure fair comparison with existing waveforms like the raised cosine (RC) and the better-than-raised-cosine (BRTC), we incorporate a custom loss function integrating energy and bandwidth constraints, along with practical design considerations such as waveform symmetry. Simulation results validate our theoretical analysis and demonstrate performance gains of the designed pulse over RC and BTRC waveforms. To facilitate testing of our results without necessitating the DNN structure recreation, we provide curve fitting parameters for select DNN-based waveforms as well.

Read more6/3/2024