Fast ML-driven Analog Circuit Layout using Reinforcement Learning and Steiner Trees

0

Sign in to get full access

Overview

- This paper presents a reinforcement learning-based approach for fast and efficient analog circuit layout design.

- The method leverages Steiner trees to optimize the interconnections between circuit components.

- The researchers demonstrate the effectiveness of their technique on several benchmark analog circuit design problems.

Plain English Explanation

The design of analog circuits, such as those found in audio equipment or telecommunications devices, is a complex and time-consuming process. Analog circuit layout using reinforcement learning and Steiner trees aims to streamline this process by using a machine learning technique called reinforcement learning.

Reinforcement learning is a type of AI that learns by trial and error, similar to how a child might learn to play a game. In this case, the reinforcement learning algorithm is trained to optimize the layout of an analog circuit, including the placement of components and the routing of connections between them.

The key innovation in this paper is the use of Steiner trees, a mathematical concept from graph theory, to efficiently route the connections between circuit components. Steiner trees find the shortest possible paths that connect multiple points, which helps to minimize the amount of wiring required in the circuit layout.

By combining reinforcement learning and Steiner trees, the researchers were able to generate analog circuit layouts much more quickly than traditional methods, while still maintaining high levels of performance and efficiency. This could significantly reduce the time and effort required to design complex analog circuits, benefiting industries such as electronics, telecommunications, and audio engineering.

Technical Explanation

The paper presents a reinforcement learning-based approach for analog circuit layout design that leverages Steiner trees to optimize the interconnections between circuit components.

The researchers formulate the analog circuit layout problem as a Markov Decision Process (MDP), where the reinforcement learning agent learns to make a sequence of decisions to place and route the circuit components. At each step, the agent observes the current state of the circuit layout and takes an action, such as placing a component or adding a connection, to improve the overall design.

The key innovation in this work is the use of Steiner trees to efficiently route the connections between circuit components. Steiner trees are a graph theory concept that find the shortest possible paths to connect multiple points, which helps to minimize the amount of wiring required in the circuit layout.

The reinforcement learning agent is trained using a combination of model-free and model-based techniques, where the model-based approach utilizes the Steiner tree optimization to guide the agent's decision-making process. This hybrid approach allows the agent to learn efficient circuit layouts more quickly than using either technique alone.

The researchers evaluate their method on several benchmark analog circuit design problems and demonstrate significant improvements in layout quality and runtime compared to traditional design methods.

Critical Analysis

The paper's approach of using reinforcement learning and Steiner trees for analog circuit layout is a promising step forward in the field of electronic design automation. The use of Steiner trees to optimize interconnections is a clever application of graph theory concepts to a real-world engineering problem.

However, the paper does not address some potential limitations of the method. For example, the reinforcement learning agent may struggle to generalize its learned policies to completely new circuit topologies or design constraints. Additionally, the computational complexity of the Steiner tree optimization could become a bottleneck for very large or dense circuit designs.

Further research could explore ways to improve the generalization capabilities of the reinforcement learning agent, such as through the use of transfer learning or meta-learning techniques. Investigating the scalability of the Steiner tree optimization, perhaps by developing approximate or heuristic methods, could also help to make the approach more widely applicable.

Overall, this paper represents a significant advancement in the use of machine learning for analog circuit design, and the authors' insights could have far-reaching implications for the electronics industry and beyond.

Conclusion

This paper introduces a reinforcement learning-based approach for fast and efficient analog circuit layout design that leverages Steiner trees to optimize the interconnections between circuit components. The researchers demonstrate the effectiveness of their technique on several benchmark problems, showing significant improvements in layout quality and runtime compared to traditional design methods.

The use of reinforcement learning and Steiner trees represents a novel and promising direction in the field of electronic design automation, with the potential to streamline the analog circuit design process and enable the development of more complex and capable electronic systems. While the paper highlights some impressive results, further research is needed to address potential limitations and expand the applicability of the approach to a wider range of circuit designs and use cases.

Overall, this work contributes important insights and techniques that could have far-reaching implications for industries such as electronics, telecommunications, and audio engineering, ultimately driving innovation and progress in these vital technological domains.

This summary was produced with help from an AI and may contain inaccuracies - check out the links to read the original source documents!

Related Papers

0

Fast ML-driven Analog Circuit Layout using Reinforcement Learning and Steiner Trees

Davide Basso, Luca Bortolussi, Mirjana Videnovic-Misic, Husni Habal

This paper presents an artificial intelligence driven methodology to reduce the bottleneck often encountered in the analog ICs layout phase. We frame the floorplanning problem as a Markov Decision Process and leverage reinforcement learning for automatic placement generation under established topological constraints. Consequently, we introduce Steiner tree-based methods for the global routing step and generate guiding paths to be used to connect every circuit block. Finally, by integrating these solutions into a procedural generation framework, we present a unified pipeline that bridges the divide between circuit design and verification steps. Experimental results demonstrate the efficacy in generating complete layouts, eventually reducing runtimes to 1.5% compared to manual efforts.

Read more5/28/2024

0

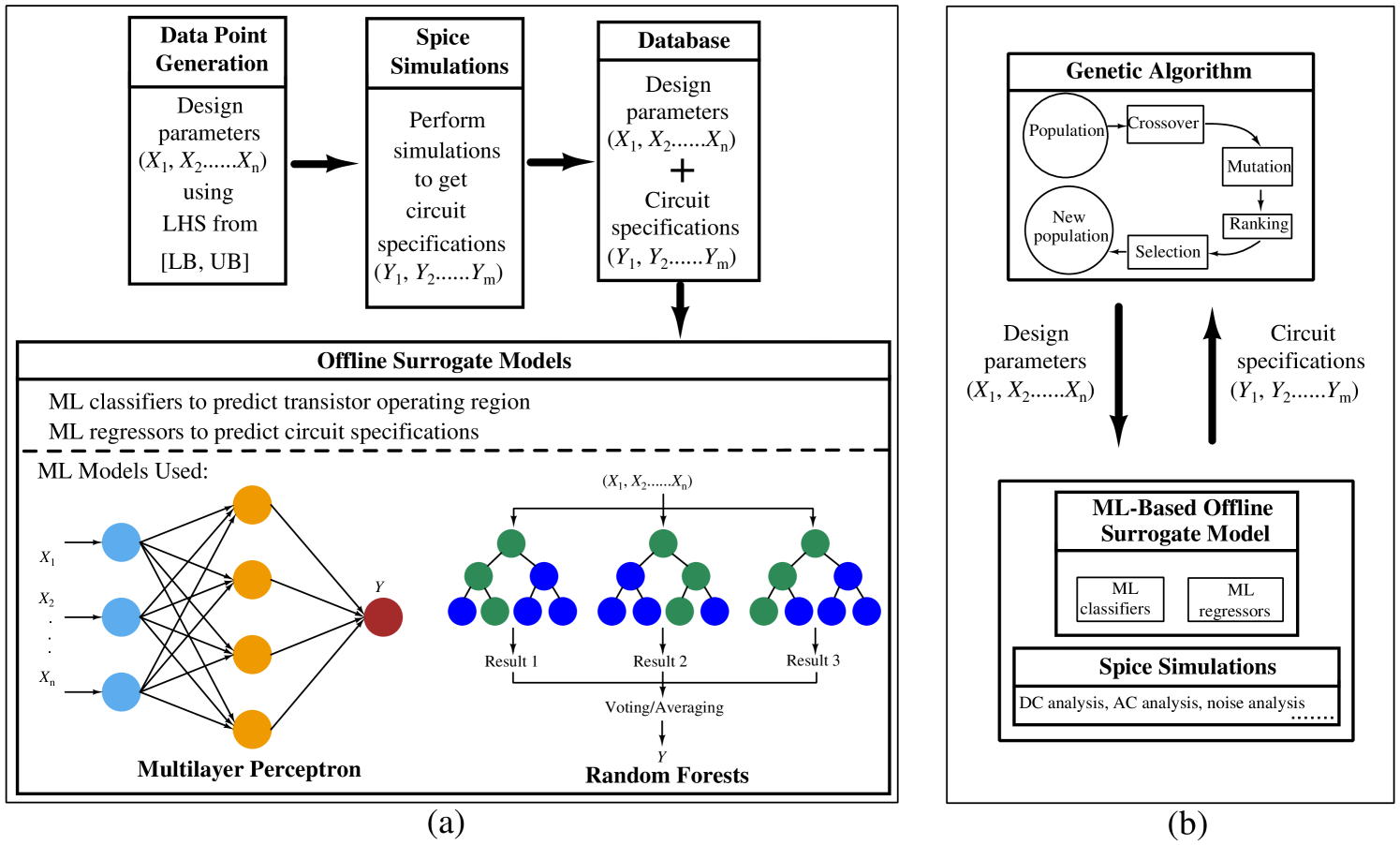

Machine Learning Driven Global Optimisation Framework for Analog Circuit Design

Ria Rashid, Komala Krishna, Clint Pazhayidam George, Nandakumar Nambath

We propose a machine learning-driven optimisation framework for analog circuit design in this paper. The primary objective is to determine the device sizes for the optimal performance of analog circuits for a given set of specifications. Our methodology entails employing machine learning models and spice simulations to direct the optimisation algorithm towards achieving the optimal design for analog circuits. Machine learning based global offline surrogate models, with the circuit design parameters as the input, are built in the design space for the analog circuits under study and is used to guide the optimisation algorithm, resulting in faster convergence and a reduced number of spice simulations. Multi-layer perceptron and random forest regressors are employed to predict the required design specifications of the analog circuit. Since the saturation condition of transistors is vital in the proper working of analog circuits, multi-layer perceptron classifiers are used to predict the saturation condition of each transistor in the circuit. The feasibility of the candidate solutions is verified using machine learning models before invoking spice simulations. We validate the proposed framework using three circuit topologies--a bandgap reference, a folded cascode operational amplifier, and a two-stage operational amplifier. The simulation results show better optimum values and lower standard deviations for fitness functions after convergence. Incorporating the machine learning-based predictions proposed in the optimisation method has resulted in the reduction of spice calls by 56%, 59%, and 83% when compared with standard approaches in the three test cases considered in the study.

Read more4/5/2024

0

Automated Design and Optimization of Distributed Filtering Circuits via Reinforcement Learning

Peng Gao, Tao Yu, Fei Wang, Ru-Yue Yuan

Designing distributed filter circuits (DFCs) is complex and time-consuming, involving setting and optimizing multiple hyperparameters. Traditional optimization methods, such as using the commercial finite element solver HFSS (High-Frequency Structure Simulator) to enumerate all parameter combinations with fixed steps and then simulate each combination, are not only time-consuming and labor-intensive but also rely heavily on the expertise and experience of electronics engineers, making it difficult to adapt to rapidly changing design requirements. Additionally, these commercial tools struggle with precise adjustments when parameters are sensitive to numerical changes, resulting in limited optimization effectiveness. This study proposes a novel end-to-end automated method for DFC design. The proposed method harnesses reinforcement learning (RL) algorithms, eliminating the dependence on the design experience of engineers. Thus, it significantly reduces the subjectivity and constraints associated with circuit design. The experimental findings demonstrate clear improvements in design efficiency and quality when comparing the proposed method with traditional engineer-driven methods. Furthermore, the proposed method achieves superior performance when designing complex or rapidly evolving DFCs, highlighting the substantial potential of RL in circuit design automation. In particular, compared to the existing DFC automation design method CircuitGNN, our method achieves an average performance improvement of 8.72%. Additionally, the execution efficiency of our method is 2000 times higher than CircuitGNN on the CPU and 241 times higher on the GPU.

Read more7/30/2024

1

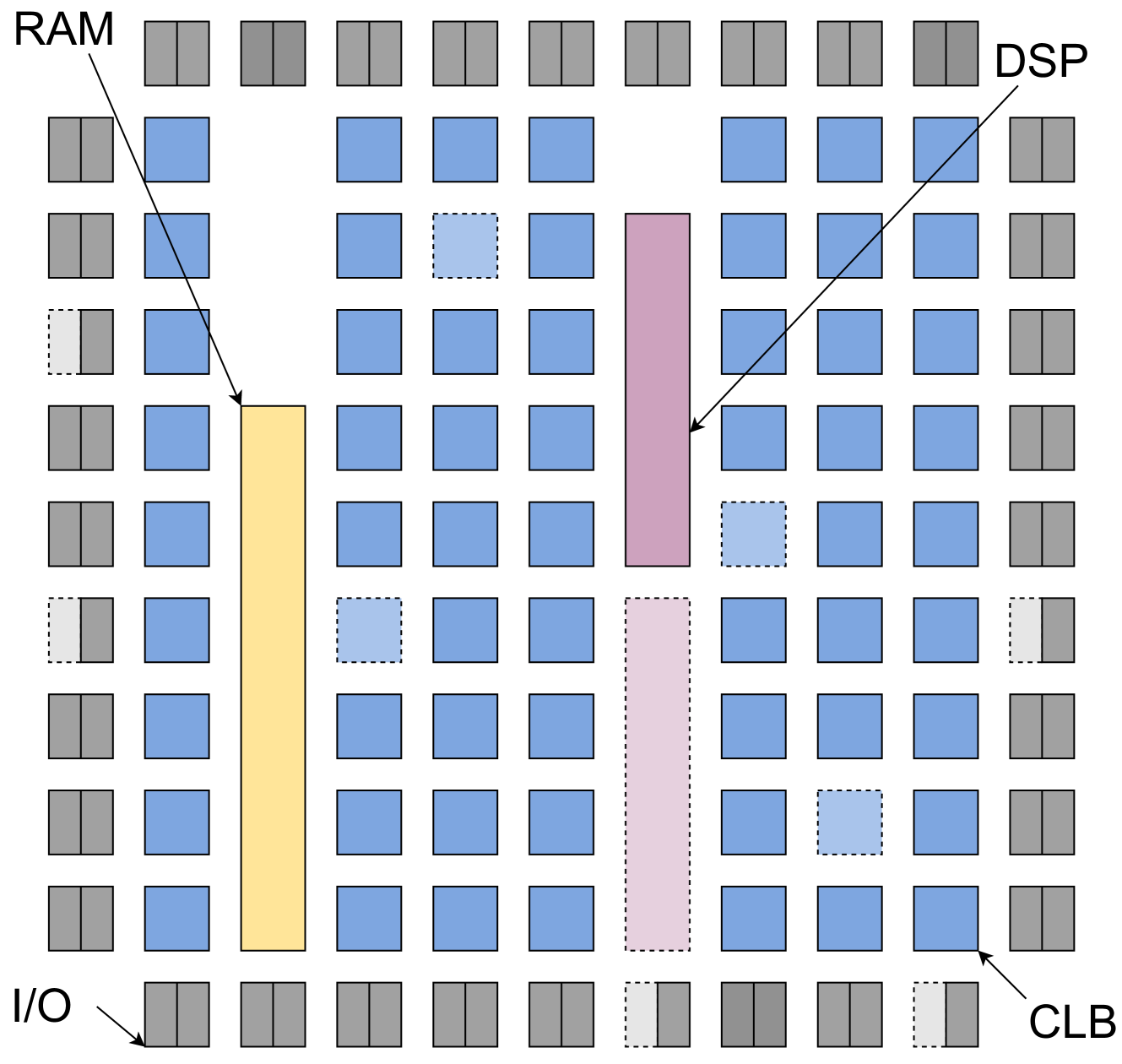

FPGA Divide-and-Conquer Placement using Deep Reinforcement Learning

Shang Wang, Deepak Ranganatha Sastry Mamillapalli, Tianpei Yang, Matthew E. Taylor

This paper introduces the problem of learning to place logic blocks in Field-Programmable Gate Arrays (FPGAs) and a learning-based method. In contrast to previous search-based placement algorithms, we instead employ Reinforcement Learning (RL) with the goal of minimizing wirelength. In addition to our preliminary learning results, we also evaluated a novel decomposition to address the nature of large search space when placing many blocks on a chipboard. Empirical experiments evaluate the effectiveness of the learning and decomposition paradigms on FPGA placement tasks.

Read more4/23/2024