HG-PIPE: Vision Transformer Acceleration with Hybrid-Grained Pipeline

0

Sign in to get full access

Overview

- HG-PIPE is a new pipeline architecture for accelerating Vision Transformers (ViT) on FPGA hardware.

- It uses a "hybrid-grained" pipeline design that combines coarse-grained and fine-grained parallelism to achieve high efficiency.

- The authors demonstrate significant performance and energy improvements over existing ViT accelerators on FPGA.

Plain English Explanation

The paper introduces HG-PIPE, a new way to speed up a type of AI model called a Vision Transformer (ViT) when running on specialized hardware called FPGAs.

ViTs are a popular type of AI model used for computer vision tasks like image classification. However, running ViTs efficiently on FPGAs has been challenging. HG-PIPE addresses this by using a "hybrid-grained pipeline" design. This combines two different approaches to parallelism - coarse-grained and fine-grained - to achieve high performance and energy efficiency.

The key idea is to divide the ViT computation into different stages and process them in parallel, using both coarse-level parallelism (across different ViT layers) and fine-level parallelism (within each layer). This hybrid approach allows HG-PIPE to maximize the utilization of the FPGA hardware resources.

Technical Explanation

The paper proposes a new pipeline architecture called HG-PIPE (Hybrid-Grained Pipeline) to accelerate Vision Transformers (ViTs) on FPGA hardware.

At a high level, HG-PIPE uses a hybrid-grained pipeline design that combines coarse-grained and fine-grained parallelism. The coarse-grained parallelism occurs at the ViT layer-level, where different layers are processed concurrently. The fine-grained parallelism happens within each ViT layer, where the computations are further divided and processed in parallel.

This hybrid approach allows HG-PIPE to efficiently utilize the FPGA's resources and achieve high performance and energy efficiency. The authors demonstrate that HG-PIPE outperforms existing ViT accelerators on FPGA in terms of throughput, latency, and energy consumption.

Specifically, the HG-PIPE architecture consists of multiple processing elements (PEs) that operate in a pipelined fashion. The input sequence is split and fed into the PEs, which execute the ViT layers in parallel. Within each PE, the computations are further parallelized using a fine-grained scheme.

The authors also propose novel techniques to address challenges like data reuse, load balancing, and communication overhead in the hybrid-grained pipeline. These optimizations play a key role in realizing the performance benefits of HG-PIPE.

Critical Analysis

The paper presents a well-designed and thoroughly evaluated HG-PIPE architecture for accelerating ViTs on FPGAs. The hybrid-grained pipeline approach is a novel and promising solution to address the efficiency challenges of running ViTs on specialized hardware.

One potential limitation mentioned in the paper is the need for careful tuning of the pipeline parameters (e.g., the number of PEs, degree of parallelism) to achieve optimal performance for different ViT models and hardware configurations. This may require additional design effort and could limit the generalizability of HG-PIPE.

Additionally, the paper does not provide a comprehensive comparison to other recently proposed ViT accelerators, such as QUASAR-ViT, Peano-ViT, or GCV-Turbo. A more extensive benchmarking against these state-of-the-art approaches could further strengthen the claims about HG-PIPE's advantages.

It would also be interesting to see how HG-PIPE's performance and energy efficiency scale with larger and more complex ViT models, as well as its applicability to other transformer-based architectures beyond computer vision tasks.

Conclusion

The HG-PIPE architecture presented in this paper offers a novel and effective solution for accelerating Vision Transformers on FPGA hardware. The hybrid-grained pipeline design, which combines coarse-grained and fine-grained parallelism, demonstrates significant improvements in throughput, latency, and energy consumption compared to existing ViT accelerators.

This work represents an important advancement in the field of efficient ViT inference on specialized hardware, and the techniques employed in HG-PIPE could potentially be applied to other transformer-based models as well. The paper provides a solid foundation for further research and optimization in this area, which could lead to even more powerful and energy-efficient ViT accelerators in the future.

This summary was produced with help from an AI and may contain inaccuracies - check out the links to read the original source documents!

Related Papers

0

HG-PIPE: Vision Transformer Acceleration with Hybrid-Grained Pipeline

Qingyu Guo, Jiayong Wan, Songqiang Xu, Meng Li, Yuan Wang

Vision Transformer (ViT) acceleration with field programmable gate array (FPGA) is promising but challenging. Existing FPGA-based ViT accelerators mainly rely on temporal architectures, which process different operators by reusing the same hardware blocks and suffer from extensive memory access overhead. Pipelined architectures, either coarse-grained or fine-grained, unroll the ViT computation spatially for memory access efficiency. However, they usually suffer from significant hardware resource constraints and pipeline bubbles induced by the global computation dependency of ViT. In this paper, we introduce HG-PIPE, a pipelined FPGA accelerator for high-throughput and low-latency ViT processing. HG-PIPE features a hybrid-grained pipeline architecture to reduce on-chip buffer cost and couples the computation dataflow and parallelism design to eliminate the pipeline bubbles. HG-PIPE further introduces careful approximations to implement both linear and non-linear operators with abundant Lookup Tables (LUTs), thus alleviating resource constraints. On a ZCU102 FPGA, HG-PIPE achieves 2.78 times better throughput and 2.52 times better resource efficiency than the prior-art accelerators, e.g., AutoViTAcc. With a VCK190 FPGA, HG-PIPE realizes end-to-end ViT acceleration on a single device and achieves 7118 images/s, which is 2.81 times faster than a V100 GPU.

Read more8/2/2024

0

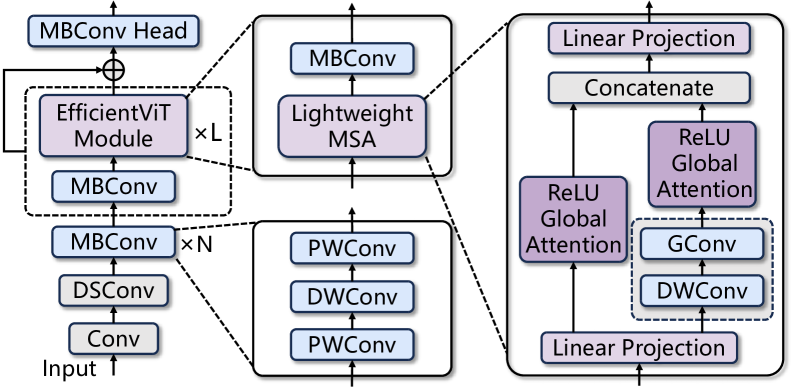

An FPGA-Based Reconfigurable Accelerator for Convolution-Transformer Hybrid EfficientViT

Haikuo Shao, Huihong Shi, Wendong Mao, Zhongfeng Wang

Vision Transformers (ViTs) have achieved significant success in computer vision. However, their intensive computations and massive memory footprint challenge ViTs' deployment on embedded devices, calling for efficient ViTs. Among them, EfficientViT, the state-of-the-art one, features a Convolution-Transformer hybrid architecture, enhancing both accuracy and hardware efficiency. Unfortunately, existing accelerators cannot fully exploit the hardware benefits of EfficientViT due to its unique architecture. In this paper, we propose an FPGA-based accelerator for EfficientViT to advance the hardware efficiency frontier of ViTs. Specifically, we design a reconfigurable architecture to efficiently support various operation types, including lightweight convolutions and attention, boosting hardware utilization. Additionally, we present a time-multiplexed and pipelined dataflow to facilitate both intra- and inter-layer fusions, reducing off-chip data access costs. Experimental results show that our accelerator achieves up to 780.2 GOPS in throughput and 105.1 GOPS/W in energy efficiency at 200MHz on the Xilinx ZCU102 FPGA, which significantly outperforms prior works.

Read more4/1/2024

0

H2PIPE: High throughput CNN Inference on FPGAs with High-Bandwidth Memory

Mario Doumet, Marius Stan, Mathew Hall, Vaughn Betz

Convolutional Neural Networks (CNNs) combine large amounts of parallelizable computation with frequent memory access. Field Programmable Gate Arrays (FPGAs) can achieve low latency and high throughput CNN inference by implementing dataflow accelerators that pipeline layer-specific hardware to implement an entire network. By implementing a different processing element for each CNN layer, these layer-pipelined accelerators can achieve high compute density, but having all layers processing in parallel requires high memory bandwidth. Traditionally this has been satisfied by storing all weights on chip, but this is infeasible for the largest CNNs, which are often those most in need of acceleration. In this work we augment a state-of-the-art dataflow accelerator (HPIPE) to leverage both High-Bandwidth Memory (HBM) and on-chip storage, enabling high performance layer-pipelined dataflow acceleration of large CNNs. Based on profiling results of HBM's latency and throughput against expected address patterns, we develop an algorithm to choose which weight buffers should be moved off chip and how deep the on-chip FIFOs to HBM should be to minimize compute unit stalling. We integrate the new hardware generation within the HPIPE domain-specific CNN compiler and demonstrate good bandwidth efficiency against theoretical limits. Compared to the best prior work we obtain speed-ups of at least 19.4x, 5.1x and 10.5x on ResNet-18, ResNet-50 and VGG-16 respectively.

Read more8/20/2024

0

CHOSEN: Compilation to Hardware Optimization Stack for Efficient Vision Transformer Inference

Mohammad Erfan Sadeghi, Arash Fayyazi, Suhas Somashekar, Massoud Pedram

Vision Transformers (ViTs) represent a groundbreaking shift in machine learning approaches to computer vision. Unlike traditional approaches, ViTs employ the self-attention mechanism, which has been widely used in natural language processing, to analyze image patches. Despite their advantages in modeling visual tasks, deploying ViTs on hardware platforms, notably Field-Programmable Gate Arrays (FPGAs), introduces considerable challenges. These challenges stem primarily from the non-linear calculations and high computational and memory demands of ViTs. This paper introduces CHOSEN, a software-hardware co-design framework to address these challenges and offer an automated framework for ViT deployment on the FPGAs in order to maximize performance. Our framework is built upon three fundamental contributions: multi-kernel design to maximize the bandwidth, mainly targeting benefits of multi DDR memory banks, approximate non-linear functions that exhibit minimal accuracy degradation, and efficient use of available logic blocks on the FPGA, and efficient compiler to maximize the performance and memory-efficiency of the computing kernels by presenting a novel algorithm for design space exploration to find optimal hardware configuration that achieves optimal throughput and latency. Compared to the state-of-the-art ViT accelerators, CHOSEN achieves a 1.5x and 1.42x improvement in the throughput on the DeiT-S and DeiT-B models.

Read more7/26/2024