Stencil Computations on AMD and Nvidia Graphics Processors: Performance and Tuning Strategies

2

🚀

Sign in to get full access

Overview

- The paper evaluates the performance and energy efficiency of stencil computations on modern datacenter graphics processors from AMD and Nvidia.

- Stencil computations are a type of data-parallel task that are widely used in high-performance computing, including machine learning and computational sciences.

- The authors propose a tuning strategy for fusing cache-heavy stencil kernels to improve performance and energy efficiency.

- The study covers both synthetic and practical applications involving linear and nonlinear stencil functions in one to three dimensions.

- The findings reveal key differences between AMD and Nvidia graphics processors, highlighting the need for platform-specific tuning to reach their full computational potential.

Plain English Explanation

Graphics processors have become a popular choice for accelerating data-parallel tasks, which are common in fields like machine learning and scientific computing. These tasks involve performing the same operation on multiple pieces of data at the same time.

In this study, the researchers looked at a specific type of data-parallel task called stencil computations. Stencil computations involve updating the value of a point based on the values of its neighboring points. This is used in a variety of applications, such as simulating the flow of fluids or processing images.

The researchers evaluated the performance and energy efficiency of stencil computations on two types of modern graphics processors: those made by AMD and those made by Nvidia. They also proposed a way to combine multiple stencil computations to improve performance.

The researchers found that the AMD and Nvidia graphics processors had some key differences in how they work, both in the hardware and the software. This means that the best way to get the most out of these processors can vary depending on which one you're using. The researchers suggest that it's important to customize your approach for the specific type of graphics processor you're working with.

Technical Explanation

The paper evaluates the performance and energy efficiency of stencil computations on modern datacenter graphics processors from AMD and Nvidia. Stencil computations are a type of data-parallel task that involve updating the value of a point based on the values of its neighboring points. These computations are widely used in various branches of high-performance computing, including machine learning and computational sciences.

The authors propose a tuning strategy for fusing cache-heavy stencil kernels to improve performance and energy efficiency. The study covers both synthetic and practical applications, involving the evaluation of linear and nonlinear stencil functions in one to three dimensions.

The experimental results reveal key differences between AMD and Nvidia graphics processors in terms of both hardware and software. These differences necessitate platform-specific tuning to reach the full computational potential of the respective architectures. The authors' findings highlight the importance of customizing optimization strategies for the target hardware when working with data-parallel tasks such as stencil computations.

Critical Analysis

The paper provides a comprehensive evaluation of stencil computations on modern datacenter graphics processors, but it acknowledges some limitations and areas for further research. For example, the study focuses on a specific set of stencil kernels and does not explore the impact of more complex memory access patterns or the integration of stencil computations with other types of workloads.

Additionally, the paper does not delve into the underlying reasons for the observed performance differences between AMD and Nvidia graphics processors. A deeper analysis of the architectural features and software stack differences between the two platforms could provide more insights and guide future hardware and software co-design efforts.

While the proposed tuning strategy for fusing cache-heavy stencil kernels demonstrates promising results, it would be valuable to investigate the generalizability of this approach to a broader range of stencil computations and application scenarios. Exploring the trade-offs between performance, energy efficiency, and programming complexity could also help determine the practical applicability of the technique.

Conclusion

This study highlights the importance of platform-specific tuning for achieving optimal performance and energy efficiency in data-parallel tasks like stencil computations on modern graphics processors. The findings suggest that the differences between AMD and Nvidia graphics processors require customized optimization strategies to fully harness the computational capabilities of each architecture.

The insights gained from this research can inform the design and development of future hardware and software systems for high-performance computing, helping to bridge the gap between theoretical peak performance and realized application-level efficiency. By understanding the unique characteristics of emerging accelerator technologies, researchers and engineers can create more efficient and robust solutions for a wide range of data-intensive applications.

This summary was produced with help from an AI and may contain inaccuracies - check out the links to read the original source documents!

Related Papers

🚀

2

Stencil Computations on AMD and Nvidia Graphics Processors: Performance and Tuning Strategies

Johannes Pekkila, Oskar Lappi, Fredrik Roberts'en, Maarit J. Korpi-Lagg

Over the last ten years, graphics processors have become the de facto accelerator for data-parallel tasks in various branches of high-performance computing, including machine learning and computational sciences. However, with the recent introduction of AMD-manufactured graphics processors to the world's fastest supercomputers, tuning strategies established for previous hardware generations must be re-evaluated. In this study, we evaluate the performance and energy efficiency of stencil computations on modern datacenter graphics processors, and propose a tuning strategy for fusing cache-heavy stencil kernels. The studied cases comprise both synthetic and practical applications, which involve the evaluation of linear and nonlinear stencil functions in one to three dimensions. Our experiments reveal that AMD and Nvidia graphics processors exhibit key differences in both hardware and software, necessitating platform-specific tuning to reach their full computational potential.

Read more6/14/2024

0

Evaluation of Programming Models and Performance for Stencil Computation on Current GPU Architectures

Baodi Shan, Mauricio Araya-Polo

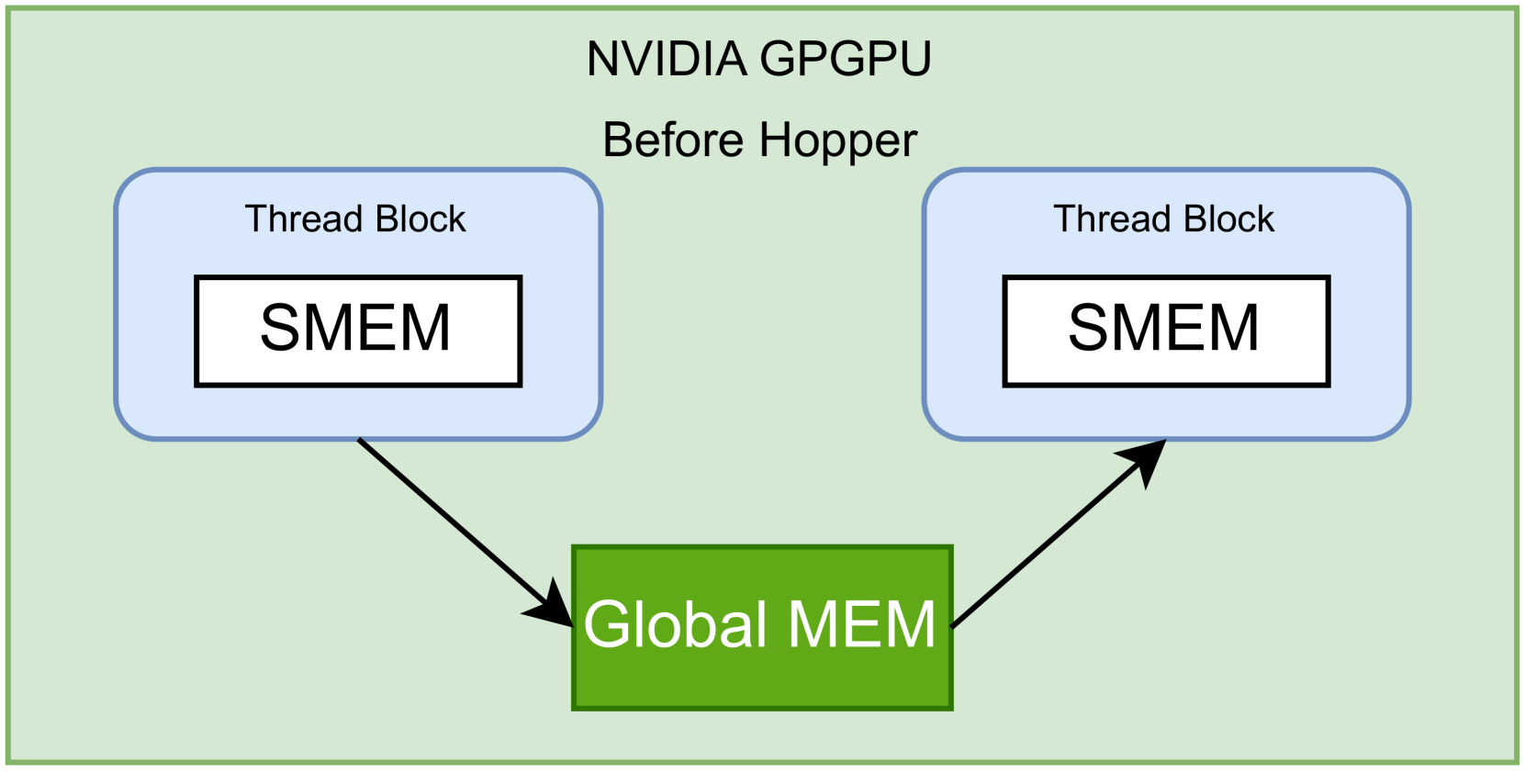

Accelerated computing is widely used in high-performance computing. Therefore, it is crucial to experiment and discover how to better utilize GPUGPUs latest generations on relevant applications. In this paper, we present results and share insights about highly tuned stencil-based kernels for NVIDIA Ampere (A100) and Hopper (GH200) architectures. Performance results yield useful insights into the behavior of this type of algorithms for these new accelerators. This knowledge can be leveraged by many scientific applications which involve stencils computations. Further, evaluation of three different programming models: CUDA, OpenACC, and OpenMP target offloading is conducted on aforementioned accelerators. We extensively study the performance and portability of various kernels under each programming model and provide corresponding optimization recommendations. Furthermore, we compare the performance of different programming models on the mentioned architectures. Up to 58% performance improvement was achieved against the previous GPGPU's architecture generation for an highly optimized kernel of the same class, and up to 42% for all classes. In terms of programming models, and keeping portability in mind, optimized OpenACC implementation outperforms OpenMP implementation by 33%. If portability is not a factor, our best tuned CUDA implementation outperforms the optimized OpenACC one by 2.1x.

Read more8/13/2024

🤷

0

A Portable Framework for Accelerating Stencil Computations on Modern Node Architectures

Ryuichi Sai, John Mellor-Crummey, Jinfan Xu, Mauricio Araya-Polo

Finite-difference methods based on high-order stencils are widely used in seismic simulations, weather forecasting, computational fluid dynamics, and other scientific applications. Achieving HPC-level stencil computations on one architecture is challenging, porting to other architectures without sacrificing performance requires significant effort, especially in this golden age of many distinctive architectures. To help developers achieve performance, portability, and productivity with stencil computations, we developed StencilPy. With StencilPy, developers write stencil computations in a high-level domain-specific language, which promotes productivity, while its backends generate efficient code for existing and emerging architectures, including modern many-core CPUs (such as AMD Genoa-X, Fujitsu A64FX, and Intel Sapphire Rapids), latest generations of GPUs (including NVIDIA H100 and A100, AMD MI200, and Intel Ponte Vecchio), and accelerators (including Cerebras and STX). StencilPy demonstrates promising performance results on par with hand-written code, maintains cross-architectural performance portability, and enhances productivity. Its modular design enables easy configuration, customization, and extension. A 25-point star-shaped stencil written in StencilPy is one-quarter of the length of a hand-crafted CUDA code and achieves similar performance on an NVIDIA H100 GPU. In addition, the same kernel written using our tool is 7x shorter than hand-optimized code written in Cerebras Software Language (CSL), and it delivers comparable performance that code on a Cerebras CS-2.

Read more7/9/2024

7

Bringing Auto-tuning to HIP: Analysis of Tuning Impact and Difficulty on AMD and Nvidia GPUs

Milo Lurati, Stijn Heldens, Alessio Sclocco, Ben van Werkhoven

Many studies have focused on developing and improving auto-tuning algorithms for Nvidia Graphics Processing Units (GPUs), but the effectiveness and efficiency of these approaches on AMD devices have hardly been studied. This paper aims to address this gap by introducing an auto-tuner for AMD's HIP. We do so by extending Kernel Tuner, an open-source Python library for auto-tuning GPU programs. We analyze the performance impact and tuning difficulty for four highly-tunable benchmark kernels on four different GPUs: two from Nvidia and two from AMD. Our results demonstrate that auto-tuning has a significantly higher impact on performance on AMD compared to Nvidia (10x vs 2x). Additionally, we show that applications tuned for Nvidia do not perform optimally on AMD, underscoring the importance of auto-tuning specifically for AMD to achieve high performance on these GPUs.

Read more7/17/2024